每個 Cortex-A9 處理器都有自己的私有 32 位定時器和 32 位看門狗定時器,兩個處理器共享一個全局 64 位定時器,這些定時器始終以 CPU 頻率 (CPU_3x2x) 的 1/2 計時。

在系統層面,有一個 24 位看門狗定時器和兩個 16 位三重定時器/計數器。

系統看門狗定時器的時鐘頻率為 CPU 頻率 (CPU_1x) 的 1/4 或 1/6,或者可以由來自 MIO 引腳或來自 PL 的外部信號提供時鐘。

兩個三重定時器/計數器始終以 CPU 頻率 (CPU_1x) 的 1/4 或 1/6 計時,用于計算來自 MIO 引腳或來自 PL 的信號脈沖的寬度。

下圖顯示了系統定時器的關系

本文重點說一下全局定時器。

全局定時器

全局定時器是一個 64 位的具有自動遞增功能的遞增計數器。

全局定時器是內存映射到與私有定時器相同的地址空間。

所有 Cortex-A9 處理器都可以訪問全局定時器。

每個 Cortex-A9 處理器都有一個 64 位比較器,用于在全局定時器達到比較器值時聲明一個私有中斷。

計時

GTC 始終以 CPU 頻率 (CPU_3x2x) 的 1/2 計時。

寄存器概述

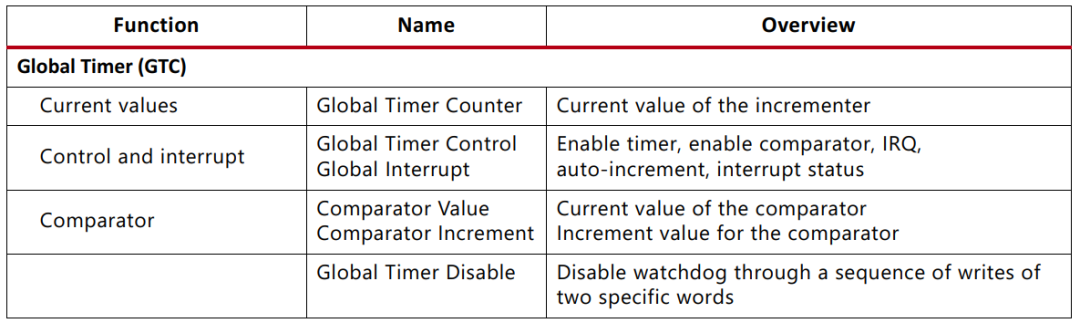

有關GTC的注冊概述如下表

全局定時器寄存器概述

怎么使用?

下面兩個函數是在bsp standalone中的xtime_l.c中。

void XTime_SetTime(XTime Xtime_Global)

{

/* Disable Global Timer */

Xil_Out32((u32)GLOBAL_TMR_BASEADDR +(u32)GTIMER_CONTROL_OFFSET, (u32)0x0);

/* Updating Global Timer Counter Register */

Xil_Out32((u32)GLOBAL_TMR_BASEADDR +(u32)GTIMER_COUNTER_LOWER_OFFSET, (u32)Xtime_Global);

Xil_Out32((u32)GLOBAL_TMR_BASEADDR +(u32)GTIMER_COUNTER_UPPER_OFFSET,

(u32)((u32)(Xtime_Global》》32U)));

/* Enable Global Timer */

Xil_Out32((u32)GLOBAL_TMR_BASEADDR + (u32)GTIMER_CONTROL_OFFSET, (u32)0x1);

}

void XTime_GetTime(XTime *Xtime_Global)

{

u32 low;

u32 high;

/* Reading Global Timer Counter Register */

do

{

high = Xil_In32(GLOBAL_TMR_BASEADDR + GTIMER_COUNTER_UPPER_OFFSET);

low = Xil_In32(GLOBAL_TMR_BASEADDR + GTIMER_COUNTER_LOWER_OFFSET);

} while(Xil_In32(GLOBAL_TMR_BASEADDR + GTIMER_COUNTER_UPPER_OFFSET) != high);

*Xtime_Global = (((XTime) high) 《《 32U) | (XTime) low;

}

官方已經把全局定時器自動初始化好了,其頻率為CPU頻率的一半。

定義全局定時器的7個寄存器全部按照地址進行了宏定義,采用xil_io.h里的out32和in32兩個函數進行讀寫操作:

#define Global_Timer_INTR XPAR_GLOBAL_TMR_INTR#define Global_Timer_Counter_Register0 XPAR_GLOBAL_TMR_BASEADDR+0x0U#define Global_Timer_Counter_Register1 XPAR_GLOBAL_TMR_BASEADDR+0x4U#define Global_Timer_Control_Register XPAR_GLOBAL_TMR_BASEADDR+0x8U#define Global_Timer_Interrupt_Status_Register XPAR_GLOBAL_TMR_BASEADDR+0xCU#define Comparator_Value_Register0 XPAR_GLOBAL_TMR_BASEADDR+0x10U#define Comparator_Value_Register1 XPAR_GLOBAL_TMR_BASEADDR+0x14U#define Auto_increment_Register XPAR_GLOBAL_TMR_BASEADDR+0x18U

接下來進行全局定時器的初始化和中斷函數綁定:

GT_Write_Reg(Global_Timer_Control_Register,0);//停止全局定時器

GT_Write_Reg(Global_Timer_Counter_Register0,0);//清空計數器低32位

GT_Write_Reg(Global_Timer_Counter_Register1,0);//清空計數器高32位

GT_Write_Reg(Global_Timer_Interrupt_Status_Register,1);//清除中斷標志位

GT_Write_Reg(Comparator_Value_Register0,TIMER_LOAD_VALUE);//加載比較器低32位

GT_Write_Reg(Comparator_Value_Register1,0);//加載比較器高32位

GT_Write_Reg(Auto_increment_Register,TIMER_LOAD_VALUE);//加載遞增寄存器數值

Status = XScuGic_Connect(IntcInstancePtr, Global_Timer_INTR,

(Xil_ExceptionHandler)TimerIntrHandler,

0);//綁定全局定時器中斷服務函數

if (Status != XST_SUCCESS)

{

return Status;

}

XScuGic_InterruptMaptoCpu(IntcInstancePtr,1,Global_Timer_INTR);//將27號全局定時器中斷映射到CPU1

XScuGic_Enable(IntcInstancePtr, Global_Timer_INTR);//打開全局定時器中斷(27號)

主程序中打開全局定時器開始計時

GT_Write_Reg(Global_Timer_Control_Register,//啟動全局定時器

Auto_Increment_Bit|IRQ_Enable_Bit|Comp_Enable_Bit|Timer_Enable_Bit);

總結

全局定時器一共7個寄存器,打開SDK再想看看對應的BSP文檔時就會發現還是很復雜的。

編輯:jq

-

處理器

+關注

關注

68文章

19535瀏覽量

231859 -

寄存器

+關注

關注

31文章

5390瀏覽量

121901 -

cpu

+關注

關注

68文章

10947瀏覽量

213900 -

計數器

+關注

關注

32文章

2278瀏覽量

95422 -

定時器

+關注

關注

23文章

3259瀏覽量

115892

原文標題:Zynq-7000系列全局定時器(GT)詳解

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

dac3174與xilinx zynq7000系列連接,fpga的案例參考代碼有沒有?

當ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

zynq7000 BSP無法在u-boot加載運行怎么解決?

正點原子ZYNQ7015開發板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強悍,資料豐富!

[XILINX] 正點原子ZYNQ7035/7045/7100開發板發布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

定時器的工作方式介紹

簡談Xilinx Zynq-7000嵌入式系統設計與實現

Xilinx ZYNQ 動手實操演練

如何實現一個軟件定時器?

Zynq-7000為何不是FPGA?

簡談Xilinx Zynq-7000嵌入式系統設計與實現

?PLC定時器介紹

剖析Zynq-7000系列全局定時器(GT)

剖析Zynq-7000系列全局定時器(GT)

評論