1. 前言

在光纖通信系統中,作為終端設備的光端機必須由光發射模塊、光接收模塊、數據接口、用戶線接口和數字復接芯片等幾部分組成。其中的數字復接芯片用來將若干個低速數字信號合并成一個高速數字信號,以達到擴大傳輸容量和提高傳輸速率的目的。

目前,數字復接體制主要有準同步數字體系(Parasynchronous Digital Hierarchy,簡稱PDH)和同步數字體系(Synchronous Digital Hierarchy,簡稱SDH),從長遠看,SDH終將取代PDH。但由于PDH復接系統信道利用率高,設備簡單,因此,在一些小規模、小容量的通信網中,仍具有廣泛的市場和應用價值。因此,研究數字復接專用芯片在PDH體制中的應用亦具有一定的意義。

PDH復接體制包括一次群到二次群復接、二次群到三次群復接、一次群到三次群跳群復接和三次群到四次群復接等 。其中,最后一種復接方式已轉化為三次群到SDH STM-1的復接。本文不予討論。

2. 各種數字復接芯片比較

為了滿足上述各種復接方式的需要,市場上出現了各種型號的數字復接專用集成芯片。這些芯片以格林威的GW

7600、GW7620、GW7680,正有的ZYIC-002,華大的CISCG和清華的MXZW68231為典型。在眾多的芯片中,怎樣選擇滿足科研設計需要的、性價比最高的復接芯片呢?表1是上述各芯片的比較。

根據表1,為滿足不同的復接要求,在保證高性價比的前提下,分不同情況給出幾種說明:

(1)一次群至二次群復分接

選CISCG芯片最便宜,但外圍電路中要有2M平滑鎖相、2M和8M時鐘提取電路;選擇GW7600和ZYIC-002在性價比及外圍電路上幾乎一樣,只是后者功耗大一點,但它帶有插座,有利于科研設計時的插拔。

(2)二次群至三次群復分接

選CISCG芯片時,外圍電路中要有8M平滑鎖相、8M和34M時鐘提取電路;選GW7600和ZYIC-002時,外圍電路中要有8M平滑鎖相和34M時鐘提取電路。

(3)一次群至三次群復分接(帶標準34M電接口)

若其中要留8M電接口,則用2片GW7620和1片GW7600或ZYIC-002,外加8M平滑鎖相和34M時鐘提取電路;若其中不留8M電接口,則用1片MXZW68231外加34M時鐘提取電路即可。

(4)一次群至三次群跳群復分接

最佳方案選GW7680,它有線路編碼電路,具有E1支路16×16交叉連接功能,方便上下電路。

3. 復接芯片的應用舉例

就目前市場的需求來看,中小容量用戶需求的是2M口且具有相當于480路容量的光傳輸出設備,而不一定是標準34M口;另外,用戶對網絡的靈活性(比如上下電路、交叉連接功能)、可靠性要求都比較高。正因為如此,認為GW7680芯片的應用開發價值較大。下面就GW7680芯片的功能、特點及應用情況作一具體介紹。

3.1 GW7680芯片的功能結構及特點

GW7680芯片是北京格林威為實現其APDH(Advanced PDH)光纖傳輸方案而設計的ASIC芯片。該芯片采用數字鎖相環技術和線路編碼技術實現E1信號(2.048kbit/s)準同步復用和E2信號(8.448kbit/s)同步復用以及光線路傳輸編解碼。GW7680吸收SDH的特點是單片可提供16個E1信號直接上下電路、E1信號通道層(通道速率為2112 kbit/s)交叉連接、E1雙纖環網通道保護、線路再定時及豐富的開銷。其功能結構如圖1所示。

在圖1中,RA和TB單元構成西側光口,RB和TA構成東側光口。TA和TB實現的功能是同步復用,以插入碼方式成幀、擾碼;RA和RB實現的功能是:解擾碼、幀同步定位、同步分接。每個基本單元的線路口速率為42.24Mbit/s。

E1 MAPPER完成16個2.048kbit/s速率信號的復接和分接,其輸入輸出構成GW7680的第三個端口(即電口)。在每個E1的輸入口設有一個全數字的時鐘恢復電路,輸出口設有一個全數字的鎖相環,這兩個模塊的性能決定了2.048kbit/s通道的抖動特征,由于采用全數字化技術進行處理,所以抖動性能非常穩定可靠且不受工作電壓和環境溫度的影響。

數字交叉連接器DXC作為E1通道的控制樞紐,對來自三個方向的信號進行調度。西向進入的E1可以再從東向發出或往E1連接器選擇一個物理口下電路,東向進入的E1可以再從西向發出或往E1連接器選擇一個物理口下電路。從某個物理口插入的E1信號可在DXC控制下發往西向或東向,或雙向同時發送。

除以上功能外,GW7680還具有如下功能特點:

●線路速率在42.24 Mbit/s(480路)和84.48 Mbit/s(960路)兩者之一任選 。選42.24 Mbit/s時,只需一對光收發模塊,適合于點到點的傳輸場合;選84.48 Mbit/s時,需兩對光收發模塊,具有交叉連接功能,在組網應用時非常方便;

●提供兩路64kbit/s數字公務電話接口,可直接連接話音CODEC(編解碼芯片,如MC145503),且具備公務電話四音(撥號、回鈴、忙音、催掛)插入控制,該接口不占用2M通道。

●提供一條帶有8kHz幀同步信號的2112kbit/s開銷數據接口,易于外部合成384kbit/s、192kbit/s、64kbit/s同向數據接口;

●提供2路2112kbit/s透明數據通道(960路設置條件下);

●提供2路528kbit/s異步采樣數據通道;

●具有微處理器(MP)接口,支持以MP為核心的設計,實現告警、監控以及系統設置(如交叉連接設置)的MP管理;

●提供線路幀失步、公務幀失步、1E-3、1E-6等告警功能以及線路誤碼比特計數、E1輸入信號消失檢測、通道AIS檢測等功能。

3.2 GW7680在TM480中的應用

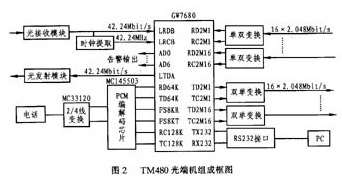

由GW7680構成的光電合一設備再配合一定的控制軟件,即可支持鏈狀網、環狀網的應用系統。在GW7680芯片外圍配置一對光收發模塊、一個微處理器、PCM編解碼芯片、42.24MHz時鐘提取電路及2M接口變換電路即可構成480路單板光端機。這種單板光端機具有許多獨特的功能,非常適合于中小容量需求的接入網。TM480光端機組成框圖如圖2所示。

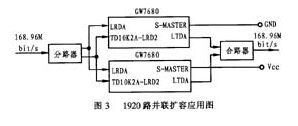

圖2是GW7680芯片最簡單的應用方式。除了這種TM480(終端設備)外,還可組成ADM480(分插復用器);如果使用2片GW7680,則可擴容為960路或1920路的TM和ADM,這主要取決于GW7680的串、并使用及軟件設置。其中TM1920和ADM1920可廣泛應用于干線傳輸網中,它的容量相當于SDH的STM-1(1890路),性能與SDH不相上下,但價格卻比SDH便宜。這種擴容方式如圖3所示。

3.2 GW7680芯片的應用技巧

在光纖傳輸系統中,無論是鏈狀網結構還是環狀網結構,光信號每經過一個中轉(中繼)設備時,必須有一個時鐘提取(也叫線路定時)過程,以實現網同步。實現網同步的目標是使網中所有交換節點的時鐘頻率和相位都控制在預先確定的容差范圍內,以便使網內各交換節點的全部數字流實現正確有效的交換。否則,在數字交換機的緩存器中會產生信息比特的溢出和取空,導致數字流的滑動損傷,從而使數據出錯。

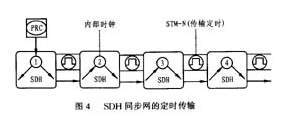

對一般的PDH傳輸網或SDH傳輸網設備而言,其發送定時總是與接收的定時信號有關,下面以SDH同步網的定時傳輸為例進行說明,其框圖如圖4所示。

在SDH系統中,主要采用主從同步方式,PRC(基準時鐘)為網中的最高一組時鐘,各分級時鐘是從傳輸信號中獲取的,然后向下一級轉發出去,因此每一個SDH網絡單元都直接地影響了定時信號,即每個SDH網元通過4.6ppm精度的內部時鐘跟蹤外定時信號,然后轉發出去。當多個4.6ppm的時鐘級聯時必將造成定時抖動積累。于是,從網同步的角度考慮,為了保證SDH組網后能夠正常運行,同步傳輸鏈路應盡量短,整個鏈路的G.812時鐘節點數應不超過10個,每一個SDH節點至少應有2個獨立的外定時輸入,以保證足夠的定時可靠性。

用2片GW7680構成的線路定時網同步方式頗具特色,跟 SDH網同步方式相比,它在線路定時提取過程中幾乎沒有任何時鐘抖動積累。線路定時提取原理如圖5所示。

當接收到上一站傳來的42.24 Mbit/s的線路信號時,1片GW7680(A單元)將其分接成16個2Mbit/s的信號, 再經另一片GW7680(B單元)復接、線路編碼成42.24Mbit/s的信號輸出,這時的時鐘信號不是由定時提取電路提出來的,而是由B單元同步復接出來的,它不需要參考別的時鐘(如PRC),也不需作任何頻偏調整。因此,當多個站采用這種本地線路定時提取方式組聯成鏈狀網或環網時,每個站的線路定時都獨立,不存在時鐘的轉發問題,因而不會造成整個鏈狀網或環網的定時抖動積累。這是一般的SDH和PDH設備無法做到的。

4. 結束語

綜上所述,根據不同的設計要求來選擇復接芯片時,首先應對各種復接芯片的功能進行分析,然后分析采用該芯片完成電路設計時的外圍電路實現的難易程度,最后考慮復接芯片的性價比。這樣設計的電路既能滿足要求,又能達到事半功倍的效果。另外,在使用某一芯片時,要盡量挖掘該芯片的潛能,進行靈活搭配使用,這樣往往能夠開發出意想不到的、性能優異的電路或設備,如本文提到的用2片GW7680構成一種獨特的本地線路定時提取方案便是如此。

責任編輯:gt

-

芯片

+關注

關注

459文章

52300瀏覽量

437677 -

接口

+關注

關注

33文章

8968瀏覽量

153347 -

光端機

+關注

關注

1文章

227瀏覽量

23805

發布評論請先 登錄

GW1N系列安徽非易失性大時代FPGA芯片成員可靠嗎

AD7680的SCLK設置為1MHZ數據輸出管腳一直為低電平

彩電處理芯片LA7680電子資料

DK-START-GW1NS4&GW1NSR4&GW1NSER4_QN48 V1.1開發板用戶手冊

GW1NS-2C MCU串口調試的參考手冊

在電路中使用AD7680檢測一個電壓值,AD7680的數據輸出管腳一直為低電平是為什么?

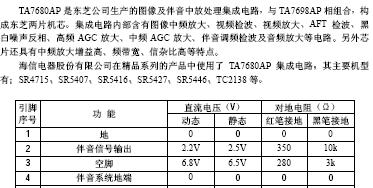

ta7680AP引腳功能及電壓資料

評論