現(xiàn)在,國(guó)際上基于各種算法的數(shù)字視頻傳輸標(biāo)準(zhǔn)已有很多,但壓縮編碼會(huì)對(duì)視頻信息帶來(lái)不同程度的損失,當(dāng)壓縮比高(數(shù)據(jù)傳輸速率低)時(shí),圖像失真嚴(yán)重,容易出現(xiàn)馬賽克及塊效應(yīng)現(xiàn)象。在電視臺(tái)內(nèi)部等要求高清晰度的場(chǎng)合,這種失真是不允許的。因此,本文介紹了一種全數(shù)字、無(wú)壓縮多路數(shù)字視頻光纖傳輸系統(tǒng),可實(shí)現(xiàn)2路視頻和4路音頻信號(hào)的同時(shí)傳輸,且容易實(shí)現(xiàn),傳輸性能好,總體性價(jià)比高。

系統(tǒng)設(shè)計(jì)方案

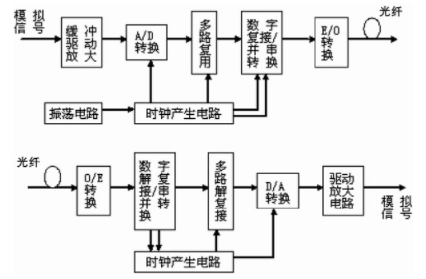

一般情況下,在非壓縮視頻傳輸系統(tǒng)中,通常先把視頻信號(hào)經(jīng)編碼、復(fù)接、電光變換之后,再經(jīng)光纖傳輸?shù)侥康牡兀缓蠼?jīng)光電轉(zhuǎn)換、分接、解碼等處理,還原成原始的視頻信號(hào)。對(duì)于單路視頻傳輸系統(tǒng),復(fù)/解復(fù)接系統(tǒng)一般用通用的復(fù)/解復(fù)接芯片來(lái)實(shí)現(xiàn),但如果系統(tǒng)要傳輸多路視頻信號(hào),現(xiàn)有的復(fù)/解復(fù)接芯片是不能獨(dú)立完成的。以本設(shè)計(jì)要求為例,需要滿足2路視頻和4路音頻的同時(shí)傳輸。每路視頻信號(hào)采用12位量化,2路視頻則需要24路的數(shù)字信號(hào),而HDMP1032芯片最多可擴(kuò)展為17路數(shù)據(jù)復(fù)/解復(fù)接傳輸,這還不包括4路音頻轉(zhuǎn)換為數(shù)字信號(hào)所占用的數(shù)據(jù)位,因而僅僅通過(guò)單個(gè)復(fù)/解復(fù)接芯片不能滿足要求,必須采用多次復(fù)/解復(fù)接才能完成設(shè)計(jì)。本文介紹一種基于HDMP1032/1034串行/解串行芯片,采用二次復(fù)/解復(fù)接實(shí)現(xiàn)多路數(shù)字視頻/音頻/數(shù)據(jù)在一根電纜或光纖上傳輸?shù)姆桨福砜驁D如圖1所示。

圖1系統(tǒng)設(shè)計(jì)原理框圖

圖2 HDMP1034A(Rx)接收端時(shí)序圖

關(guān)鍵技術(shù)

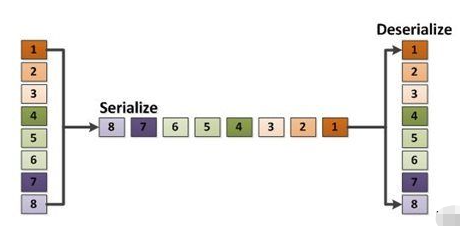

本設(shè)計(jì)采用二次復(fù)用的方法傳輸2路視頻信號(hào)、4路音頻信號(hào)。二次復(fù)用的思想類(lèi)似于脈沖編碼調(diào)制。在發(fā)送端,多路模擬視頻/音頻信號(hào)經(jīng)ADC轉(zhuǎn)換為多路數(shù)字視頻/音頻信號(hào),為了減輕復(fù)接單元的壓力,首先將多路數(shù)字信號(hào)分別通過(guò)一個(gè)合路器進(jìn)行一次復(fù)用,復(fù)用為1路或幾路較高速并行數(shù)字信號(hào),然后再將其送到復(fù)接單元G—Link進(jìn)行二次復(fù)接,得到高速串行數(shù)字信號(hào);在接收端,高速串行信號(hào)首先經(jīng)過(guò)分接單元進(jìn)行一次解復(fù)用,得到較高速多路并行數(shù)字信號(hào),然后分別經(jīng)分路器進(jìn)行二次解復(fù)接恢復(fù)為多路數(shù)字視頻/音頻信號(hào),再通過(guò)DAC轉(zhuǎn)換為多路模擬信號(hào)。整個(gè)系統(tǒng)的同步主時(shí)鐘由一個(gè)32.768MHz的晶振提供。二次復(fù)/解復(fù)接由HDMP1032/1034串行/解串行芯片來(lái)完成,所以主要設(shè)計(jì)的是信號(hào)的一次復(fù)/解復(fù)接部分。由于4路音頻信號(hào)最后合為1路串行信號(hào)進(jìn)入HDMP1032/1034芯片組,所以4路音頻復(fù)/解復(fù)接的時(shí)序是整個(gè)系統(tǒng)的關(guān)鍵。

視頻信號(hào)的處理

首先,分別對(duì)視頻和音頻信號(hào)進(jìn)行量化復(fù)接。兩路視頻經(jīng)過(guò)A/D轉(zhuǎn)換后,采用12位量化后輸出24路數(shù)字信號(hào),取樣速率為16.384MHz,然后經(jīng)過(guò)2:1的復(fù)接器。復(fù)接的具體做法是第一路A/D轉(zhuǎn)換量化后的第一位A0與第二路A/D轉(zhuǎn)換量化后的第一位B0復(fù)接為T(mén)X0,第一路A/D轉(zhuǎn)換量化后的第二位A1與第二路A/D轉(zhuǎn)換量化后的第二位B1復(fù)接為T(mén)X1,依此類(lèi)推,24路視頻信號(hào)復(fù)接為12路并行數(shù)據(jù)TX0、TX1、…、TX11進(jìn)入HDMP1032。由于每路信號(hào)速率為16.384Mbps,故復(fù)接后信號(hào)速率為32.768Mbps。在接收端,HDMP1034仍然輸出12路視頻數(shù)字信號(hào),然后通過(guò)兩個(gè)反相時(shí)鐘分別解出兩路視頻。

音頻信號(hào)一次復(fù)接的實(shí)現(xiàn)

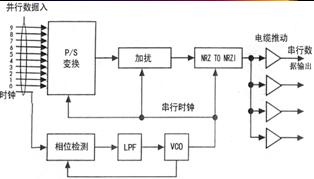

本設(shè)計(jì)中音頻信號(hào)的采樣頻率為32KHz,量化精度為24位,同時(shí)進(jìn)行AES3編碼,轉(zhuǎn)換后的單路音頻碼流速率為4.096Mbps。4路音頻TXP0、TXP1、TXP2和TXP3經(jīng)ADC轉(zhuǎn)換后,通過(guò)4:1數(shù)據(jù)選擇器復(fù)接成1路速率為16.384Mbps的串行數(shù)字信號(hào)TXA,這個(gè)過(guò)程是通過(guò)主時(shí)鐘的4分頻(F1)和8分頻(F2)兩個(gè)時(shí)鐘的4種組合、利用時(shí)分復(fù)用的原理完成的。

作為擴(kuò)展需要, TXA與一路外部擴(kuò)展信號(hào)EX用16.384MHz時(shí)鐘進(jìn)行2:1的復(fù)接,最終得到速率為32.768Mbps的信號(hào)TXAE。這與視頻信號(hào)的速率相等,保證了輸入HDMP1032芯片的各數(shù)據(jù)流速率一致。在接收端,同樣用音頻一次復(fù)用時(shí)采用的時(shí)鐘F1和F2將4路音頻信號(hào)恢復(fù)出來(lái)。

高速串/并轉(zhuǎn)換的實(shí)現(xiàn)

設(shè)計(jì)中視頻/音頻信號(hào)的串行傳輸通過(guò)HDMP1032/4A芯片組完成。HDMP1032/4A芯片組可實(shí)現(xiàn)高速數(shù)據(jù)鏈路的點(diǎn)對(duì)點(diǎn)通信,在使用中,它可以看成傳送數(shù)據(jù)和控制字的“虛擬帶狀電纜”接口。載入Tx發(fā)射芯片的并行位可以經(jīng)過(guò)一個(gè)同軸電纜或是光纖鏈路串行信道到達(dá)Rx接收芯片,并在Rx恢復(fù)為最初的并行格式。

在發(fā)射端,HDMP1032內(nèi)部的鎖相環(huán)(PLL)和時(shí)鐘發(fā)生器用來(lái)產(chǎn)生發(fā)射芯片工作所需要的全部?jī)?nèi)部時(shí)鐘。通過(guò)所需的并行碼率設(shè)置控制信號(hào)TXDIV1/0的選擇,PLL鎖住TXCLK輸入的時(shí)鐘,經(jīng)CIMT編碼后擴(kuò)展為20位(16位碼位+4位編碼位)。鎖相完成后,芯片開(kāi)始接收并行碼率在TXDIV1/0設(shè)定范圍內(nèi)的信號(hào)。又根據(jù)控制位的狀態(tài),決定信號(hào)類(lèi)型、進(jìn)行編碼復(fù)接、串行輸出。

在接收端,高速串行數(shù)據(jù)進(jìn)入Rx后,片內(nèi)的時(shí)鐘——數(shù)據(jù)恢復(fù)電路(CDR)從輸入數(shù)據(jù)提取時(shí)鐘,恢復(fù)出數(shù)據(jù)。CDR電路鎖住REFCLK的頻率,與抽樣后的輸入信號(hào)相位對(duì)齊。恢復(fù)后的數(shù)據(jù)進(jìn)入解復(fù)接電路,時(shí)鐘發(fā)生器根據(jù)碼流速率產(chǎn)生內(nèi)部電路所需的所有時(shí)鐘。此時(shí)串行數(shù)據(jù)解復(fù)接為并行數(shù)據(jù),再進(jìn)入譯碼器譯碼,然后輸出并行碼。

信號(hào)經(jīng)一次復(fù)接后,2路視頻和4路音頻復(fù)接為13路并行的數(shù)字信號(hào),同時(shí),為了準(zhǔn)確恢復(fù)音頻信號(hào),保證接收端和發(fā)射端信號(hào)與復(fù)接時(shí)鐘之間的相對(duì)關(guān)系不變,我們將復(fù)接時(shí)用到的時(shí)鐘F1和F2也作為數(shù)據(jù)與信號(hào)并行傳輸,在接收端得到RF1和RF2。這樣,加上2路時(shí)鐘信號(hào),總共15路數(shù)字信號(hào)進(jìn)入二次復(fù)接芯片HDMP1032A的數(shù)據(jù)位。由HDMP1032A出來(lái)的1路串行數(shù)據(jù)經(jīng)光纖傳輸進(jìn)入HDMP1034A,通過(guò)其內(nèi)部處理,在接收端得到的仍然是15路數(shù)字信號(hào),即進(jìn)入HDMP1032A的并行信號(hào)。這樣,音視頻信號(hào)的二次復(fù)接和一次解復(fù)接已經(jīng)由HDMP1032/4A芯片組完成。

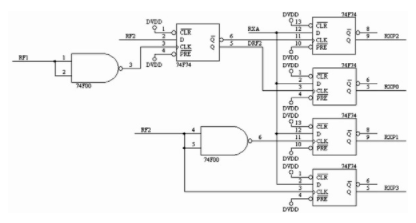

圖3 音頻二次解復(fù)接的電路原理圖

音頻二次解復(fù)接的實(shí)現(xiàn)

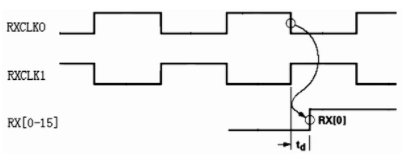

HDMP1034可自動(dòng)產(chǎn)生兩個(gè)互為反相的RXCLK0和RXCLK1,作為所有輸出信號(hào)的標(biāo)志信號(hào),所有的恢復(fù)信號(hào)的相位均以這兩個(gè)信號(hào)作為參考。這對(duì)于得到用于恢復(fù)各路音頻的時(shí)鐘信號(hào)非常重要。圖2所示的是輸出信號(hào)與RXCLK0和RXCLK1之間的時(shí)序關(guān)系。RX[0-15]表示HDMP1032/4A芯片組中可作為信號(hào)傳輸?shù)?6位并行數(shù)據(jù)位,它們與RXCLK0的下降沿存在td、典型值為2ns的延遲。事實(shí)上,作為芯片時(shí)鐘輸入的TXFLAG經(jīng)過(guò)芯片組后得到的RXFLAG同樣與各數(shù)據(jù)位相位一致。

從串行信號(hào)恢復(fù)出的各信號(hào)必須遵循的原則是用復(fù)接時(shí)用到的頻率去恢復(fù)出串行流中包含的各信號(hào)。因此,首先用同樣是Tx恢復(fù)出的16.384MHz的RX16MA將數(shù)據(jù)信號(hào)和外部擴(kuò)展信號(hào)EX分離開(kāi),得到RXA。為了能準(zhǔn)確地恢復(fù)RXA,所選用的16.384MHz時(shí)鐘的邊沿應(yīng)該盡量靠近RXP[0-3]數(shù)據(jù)包的中間部分。處理的辦法是將RXFLAG做為數(shù)據(jù)位,RXCLK1做為時(shí)鐘,經(jīng)過(guò)一個(gè)D觸發(fā)器,得到16.384MHz的RX16MA,這樣,RX16MA與RXAE之間存在約為5ns的延時(shí)。

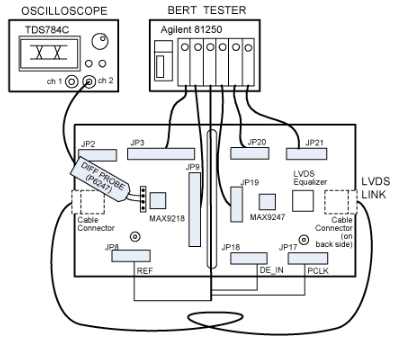

對(duì)于RXP[0-3]的恢復(fù)選用的是兩個(gè)4.096MHz的時(shí)鐘,具體的電路如圖3所示。最后用于RXP[0-3]解復(fù)接的4個(gè)時(shí)鐘信號(hào)分別是DRF2及其反相信號(hào),RF2及其經(jīng)過(guò)與非門(mén)之后的信號(hào)。其中,DRF2及其反相信號(hào)分別解出RXP0和RXP2,RF2及其經(jīng)過(guò)與非門(mén)之后的信號(hào)分別解出RXP3和RXP1。因?yàn)?路音頻復(fù)接成的串行信號(hào)速率為16.384Mbps,因此,對(duì)相鄰兩路音頻信號(hào)解復(fù)接的兩路時(shí)鐘信號(hào)應(yīng)存在一個(gè)周期的延遲,對(duì)應(yīng)到解復(fù)接采用的4.096MHz的時(shí)鐘,即為1/4個(gè)周期的延遲。

這樣,首先將4路音頻與1路擴(kuò)展信號(hào)分離,然后進(jìn)行RXP[0-3]的解復(fù)接,最后恢復(fù)出了4路音頻信號(hào)。

結(jié)語(yǔ)

本方案具有簡(jiǎn)單、實(shí)用、可靠性高、成本低等特點(diǎn),已經(jīng)成功運(yùn)用于傳輸多路音視頻及數(shù)據(jù)信息的光端機(jī)設(shè)計(jì)中。視頻傳輸質(zhì)量達(dá)到廣播電視水平;音頻傳輸質(zhì)量足以滿足專(zhuān)業(yè)級(jí)的立體聲傳輸要求(失真<-75dB、S/N>75dB、20Hz~20kHz帶內(nèi)平坦度<±0.5dB)。

責(zé)任編輯:gt

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423137 -

音視

+關(guān)注

關(guān)注

0文章

8瀏覽量

10277 -

光端機(jī)

+關(guān)注

關(guān)注

1文章

222瀏覽量

23184

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

BCI:1400系列串行數(shù)字視頻及數(shù)字音頻光端機(jī)

串行解串器如何構(gòu)成PHY

探討串行解串器的技術(shù)及其應(yīng)用

瑞盟 MS9218 數(shù)字視頻串/并轉(zhuǎn)換器在數(shù)據(jù)和控制周期對(duì)總共 27 位數(shù)據(jù)解串

什么是34位串行編碼?

怎樣去設(shè)計(jì)一種多路數(shù)字視頻光纖傳輸系統(tǒng)?

串行數(shù)字視頻信號(hào)傳輸系統(tǒng)-SDI接口

MAX9247/MAX9218串行器/解串器芯片組的性能測(cè)試

針對(duì)汽車(chē)后視安全系統(tǒng)的ISL76321串行/解串器接口芯片

串行數(shù)字視頻測(cè)量

MAX9266 HDCP吉比特串行鏈路解串器

采用FPD-Link III技術(shù)實(shí)現(xiàn)數(shù)字視頻信號(hào)遠(yuǎn)傳設(shè)計(jì)

串行解串器的關(guān)鍵技術(shù)及應(yīng)用分析

串行器和解串器對(duì)的性能測(cè)試:MAX9247和MAX9218

MAX9247/MAX9218串行器/解串器芯片組的性能測(cè)試

基于HDMP1032/1034串行/解串行芯片實(shí)現(xiàn)多路數(shù)字視頻光纖傳輸系統(tǒng)設(shè)計(jì)

基于HDMP1032/1034串行/解串行芯片實(shí)現(xiàn)多路數(shù)字視頻光纖傳輸系統(tǒng)設(shè)計(jì)

評(píng)論