作者:符運(yùn)生,陳雪,胡駿,王晨凌,劉冬

基于以太網(wǎng)的無源光網(wǎng)絡(luò)(EPON)是一種融合了以太網(wǎng)和無源光網(wǎng)絡(luò)(PON)優(yōu)點(diǎn)的接入網(wǎng)技術(shù),具有容量大、成本低、對(duì)IP業(yè)務(wù)支持好、技術(shù)成熟和維護(hù)簡單等優(yōu)點(diǎn),是未來實(shí)現(xiàn)FTTx的理想方案之一。目前EPON系統(tǒng)已在日本大規(guī)模應(yīng)用,我國也有不少EPON系統(tǒng)投入商業(yè)應(yīng)用。為使EPON能夠低成本、大規(guī)模地成功應(yīng)用,不僅要求不同廠商的EPON光線路終端(OLT)和光網(wǎng)絡(luò)單元(ONU)設(shè)備能夠互通,而且需要方便有效地在EPON網(wǎng)絡(luò)開通前完成工程驗(yàn)收,以及在EPON網(wǎng)絡(luò)運(yùn)行過程中進(jìn)行便捷的維護(hù)等。由于EPON點(diǎn)對(duì)多點(diǎn)的拓?fù)浣Y(jié)構(gòu)及其相應(yīng)的上行時(shí)分多址接入(TDMA)方式,傳統(tǒng)的網(wǎng)絡(luò)測(cè)試設(shè)備都不能直接介入到EPON系統(tǒng)內(nèi)部,只能通過EPON用戶側(cè)和網(wǎng)絡(luò)側(cè)接口進(jìn)行相關(guān)測(cè)試,因此無法監(jiān)測(cè)EPON內(nèi)部運(yùn)行狀況,不能對(duì)會(huì)影響互通的EPON相關(guān)協(xié)議進(jìn)行測(cè)試分析。為此我們?cè)O(shè)計(jì)開發(fā)了EPON測(cè)試儀,以幫助運(yùn)營商進(jìn)行EPON組網(wǎng)前的設(shè)備互通測(cè)試和組網(wǎng)后的工程驗(yàn)收和網(wǎng)絡(luò)維護(hù)。

1、系統(tǒng)簡介

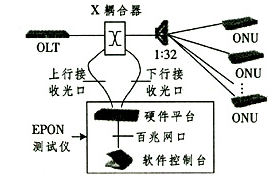

EPON采用單纖雙向通信方式,為了觀測(cè)EPON的內(nèi)部運(yùn)行情況,我們?cè)贠LT與光分配網(wǎng)絡(luò)(ODN)主干光纖之間接入X型光耦合器,分出部分上行和下行光信號(hào)至EPON測(cè)試儀,以實(shí)現(xiàn)對(duì)上下行鏈路的監(jiān)視,如圖1所示。

圖1EPON測(cè)試儀介入被測(cè)網(wǎng)絡(luò)的方式

EPON測(cè)試儀由硬件平臺(tái)和配套的軟件控制臺(tái)兩大部分組成,其中硬件平臺(tái)負(fù)責(zé)EPON協(xié)議幀和相關(guān)數(shù)據(jù)的采集處理以及與軟件控制臺(tái)的通信,軟件控制臺(tái)負(fù)責(zé)EPON相關(guān)協(xié)議分析、提供用戶界面和對(duì)硬件平臺(tái)的配置管理等。本文著重闡述EPON測(cè)試儀硬件平臺(tái)的設(shè)計(jì)與實(shí)現(xiàn)。

2、硬件平臺(tái)功能需求分析

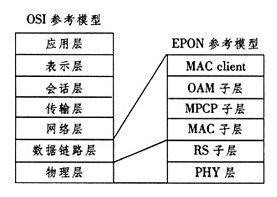

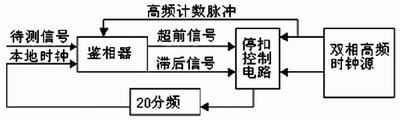

EPON測(cè)試儀主要關(guān)注影響EPON互通和運(yùn)維的EPON調(diào)和(RS)子層、多點(diǎn)MAC控制(MPCP)子層和運(yùn)行管理維護(hù)(OAM)子層。其中RS子層定義了EPON的前導(dǎo)碼格式,它在原以太網(wǎng)前導(dǎo)碼的基礎(chǔ)上引入了邏輯鏈路標(biāo)識(shí)(LLID)區(qū)分OLT與各個(gè)ONU的邏輯連接,并增加了對(duì)前導(dǎo)碼的8位循環(huán)冗余校驗(yàn)(CRC8);MPCP子層負(fù)責(zé)ONU到OLT的注冊(cè)、上行方向TDMA機(jī)制的運(yùn)行等;OAM子層則負(fù)責(zé)有關(guān)EPON網(wǎng)絡(luò)運(yùn)維的功能。EPON參考模型如圖2所示。

圖2EPON參考模型

EPON測(cè)試儀的主要功能有兩個(gè):幫助發(fā)現(xiàn)影響互通的原因和方便EPON網(wǎng)絡(luò)的管理維護(hù)。前一個(gè)功能主要是指它可以幫助分析ONU的注冊(cè)過程是否符合標(biāo)準(zhǔn)、注冊(cè)成功后上層OAM消息的交互和業(yè)務(wù)的互通是否存在問題等;后一個(gè)功能主要是指它可為網(wǎng)絡(luò)維護(hù)人員提供在線ONU的基本信息和鏈路參數(shù)的統(tǒng)計(jì)數(shù)據(jù),以方便運(yùn)營者對(duì)網(wǎng)絡(luò)的管理和故障定位。

根據(jù)EPON測(cè)試儀的功能要求和我們對(duì)EPON測(cè)試儀硬件平臺(tái)和軟件控制臺(tái)的功能分割,確定EPON測(cè)試儀硬件平臺(tái)功能需求如下:

(1)提取ONU注冊(cè)過程所涉及的幀。

(2)按配置的過濾條件采集非注冊(cè)過程MPCP幀和OAM幀。針對(duì)EPON的特點(diǎn),過濾條件可為LLID、幀的前64字節(jié)內(nèi)用戶自定義的6字節(jié)長關(guān)鍵字,或二者的“與/或”組合。考慮到協(xié)議幀流量、送往軟件控制臺(tái)前的封裝開銷、與控制臺(tái)接口的速率限制和實(shí)現(xiàn)復(fù)雜度等因素,支持最多64個(gè)LLID過濾條件,和兩組用戶自定義關(guān)鍵字,關(guān)鍵字支持精確到比特的掩碼配置。

(3)對(duì)采集到的EPON協(xié)議幀(MPCP/OAM幀)打上本地時(shí)鐘標(biāo)簽,并標(biāo)明是來自EPON上行還是下行鏈路。

(4)EPON前導(dǎo)碼校驗(yàn)的差錯(cuò)率統(tǒng)計(jì),支持統(tǒng)計(jì)使能和統(tǒng)計(jì)數(shù)據(jù)上報(bào)周期的配置。

(5)基于最多256個(gè)LLID,對(duì)前導(dǎo)碼正確的EPON幀的業(yè)務(wù)流量和幀校驗(yàn)序列(FCS)校驗(yàn)結(jié)果進(jìn)行統(tǒng)計(jì),支持統(tǒng)計(jì)使能和統(tǒng)計(jì)數(shù)據(jù)上報(bào)周期的配置。

(6)采集到的EPON協(xié)議幀和統(tǒng)計(jì)信息被封裝到以太網(wǎng)幀后通過百兆以太網(wǎng)接口送軟件控制臺(tái)分析。

(7)硬件平臺(tái)的配置內(nèi)容由軟件控制臺(tái)通過百兆接口下達(dá),配置內(nèi)容包括EPON協(xié)議幀的過濾條件、鏈路統(tǒng)計(jì)項(xiàng)的使能和上報(bào)周期、EPON協(xié)議幀和統(tǒng)計(jì)信息被封裝到以太網(wǎng)幀時(shí)的源地址/目的地址/類型(DA/SA/type)字段等,硬件平臺(tái)應(yīng)支持向軟件控制臺(tái)返回配置確認(rèn)幀。

3、硬件平臺(tái)的設(shè)計(jì)實(shí)現(xiàn)

3.1硬件總體結(jié)構(gòu)

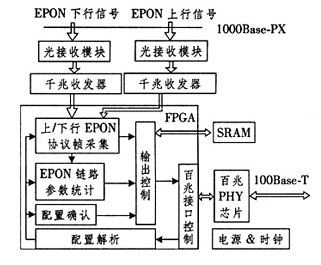

EPON測(cè)試儀硬件平臺(tái)的組成如圖3所示:

圖3EPON測(cè)試儀硬件平臺(tái)框圖

光接收模塊采用符合IEEE 802.3ah規(guī)范中1000Base-PX光接口要求的EPON光收發(fā)模塊,但只使用光接收部分。千兆以太網(wǎng)收發(fā)器芯片則采用商用芯片,它完成比特同步和串/并變換功能,然后將并行數(shù)據(jù)通過10比特接口(TBI)輸出給EPON測(cè)試儀核心功能現(xiàn)場(chǎng)可編程門陣列(FPGA)來處理。

核心功能FPGA完成底層硬件平臺(tái)的核心處理功能,包括EPON協(xié)議幀的采集、EPON鏈路參數(shù)統(tǒng)計(jì)和用戶配置等,綜合考慮這些功能對(duì)FPGA的資源需求、可擴(kuò)展性和低成本要求,我們選擇的是Altera公司的stratix系列芯片。

百兆物理層(PHY)芯片采用的是VT6108S,它實(shí)現(xiàn)核心功能FPGA與軟件控制臺(tái)的接口功能。由于核心功能FPGA采集數(shù)據(jù)的峰值速率可達(dá)千兆速率,而輸出給控制臺(tái)時(shí)僅為百兆速率,故使用一個(gè)外部靜態(tài)存儲(chǔ)器(SRAM)實(shí)現(xiàn)輸出數(shù)據(jù)的緩存。

3.2核心功能的FPGA設(shè)計(jì)

3.2.1EPON協(xié)議幀的采集

圖4是上/下行協(xié)議幀采集框圖。千兆收發(fā)器芯片通過TBI接口將EPON上/下行鏈路的數(shù)據(jù)送給核心功能FPGA,F(xiàn)PGA以異步先入先出(FIFO)方式將接收到的數(shù)據(jù)同步到FPGA內(nèi)部的125 MHz時(shí)鐘,然后進(jìn)行8B/10B解碼,轉(zhuǎn)換為千兆比特媒質(zhì)無關(guān)接口(GMII)格式的數(shù)據(jù)并恢復(fù)出各幀。

圖4上/下行協(xié)議幀采集框圖

經(jīng)過EPON前導(dǎo)碼校驗(yàn)和FCS校驗(yàn)后,錯(cuò)誤的幀將被丟棄。由于MPCP幀的type域?yàn)?x8808,OAM幀的type域?yàn)镺x8809,幀分類模塊據(jù)此篩選出MPCP/OAM幀送過濾模塊。

過濾模塊包括一個(gè)注冊(cè)過程提取模塊和一個(gè)用戶自定義過濾模塊。注冊(cè)過程提取模塊能夠根據(jù)LLID和幀內(nèi)type/opcode字段篩選出所有的注冊(cè)過程幀,其余的幀送用戶自定義過濾模塊。用戶自定義過濾模塊支持按LLID過濾,或按用戶自定義幀內(nèi)字段過濾,或按兩種過濾條件的“與/或”組合過濾,具體參數(shù)見硬件平臺(tái)功能需求分析。

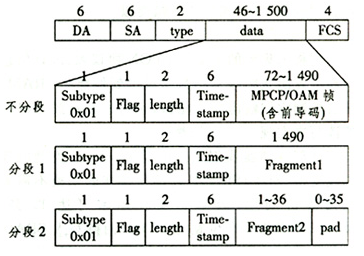

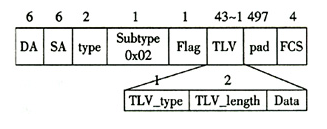

由于硬件平臺(tái)與軟件控制臺(tái)的接口為百兆以太網(wǎng)口,故采集到的EPON協(xié)議幀(含EPON前導(dǎo)碼)需要先封裝到以太網(wǎng)幀再輸出給軟件控制臺(tái),封裝時(shí)應(yīng)盡量反映EPON協(xié)議幀的原始信息,如采集時(shí)間、來自EPON上行方向還是下行方向等,這些分別在timestamp域和flag域中標(biāo)識(shí),另外考慮到EPON幀封裝到以太網(wǎng)幀后的長度可能會(huì)超過以太網(wǎng)的最大傳輸單元(MTU),長度大于1 490字節(jié)的EPON協(xié)議幀將被分為2段封裝,有關(guān)分段的信息也包含在flag域。封裝格式見圖5。其中在subtype域標(biāo)明以太網(wǎng)幀的凈荷部分為EPON協(xié)議幀。

圖5EPON協(xié)議幀的封裝

3.2.2EPON鏈路參數(shù)統(tǒng)計(jì)

我們對(duì)反映EPON鏈路性能最為關(guān)鍵的3類信息:EPON前導(dǎo)碼CRC8校驗(yàn)的差錯(cuò)率、各LLID對(duì)應(yīng)幀的FCS校驗(yàn)差錯(cuò)率和各LLID對(duì)應(yīng)的業(yè)務(wù)流量信息,進(jìn)行了統(tǒng)計(jì)上報(bào)。

基于用戶對(duì)幾類統(tǒng)計(jì)數(shù)據(jù)的關(guān)注程度不同,底層支持對(duì)各類統(tǒng)計(jì)的使能和上報(bào)周期控制,在上報(bào)周期到達(dá)時(shí)刻,統(tǒng)計(jì)信息將被打包輸出。為了在數(shù)據(jù)輸出時(shí)仍能進(jìn)行統(tǒng)計(jì),我們使用了兩套統(tǒng)計(jì)模塊,當(dāng)一套需要輸出統(tǒng)計(jì)信息時(shí),則切換到另一套進(jìn)行參數(shù)統(tǒng)計(jì)。

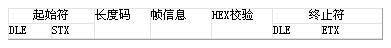

在EPON中,OAM消息均以TLV(Type Length Value)的格式承載,然后再被封裝到OAM幀中的data域,這種格式使得OAM消息具有很好的擴(kuò)展性。在此我們借鑒了EPON OAM幀的封裝方式,統(tǒng)計(jì)數(shù)據(jù)將先被封裝到一個(gè)TLV中,在TLV頭部的type字段標(biāo)明該TLV承載了哪類統(tǒng)計(jì)信息,通過length域標(biāo)明該TLV的長度。在將TLV封裝到以太網(wǎng)幀時(shí),仍使用了subtype字段來標(biāo)識(shí)該以太網(wǎng)幀的凈荷部分為統(tǒng)計(jì)信息,flag域預(yù)留,封裝格式見圖6。

圖6統(tǒng)計(jì)信息的封裝格式

3.2.3配置解析

來自軟件控制臺(tái)的各種配置消息由配置解析模塊處理后,被送往相應(yīng)模塊。用戶可配內(nèi)容包括EPON協(xié)議幀的過濾條件、各鏈路統(tǒng)計(jì)項(xiàng)的使能和上報(bào)周期以及數(shù)據(jù)封裝到以太網(wǎng)幀時(shí)的DA/SA/type字段等。

考慮到與軟件控制臺(tái)的通信線路可靠性,當(dāng)配置解析模塊收到一個(gè)沒有誤碼的配置消息后,它將產(chǎn)生一個(gè)包含該配置消息號(hào)和配置生效時(shí)間的確認(rèn)幀告知控制臺(tái),格式與統(tǒng)計(jì)幀類似。

3.2.4輸出控制

它將采集到的上下行EPON協(xié)議幀、統(tǒng)計(jì)信息幀和配置確認(rèn)幀等幾路數(shù)據(jù)調(diào)度到外部的SRAM,然后控制它們輸出到百兆口,這通過對(duì)外部SRAM的讀寫來實(shí)現(xiàn)。

外部存儲(chǔ)器我們采用的是pipelined類型的零總線變換(ZBT)SRAM,其讀寫操作的切換不需要任何等待周期,因而總線利用率可達(dá)100%。SRAM的數(shù)據(jù)接口位寬為36 bit,而待寫入SRAM的各路數(shù)據(jù)位寬為9 bit(8 bit數(shù)據(jù)+1 bit幀包絡(luò)信息),這樣各路數(shù)據(jù)每4個(gè)時(shí)鐘分別往SRAM寫一次36 bit位寬數(shù)據(jù)即可實(shí)現(xiàn)線速存儲(chǔ)。為此將SRAM劃分為3個(gè)獨(dú)立的存儲(chǔ)區(qū),并將讀寫時(shí)隙分配如下:第1個(gè)時(shí)鐘周期可往SRAM的存儲(chǔ)1區(qū)寫EPON上行協(xié)議幀,第2個(gè)時(shí)鐘周期可往SRAM的存儲(chǔ)2區(qū)寫EPON下行協(xié)議幀,第3個(gè)時(shí)鐘周期可往SRAM的存儲(chǔ)3區(qū)寫統(tǒng)計(jì)信息幀和配置確認(rèn)幀,第4個(gè)時(shí)鐘周期可從SRAM讀出數(shù)據(jù),從某一塊存儲(chǔ)區(qū)讀出完整一幀后即切換到讀另一塊存儲(chǔ)區(qū)。

3.3測(cè)試結(jié)果

我們?cè)诒本└窳滞?a target="_blank">科技發(fā)展有限公司的EPON系統(tǒng)上進(jìn)行了實(shí)際測(cè)試。所研發(fā)的EPON測(cè)試儀能夠提取ONU注冊(cè)過程中涉及到的所有幀;當(dāng)收到控制臺(tái)配置的過濾條件時(shí),它將向控制臺(tái)返回一個(gè)確認(rèn)消息,然后按照配置的過濾條件提取特定MPCP/OAM幀;可對(duì)幾類鏈路參數(shù)中的某一類或全部進(jìn)行統(tǒng)計(jì),并可獨(dú)立配置各類統(tǒng)計(jì)數(shù)據(jù)的上報(bào)周期;所有送往控制臺(tái)的數(shù)據(jù)均按設(shè)定格式封裝到以太網(wǎng)幀。此外我們還對(duì)EPON測(cè)試儀硬件平臺(tái)支持的參數(shù)進(jìn)行了測(cè)試,測(cè)試結(jié)果表明,各項(xiàng)功能和性能指標(biāo)均與設(shè)計(jì)要求相符。

4、結(jié)束語

本文說明了研究開發(fā)EPON測(cè)試儀的意義,簡要描述了其功能結(jié)構(gòu),并著重闡述了其硬件平臺(tái)的FPGA設(shè)計(jì)與實(shí)現(xiàn)。EPON測(cè)試儀可以有效地幫助網(wǎng)絡(luò)運(yùn)營商進(jìn)行設(shè)備互通測(cè)試、工程驗(yàn)收和網(wǎng)絡(luò)運(yùn)維等。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603004 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5419瀏覽量

171600

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

液晶電視屏幕測(cè)試儀是如何實(shí)現(xiàn)的

求大神分享一種高速突發(fā)模式誤碼測(cè)試儀的FPGA實(shí)現(xiàn)方案

基于FPGA的RS485接口誤碼測(cè)試儀的設(shè)計(jì)怎么實(shí)現(xiàn)?

求一種基于FPGA的誤碼率測(cè)試儀的方案

如何去實(shí)現(xiàn)EPON測(cè)試儀硬件平臺(tái)的設(shè)計(jì)?

基于電路板維修測(cè)試儀軟件系統(tǒng)的實(shí)現(xiàn)

基于USB接口的通用測(cè)試儀的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的智能誤碼測(cè)試儀

基于FPGA的新型誤碼測(cè)試儀的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的高速誤碼測(cè)試儀的設(shè)計(jì)

數(shù)字電容測(cè)試儀實(shí)現(xiàn)方案

耐壓測(cè)試儀原理_耐壓測(cè)試儀結(jié)構(gòu)組成

基于DDS和FPGA器件實(shí)現(xiàn)頻率特性測(cè)試儀的設(shè)計(jì)

基于51內(nèi)核和FPGA器件實(shí)現(xiàn)便攜式幅頻特性測(cè)試儀的應(yīng)用方案

韌性測(cè)試儀詳解

基于FPGA器件實(shí)現(xiàn)EPON測(cè)試儀的應(yīng)用設(shè)計(jì)

基于FPGA器件實(shí)現(xiàn)EPON測(cè)試儀的應(yīng)用設(shè)計(jì)

評(píng)論