最近,關于臺積電的先進封裝有很多討論,讓我們透過他們的財報和最新的技術峰會來對這家晶圓代工巨頭的封裝進行深入的介紹。

資料顯示,在張忠謀于2011年重返公司之后,就下定決定要做先進封裝。而1994年加入公司的余振華就是臺積電這個“秘密”項目的帶頭人。CoWoS技術則是臺積電在這個領域的小試牛刀。他們這個技術首先在Xilinx的FPGA上做了實現,而基于此衍生的InFO封裝則在蘋果處理器上大放異彩,并從此讓臺積電的封裝名揚天下。

臺積電先進封裝技術科普

據Semiwiki報道,去年,臺積電將他們的 2.5D 和 3D 封裝產品合并為一個單一的、全面的品牌3DFabric。

其中,2.5D封裝技術CoWoS可分為 CoWoS 和 InFO 系列。首先看CoWoS技術,可以分為以下幾種:

1、CoWoS-S

用于die到die再分布層 (redistribution layer:RDL) 連接的帶有硅中介層的“傳統”基板上晶圓上芯片(chip-on-wafer-on-substrate with silicon interposer )正在慶祝其大批量制造的第 10 年。

2、CoWoS-R

CoWoS-R 選項用有機基板中介層取代了跨越 2.5D die放置區(qū)域范圍的(昂貴的)硅中介層。CoWoS-R 的折衷是 RDL 互連的線間距較小——例如,與 CoWoS-S 的亞微米間距相比,有機上的間距為 4 微米。

3、CoWoS-L

在硅 –S 和有機 –R 中介層選項之間,TSMC CoWoS 系列包括一個更新的產品,具有用于相鄰die邊緣之間(超短距離)互連的“本地”硅橋。這些硅片嵌入有機基板中,提供高密度 USR 連接(具有緊密的 L/S 間距)以及有機基板上(厚)導線和平面的互連和功率分配功能。

請注意,CoWoS 被指定為“chip last”組裝流程,芯片連接到制造的中介層。

再看2.5D封裝技術InFO。

據介紹,InFO 在載體上使用(單個或多個)裸片,隨后將這些裸片嵌入molding compound的重構晶圓中。隨后在晶圓上制造 RDL 互連和介電層,這是“chip first”的工藝流程。單die InFO 提供了高凸點數選項,RDL 線從芯片區(qū)域向外延伸——即“扇出”拓撲。如下圖所示,多die InFO 技術選項包括:

InFO-PoP:“package-on-package”InFO-oS:“InFO assembly-on-substrate”

臺積電的3D封裝技術則是SoIC。

據臺積電介紹,公司的3D 封裝與 SoIC 平臺相關聯,該平臺使用堆疊芯片和直接焊盤鍵合,面對面或面對背方向 -表示為 SoIC 晶圓上芯片(chip on wafer)。硅通孔 (TSV) 通過 3D 堆棧中的die提供連接。

SoIC 開發(fā)路線圖如下所示——例如,N7-on-N7 芯片配置將在 21 年第四季度獲得認證。

臺積電對先進封裝的看法

據臺積電介紹,晶圓級系統整合技術(WLSI)在日益復雜的應用領域中藉由混合與匹配不同平臺而迅速發(fā)展。這些包含在晶圓級系統整合范圍內的技術被命名為3DFabric,因為它能夠實現精細間距的芯片到芯片連接,以及利用現有晶圓制程的統合制造理念。

在3DFabric下,先嵌入芯片再做導線互連的所有制程都稱為整合型扇出(InFO)。而先做線路重布層(RDL),然后再將芯片嵌入預制的RDL上就稱為CoWoS(Chip-on-Wafer-on-Substrate)。這個新的命名系統真實反映了制程的本質并指向將來的技術推進軌跡。與同級制程系統整合芯片(System on Integrated Chips, SoIC)、SoW(System on Wafer)和SoIS(System on Integrated Substrate)結合在一起,它們形成了通用的晶圓級系統整合技術家族,將推動產業(yè)界在面對更具挑戰(zhàn)和多樣化的運算系統整合需求下,滿足未來的系統級微縮需求。

臺積電進一步指出,系統整合芯片(TSMC-SoIC)是創(chuàng)新的晶圓級前段三維芯片(3DIC)堆棧平臺,具有卓越的接合密度、互連頻寬、功耗效率和薄形輪廓,可透過系統級微縮來延續(xù)摩爾定律,具有持續(xù)性的效能提升和成本優(yōu)勢。系統整合芯片接下來可以使用傳統封裝或臺積公司新的3DFabric技術。

例如,CoWoS或整合型扇出來做封裝,支援下一代高效能運算(HPC)、人工智能(AI)和行動應用產品。目前臺積公司已使用微米級接合間距制程完成了芯片對晶圓(Chip on Wafer, CoW)和晶圓對晶圓(Wafer on Wafer, WoW)堆棧制程的驗證,具有令人滿意的電性良率和可靠性結果。

臺積公司將繼續(xù)追求系統整合芯片技術的微縮,以與臺積公司先進的硅技術保持一致,進一步提高晶體管密度、系統功耗、性能和面積(Power, Performance, Area,PPA)與成本競爭力。

在臺積電看來,智能產品應用的2.5D領先技術。此技術具有一個大型的硅中介層,該中介層具有次微米級的繞線層和整合電容(integrated capacitors, iCap),因此可以在其上面放置系統單芯片(SoC)和高頻寬存儲器(HBM)等各種小芯片。正在開發(fā)的第五代CoWoS具有創(chuàng)紀錄的硅中介層面積,高達2,400平方毫米,相當于三個全光罩(full-reticle)尺寸。此技術預計于2021年上半年完成驗證。

他們表示,2020年,臺積公司持續(xù)領先全球大量生產第五代整合型扇出層疊封裝技術(InFO-PoP Gen-5)以支援行動應用,并大量生產第二代整合型扇出暨基板封裝技術(InFO-oS Gen-2)支援高效能運算晶粒分割的應用。

第六代InFO-PoP已成功通過認證支援行動應用和增強散熱性能。如期開發(fā)完成的第三代InFO-oS提供了更多的芯片分割,整合于更大的封裝尺寸和更高的頻寬。為了滿足HPC應用的需求,臺積公司開發(fā)了超高頻寬整合型扇出暨局部硅互連技術(InFO Local Silicon Interconnect, InFO_LSI),其中系統單芯片小芯片(Chiplet)藉由超高密度局部硅互連(LSI)整合到三維InFO封裝中。無基板InFO使用多芯片異質整合與更細間距的芯片到芯片互連技術,已成功完成驗證以滿足消費性電子產品的應用。

最新一代整合式被動元件技術(Integrated Passive Device, IPD)提供高密度電容器和低有效串聯電感(Effective Series Inductance, ESL)以增強電性,并已在InFO-PoP上通過認證。AI與5G行動應用將受惠于此增強的InFO-PoP技術。最新一代IPD預計于2021開始大量生產。

臺積電先進封裝的新進展

在臺積電的最新技術研討會上,公司發(fā)布了在封裝方面的一些新進展。

1、最大封裝尺寸和 RDL 增強

對集成到單個封裝中的大量 2.5D 裸片的需求推動了對更大面積的 RDL 制造的需求,無論是在中介層還是重組晶圓上。臺積電繼續(xù)將互連的“拼接”擴展到超過單次曝光最大光罩尺寸。同樣,需要額外的 RDL 層(具有激進的線距)。

更大封裝尺寸和 RDL 層的路線圖包括:

CoWoS-S:3X 標線(2021 年認證);

CoWoS-R:45X 掩模版(2022 年為 3X),有機基板上的 4 個 RDL 層(W/S:2um/2um),使用 SoC + 2 HBM2 die堆棧進行可靠性認證;

CoWoS-L:1.5X 掩模版尺寸的可靠性評估測試工具,在 1 個 SoC 和 4 個 HBM2 芯片堆棧之間有 4 個本地互連橋;

InFO_oS:5X 掩模版(51mm x 42mm,在 110mm x 110mm 封裝上),5 個 RDL 層(W/S:2um/2um),目前在可靠性評估中;

下圖說明了一種潛在的 InFO_oS 配置,其中邏輯芯片被 I/O SerDes 小芯片包圍,以支持高速/高基數網絡交換機。

2、InFO_B(底部)

上面顯示的 InFO_PoP 配置描述了一個 InFO 組件,其頂部連接了一個 DRAM 模塊,在 DRAM 和 RDL 互連層之間有過孔。

TSMC 正在更改此 InFO_PoP 產品,以使 (LPDDR DRAM) 封裝組裝能夠在外部合同制造商/OSAT 上完成,InFO_B 表示一個選項,如下所示。

相應地,臺積電將“開放創(chuàng)新平臺”擴展到包括符合 InFO_B 總裝條件的 3DFabric 合作伙伴。(目前,3DFabric 合作公司有:Amkor Technology、ASE Group、Integrated Service Technology、SK Hynix。)

3、CoWoS-S“標準架構”(STAR)

CoWoS-S 的流行設計實現是將單個 SoC 與多個高帶寬存儲器 (HBM) die堆棧集成。邏輯芯片和 HBM2E(第二代)堆棧之間的數據總線寬度非常大,即 1024 位。

通過 RDL 將 HBM堆棧連接到 SoC 的路由和信號完整性挑戰(zhàn)是相當大的。TSMC 正在為系統公司提供多種標準 CoWoS-S 設計配置,以加快工程開發(fā)和電氣分析進度。下圖說明了一些不同的 CoWoS-S 選項,范圍從 2 到 6 個 HBM2E 堆棧。

臺積電預計 2021 年這些標準設計實施的采用率會很高。

4、新TIM材料

熱界面材料 (hermal interface material:TIM) 薄膜通常包含在高級封裝中,以幫助降低從有源die到周圍環(huán)境的總熱阻。(對于非常高功率的器件,通常應用兩層 TIM 材料層——die和封裝蓋之間的內層以及封裝和散熱器之間的一層。)

對應于更大封裝配置的功耗增加,臺積電先進封裝研發(fā)團隊正在尋求新的內部 TIM 材料選項,如下所示。

5、先進封裝(AP)制造能力擴張

預計 3DFabric 封裝的完整補充將越來越多地采用,臺積電正在大力投資擴大先進封裝 (AP) 制造能力,如下圖所示。

聲明

來源:半導體行業(yè)觀察

版權歸原作者所有,若侵權請聯系刪除

編輯:jq

-

芯片

+關注

關注

455文章

50714瀏覽量

423157 -

臺積電

+關注

關注

44文章

5632瀏覽量

166414 -

單芯片

+關注

關注

3文章

419瀏覽量

34572 -

晶圓代工

+關注

關注

6文章

859瀏覽量

48581 -

3D封裝

+關注

關注

7文章

133瀏覽量

27118

原文標題:科技前沿 | 臺積電的先進封裝

文章出處:【微信號:siid_inno,微信公眾號:深圳創(chuàng)新設計研究院】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

三星電子晶圓代工副總裁:三星技術不輸于臺積電

臺積電引領全球晶圓代工熱潮,明年產值料增逾二成

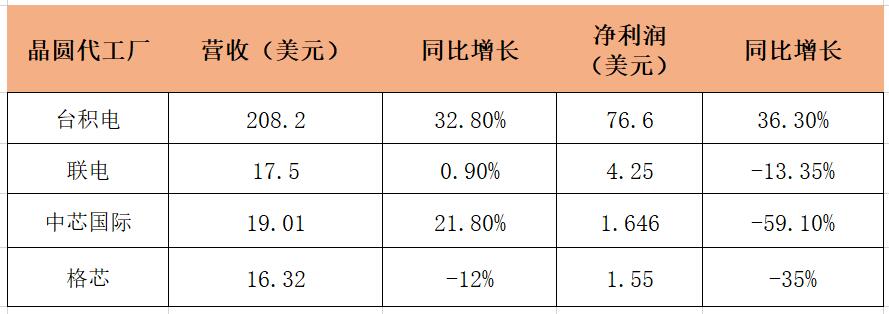

晶圓出貨量增長!臺積電Q2營收飆漲,四大芯片代工廠財報有何亮點?

深入介紹晶圓代工巨頭臺積電的先進封裝

深入介紹晶圓代工巨頭臺積電的先進封裝

評論