很多硬件工程師都有過因為一個小小的不注意,不得不重新打板的經歷,對有些不以為然的工程師甚至成了家常便飯,殊不知這每一次的打板導致的工期延誤對于企業是很大的浪費,尤其是對于爭分奪秒搶占市場的產品來講任何小小的疏忽導致的工期延誤帶來的損失都有可能是致命的。

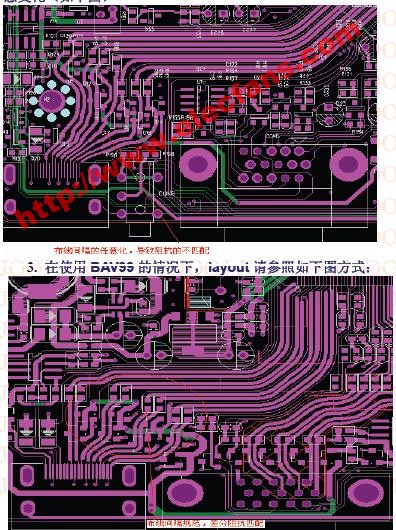

我在前面的文章中說過,硬件工程師設計PCB,即便是一個嶄新的設計,到最終定型不能超過3版,最好2版以內搞定。而做到這一點就必須養成良好的設計習慣,PCB設計是牽扯到很多個環節的鏈條,越早的環節越是重要,為避免最終的錯誤,從一開始就要小心翼翼,不能埋下任何雷。今天蘇老師來講講電路原理圖設計中要注意的一些要點。

首先要說明的是,原理圖是連接產品的概念性設計(方案框圖)和最終的以PCBA形式的物理呈現之間的橋梁,因此它一定要準確、完整。原理圖的基本構成單元是表征一個個電子元器件的“符號(Symbol)”,因此要求原理圖的“符號”一定要準確、完整,而這些符號之間的連線(元器件各管腳之間的電氣連接)要正確無誤。

元器件符號的準確、完整

熟練掌握原理圖符號的編輯(Symbol Editor)是非常重要的,即便在設計中你沒有必要自己親自創建原理圖符號,但你仍然需要查看或檢查這些符號的特性。尤其是你從一些網站上(SamacSys、Ultralibrarian、SnapEDA等)下載的符號,這些網站提供的是適用于各種PCB設計工具的符號,因此最好要根據自己的電路設計對這些符號中的管腳進行位置的重新排列,以及一些管腳屬性的定義。

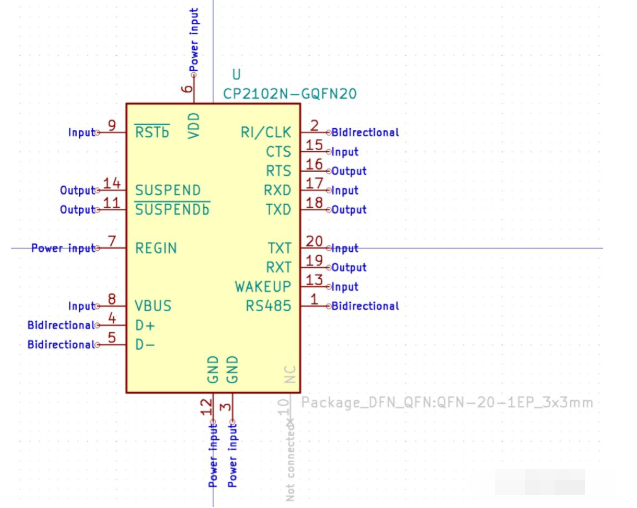

一個元器件的所有的管腳都必須在符號上“可見(Visiable)”,也就是顯示出來,如果這個器件有20個管腳,那就必須有20個管腳出現在符號上,永遠不要用“不可見(Invisible)”管腳,比如“電源”和“地”管腳,另外“No Connect”(簡稱NC - 無連接)的管腳也要顯示出來。

有兩種類型的“NC”管腳,第一種類型是在任何的設計中都不會被連接,它可能本身就是沒有任何內部連接的,或者說只是供生產廠商測試用的。比如上面圖中的CP2102N-GQFN20的第10個管腳就是永遠不用連接的管腳。有的原理圖工具允許給這種管腳設定一個“NC”類型的屬性,這些管腳將被永久地用一個小“x”來標記。你也可以給它們一個獨特的管腳名字NC1、NC2等等,就像在原理圖上顯示的那樣。雖然原理圖允許管腳重名,但我建議最好給每個不同的管腳不同的名字。

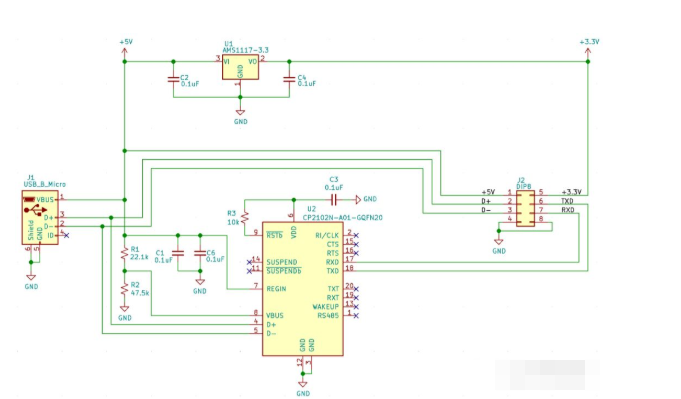

第二種類型的“NC”是有一些管腳是有意義的,但在某些設計中用不著,例如下圖用CP2102設計的USB - UART橋接電路中,有不少管腳內部是有連接,但在這個設計中它們是不用連接上的。很多原理圖工具允許將沒有連接的管腳上放置一個叫“NC”的原理圖符號,一般為“X”的形狀,作為原理圖的一部分。如果原理圖工具中沒有這么個“NC”符號,系統做ERC(電氣規則檢查)的時候就會報“錯誤”(Error)或者“警告”(Warning),在知道事情的原委的前提下你可以忽略這些信息,但一定要確保你知道這些信息的來源。

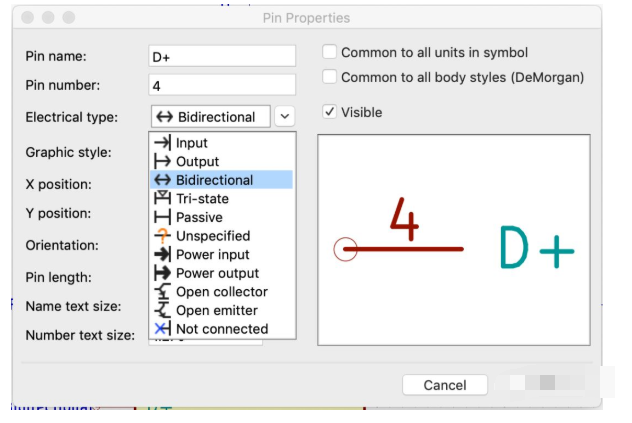

在構建原理圖符號的時候非常重要的一步就是為每個管腳賦予正確的“電氣類型”,這些管腳的類型會用在ERC中,這些電氣類型的添加或編輯有專門的菜單來執行,如下圖(KiCad工具為例),電氣類型選項中可以看出針對每一個管腳的一些典型的電氣特性。

有的時候還是需要一些小技巧才能選到準確的類型的 - 可以選擇最接近的。有時候找不到合適的類型,你可以選擇“Passive”(無源),這個屬性會被輕松通過ERC。不是所有的工具都有“NC”類型,如果沒有的話,你可以選擇一種類型,使得它連接了任何一種管腳ERC都會報錯。

連接器、FPGA、微控制器等這些器件的符號經常需要修改某些管腳的電氣類型,因為這些管腳在不同的設計中其電氣類型是不同的,要根據分配給這些管腳的信號的屬性來重新修改這些管腳的電氣類型。

在創建完所有的原理圖符號后,找一個安靜、無人打擾的地方,打開符號編輯器以及這些元器件的數據手冊,再仔細檢查每一個器件的每一個管腳:管腳編號、管腳名字、電氣類型等,確保每一個管腳都在符號上而且屬性是對的。我個人的習慣是在畫完原理圖以后再檢查一遍原圖中的每個符號,從創建原理圖符號,到繪制原理圖再做最終的檢查中間隔一段時間會比較容易檢查出一些剛創建時無法看出來的問題。

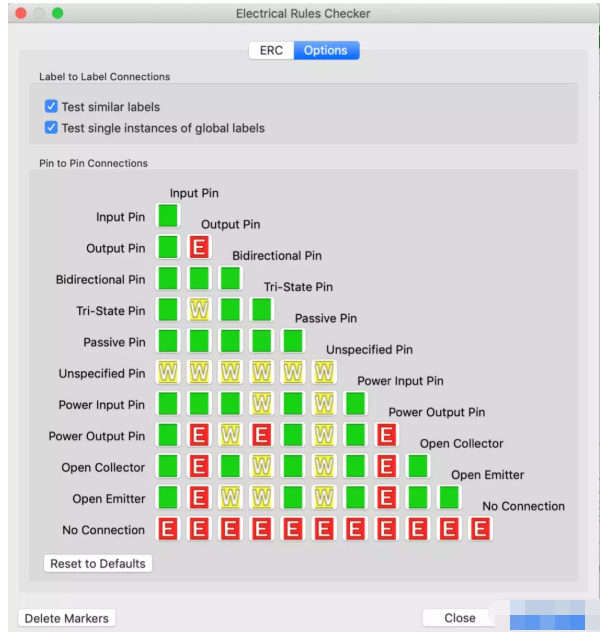

善用ERC(電氣規則檢查)ERC是根據一系列設定的規則進行的電氣連接方面的檢查,如果有不正確的連接就會給出“錯誤”或“警告”的提示信息。一般來講,規則都是在尋找懸空的管腳,或者電氣類型不兼容的管腳之間產生了連接。一般來講,這些規則被一個“連接矩陣”來設定,如下面的例子(來源于KiCad工具):

在矩陣中,每一種可以指定給管腳的電氣類型都有一行和一列,這些由行、列交叉的管腳的每一種組合就被定義了一種規則,在本圖中,矩陣中綠色的意味著兩種類型的管腳是可以進行連接的,一個“W”在ERC報告中會產生一個“報警”信息,一個“E”在ERC報告中會產生一個“錯誤”信息。工具一般都會有一個缺省的矩陣規則,這種規則是常用的,當然在具體的電路設計中你可以根據需要改變這些規則。

雖然ERC是有局限性的,也一定要在設計原理圖的時候運行ERC,根據你電路的設計設計可以調整你電路ERC的規則矩陣,并根據產生的報告修改電路圖中存在的錯誤和不規范的地方,直到所有的錯誤、警告信息全部消失再執行下一步。

通過網表(netlist)檢查

即便你的設計通過了ERC,沒有了錯誤,也沒有了警告提示,但不意味著你的設計一定就安全了,你可能標記網絡名字的時候將兩個名字做了交換,有可能本該連接的管腳并沒有真正連接上,而這些通過ERC可能無法檢查出來的,生成的Netlist可能幫你大忙。

我一般會手工檢查生成的網表 - 對比原理圖中的每一根連線,查找netlist中的每一個連接信息,檢查完一個連接在原理圖上劃掉,并在netlist文件中刪除掉,直到原理圖中的每一個連接、netlist中的每一行信息都彼此做了一一對應。很多人會覺得這沒有必要,但我確實發現過通過其它檢查工具未查出來的問題。對我來講,發現一個問題就值得所有的努力。

機器 - PCB設計工具,畢竟是按照人設定的規則進行檢查的一種方式,它不可能盡善盡美,但學會使用這些工具會對你的設計大有裨益。當然最重要的還是要養成好的設計習慣 - 在創建原理圖符號、繪制原理圖的每一步都要盡可能做到嚴謹、細致、一絲不茍,確保原理圖、原理圖的每一個符號都是準確的、完整的,原理圖的連線都是準確的、完整的并且清晰的。除此之外,考慮到原理圖的易讀性(多數情況下原理圖是給別人看的,而別人更容易發現你看不到的問題),原理圖的設計風格也要做到清晰、規范、符合人的閱讀習慣。

前期點點滴滴的努力,都是為了后期項目進展的順暢,記住一點,前期花的時間越多,整體的效率會越高。

責任編輯人:CC

-

電路原理圖

+關注

關注

40文章

347瀏覽量

38356 -

電路原理圖設計

+關注

關注

0文章

5瀏覽量

6890

發布評論請先 登錄

相關推薦

高速電路中過孔設計注意事項

PCB電源知多少,開關電源布線注意事項

HDMI在TV應用中的注意事項

H6芯片在應用方案設計中的原理圖和PCB設計要點和注意事項詳細說明

電路原理圖設計中的注意事項

電路原理圖設計中的注意事項

評論