目前,多數計算機、嵌入式處理設備和通信設備都采用并行總線,但隨著芯片性能不斷提升和系統越來越復雜,數據傳輸帶寬已成為提高系統性能的瓶頸。雖然增大并行總線寬度可以提高芯片與芯片之間、背板與背板之間的數據吞吐量,但是數據線的增多和傳輸速率的加快會使PCB布線的難度提高,并且增加了信號延時和時鐘相位偏移。高速串行互連技術成為提高數據傳輸帶寬的有效解決途徑。

新的串行總線技術不斷涌現,如新推出的串行總線標準有PCI-express、RapidI()、10Gigabit Ethernet Attachment Unit Interface(XAUI)、HyperTransport、Infini-Band、SATA等。新標準的快速發展及網絡與通信領域不斷增強的數字統一趨勢,對系統設計人員橋接這些標準和適應不斷演化的標準提出了新的挑戰,需要具有新一代系統集成和靈活性的可編程解決方案。Xilinx公司的Vir-tex-4 FX系列FPGA芯片內置了RocketIO收發器,能夠提供622 Mb/s~6.5 Gb/s的數據傳輸速率,并且支持多種高速串行通信協議,可以幫助設計人員方便、靈活、可靠地實現高速通信。

1 設計要素

1.1 時 鐘

在Virtex-4 FX系列FPGA中每個RocketIO Multi-Gigabit Transceiver(MGT)有多個時鐘輸入。其中,參考時鐘有3種,根據不同的傳輸速率選擇不同的參考時鐘。GREFCLK適用于單個MGT組且數據傳輸率低于1 Gb/s的情況。REFCLK1和REFCLK2一般用于數據傳輸率高于1 Gb/s、低于6.5 Gb/s的情況。

時鐘精度和時鐘抖動是評價時鐘質量的兩個重要指標。MGT模塊要求高精度的參考時鐘,MGT要求的時鐘精度為±350×10-6,MGT可容忍的輸入參考時鐘抖動公差最大為40 ps,所以從DCM中出來的時鐘(大于±100ps)不能夠作為MGT的參考時鐘輸入。MGT的時鐘一般采用以下方案解決:從片外輸入的差分時鐘必須經過 RocketIO模塊指定的差分時鐘引腳接入,然后經過Rock-etIO模塊中的時鐘管理模塊GTllCLK_MGT轉化成單端時鐘,送到 REFCLK1或REFCLK2作為MGT的參考時鐘。

MGT模塊的輸出時鐘TXOUTCLK1、TXOUT-CLK2、RXRECCLK1、RXRECCLK2可以作為4個用戶使用的時鐘 TXUSRCLK、TXUSRCLK2、RXUSRCLK、RX-USRCLK2的時鐘源;也可以作為DCM模塊的輸入,從而生成用戶所需的特定頻率的時鐘,提供給系統其他模塊使用。參考時鐘的頻率由串行傳輸速率和時鐘參數設置來決定。表1是該實驗中關于時鐘參數的設置。

1.2 復 位

MGT模塊中的復位分為發送部分的復位和接收部分的復位。發送部分的復位主要包括TXPMARESET和TXPCSRESET;接收部分的復位主要包括RXPMARE-SET和RXPCSRESET。TXPMARESET復位用于復位PMA和重新初始化PMA功能。其引腳電平為高時,復位PLL控制邏輯和內部的PMA分頻器,同時也使發送器PLL LOCK信號為低并且迫使TX PLL進行校驗。TXP-MARESET引腳電平為高至少要持續3個USRCLK時鐘周期。

當TXPCSRESET引腳電平為高時,TX PCS模塊被復位。TX PCS模塊包括:TX Fabric接口,8B/10B編碼器,10GBASE-R編碼器,TX緩沖器,64B/66B擾碼器和10GBASE-R自適應同步器。 TXPCSRESET復位與TXPMARESET復位是相互獨立,互不影響的。

TXPCSRESET復位的要求如下:

①在TXPCSRESET復位時,TXUSRCLK和PCS的TXCLK時鐘必須已經保持穩定,以便初始化發送緩沖器。

②TXPCSRESET引腳電平為高,至少要持續3個TXUSRCLK或TXUSRCLK2時鐘周期。

③在TXPCSRESET復位結束后,TX PCS模塊至少需要5個時鐘周期(以TXUSRCLK或TXUSRCLK2中最長的時鐘周期為準)來完成各個子模塊的復位。

圖1是發送部分的復位時序圖。接收部分的復位時序圖和復位要求與接收部分類似,請參見Xilinx公司技術文檔ug076.pdf。

2 MGT的模塊及原理介紹

發送的并行數據經過8B/10B編碼后,寫入發送端FIFO,然后轉換成串行差分數據發送出去。接收端接收到的串行差分信號首先經過接收端緩沖,然后經過串并轉化器轉換成并行數據,再經過8B/10B解碼,寫入彈性緩沖,最后并行輸出。

2.1 8B/10B編解碼器

8B/10B編碼機制是由IBM公司開發的,已經被廣泛采用。它是一種數值查找類型的編碼機制,可將8位的字符轉化為10位字符。轉化后的字符可以保證有足夠的跳變用于時鐘恢復。 8B/10B編碼具有“0”和“1”出現的概率相等,直流基線漂移小,低頻分量小,功率譜帶寬較窄,抖動小,以及能夠檢測輸入數據中的錯誤等許多優點。

8B/10B編碼可以分為256個數據字符和12個控制字符。數據字符,標為D,用于傳輸數據;控制字符,標為K,用于傳輸控制序列。12個控制字符用于對齊、控制,以及將帶寬劃分為子通道。

2.2 comma字符檢測和對齊

Virtex-4 RRocketIO有可編程的逗號檢測,以便于實現10位字符的各種通信協議和檢測,通過對MCOMMA_10B_VALUE、 DEC_MCOMMA_DETECT、PCOMMA_10B_VALUE、DEC_PCOMMA_DETECT和COMMA_10B_MASK這些參數的設置,可以實現任意的8位或10位符號檢測。

接收器在輸入數據流中掃描搜尋comma字符。如果找到,解串器就調整序列邊界以匹配檢測到的comma字符序列,且掃描是連續進行的。一旦對齊確定,所有后續comma字符的對齊均已確定。在任意的序列組合里,comma字符序列必須是唯一的。常用的K字符是12個K字符中的一個或多個。由于 K28.1、K28.5、K28.7這些字符的頭7位都是1100000,這種比特序列模式只可以在這些控制字符中出現,因此,這些控制字符是非常理想的對齊序列。

2.3 時鐘修正

在時鐘/數據恢復電路的作用下,從接收的串行數據流中解出時鐘的頻率和相位,一般將它的20分頻時鐘作為恢復時鐘。在恢復時鐘作用下從串行數據經過解串器產生并行數據作為8B/10B譯碼的輸入,譯碼后的數據進入16×52位的接收緩沖器。輸入緩沖器的輸人數據速率是由PCS RXCLK的頻率決定的,而從緩沖器讀取端輸出的數據速率是由RXUSRCLK的頻率決定的。由于兩個時鐘會有差異,所以需要進行時鐘修正。

時鐘修正的基本原理是:在發送端,當數據發送了一定的字節或數個數據包后,通過插入和發送一些特定的字節修正字符;在接收端,當接收到這些字符后會自動地丟棄或者重復來補償時鐘的差異。時鐘修正的核心工作是在比特流中搜尋特定的字符序列。

3 MGT的測試與驗證

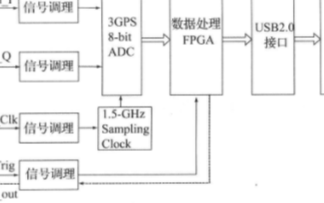

本實驗是在XilinX公司的ML405評估板上進行的,使用2個MGT。其中,MGT1用來發送數據(通過mgt1_tx_n和mgt1_tx_p這對差分線),MGT0用于接收數據(通過mgt0_tx_n和mgt0_tx_p這對差分線)。使用串行ATA電纜(長約100 cm)將它們連接起來形成一個大環路,進行數據讀回測試。MGT驗證實驗的硬件框圖如圖2所示。

其中,gtll_init_tx模塊產生tx—pmareset、tx_pcsreset復位信號以及frame—gen模塊的復位信號;frame—gen模塊產生帶有comma字符的數據流,每次發送的數據位寬為32位;gtll_init_rx模塊產生rx_pmareset、 rx_pcsreset復位信號以及frame_check模塊的復位信號;frame_check模塊用來將發送的數據與實際接收到的來自于MGT0的并行輸出端口的數據進行比較,如果檢測到不一致,則frame_check模塊的ERR_COUNT計數器就加1,通過讀取該計數器的值和記錄MGT工作的時間就可以計算出該系統中MGT的錯誤率。

假設MGT的錯誤率為δ,MGT的數據傳輸率為μ,MGT傳輸數據的有效時間為τ,ERR_COUNT計數器的計數值為E,則有:

實驗中測得,E=319,τ=3 600s,μ=3 Gb/s。將上述數值代入式(1),求得δ=2.957×10-11。通過取不同的時間τ,每個τ對應做多次實驗,可以得到δ的范圍為 [2.752×10-11,3.168×10-11]。通過該實驗可以發現具MGT的可靠性比較高,可以滿足我們的工程需求,具有很高的實際使用價值。

結 語

目前,系統對數據傳輸率的要求越來越高,高速串行互連技術由于將時鐘與數據合并進行傳輸,從而解決了高速并行數據傳輸過程中時鐘和數據的抖動問題,提高了數據傳輸速率,降低了設計復雜性和成本,減少了引腳數量和PC板面積。Xilinx公司的Virtex-4 FX系列FPGA器件中所提供的用于實現高速串行互連的RocketIO IP核,具有使用方便、配置靈活、集成度高等優點,將它用于解決高速串行數據傳輸問題,既簡化了設計,又提高了系統的集成度和可靠性,有很好的應用前景。

責任編輯:gt

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604344 -

芯片

+關注

關注

456文章

50965瀏覽量

424824 -

嵌入式

+關注

關注

5087文章

19148瀏覽量

306171

發布評論請先 登錄

相關推薦

采用多功能器件實現新型數字信號中和器的應用電路設計

如何使用FPGA與FX3實現數據的傳輸?

關于FX2下載FPGA程序,以及實現FPGA與PC通信的問題

FPGA與DSP的高速通信接口設計與實現

FPGA與DSP的高速通信接口設計與實現

FPGA和DSP高速通信接口設計方案

基于Verilog的FPGA與USB 2.0高速接口設計

基于FPGA DSP架構的高速通信接口設計與實現

基于FPGA實現的高速串行交換模塊實現方法研究

基于FPGA的USB3.0協議高速通信架構

FPGA和USB3.0通信-FX3硬件設計簡談

基于Vir-tex-4 FX系列FPGA芯片實現高速通信

基于Vir-tex-4 FX系列FPGA芯片實現高速通信

評論