1 引言

隨著半導(dǎo)體工藝的不斷發(fā)展和通信技術(shù)的不斷提高,以超大規(guī)模、高集成度和復(fù)雜性為特征的通信集成電路芯片物理設(shè)計(jì),相比于普通的消費(fèi)類產(chǎn)品芯片,在超深亞微米工藝下面臨著更為嚴(yán)峻的挑戰(zhàn):一、工藝特征尺寸的不斷縮小、電源電壓的不斷降低、電源噪聲對芯片性能的影響日益凸顯,已成為超大規(guī)模通信集成電路物理設(shè)計(jì)中一個(gè)不可忽視的問題;二、隨著工藝技術(shù)的進(jìn)步,高速通信集成電路芯片的時(shí)序?qū)τ?a href="http://www.1cnz.cn/v/tag/207/" target="_blank">芯片制造過程中產(chǎn)生的偏差越來越敏感,精確的電路模型及準(zhǔn)確的時(shí)序分析方法成為制約通信集成電路芯片能否實(shí)現(xiàn)快速時(shí)序收斂的關(guān)鍵;三、通信集成電路芯片通常需要支持各種高速接口電路的應(yīng)用,從而造就了獨(dú)特的時(shí)鐘樹拓?fù)浣Y(jié)構(gòu)——網(wǎng)狀時(shí)鐘樹,而通信芯片固有的超大規(guī)模的特性更加重了這種復(fù)雜高速時(shí)鐘樹優(yōu)化的難度;四、隨著通信技術(shù)的飛速發(fā)展、數(shù)據(jù)傳輸速度和容量的不斷提高、信道噪聲對信號質(zhì)量的影響越來越大,高速串并/并串轉(zhuǎn)換器(HighSpeedSerdes,HSS)的抗噪性、傳輸信道數(shù)量及其建模仿真的精確度成為影響通信系統(tǒng)設(shè)計(jì)的重要因素。本文針對這些通信芯片的物理設(shè)計(jì)難點(diǎn),較為詳細(xì)地介紹了IBM相應(yīng)的解決方案。

2 物理設(shè)計(jì)難點(diǎn)分析及解決方案

針對超深亞微米工藝下超大規(guī)模通信集成電路所面臨的物理設(shè)計(jì)難點(diǎn),IBM提出了相應(yīng)的解決方案,具體介紹如下。

2.1 電源噪聲分析

目前通信集成電路的規(guī)模不斷增大、工藝特征尺寸不斷減小,芯片的功耗不斷增加而電源電壓則不斷降低,電源噪聲已成為超大規(guī)模集成電路設(shè)計(jì)中一個(gè)不可忽視的問題。由于大規(guī)模通信集成電路芯片通常帶有各種復(fù)雜的高速接口,并在整個(gè)產(chǎn)品的工作過程中要求有很高的可靠性,因此芯片的電源設(shè)計(jì)起著至關(guān)重要的作用。為了保證芯片的電源完整性,在芯片的設(shè)計(jì)流程中必須對IO的同步開關(guān)噪聲SSN(SimultaneousSwitchNoise)、芯片上的動態(tài)電源噪聲、靜態(tài)壓降、ESD(Electro-StaticDischarge)靜電保護(hù)以及電遷移EM(ElectroMigration)進(jìn)行有效的檢查和簽收。

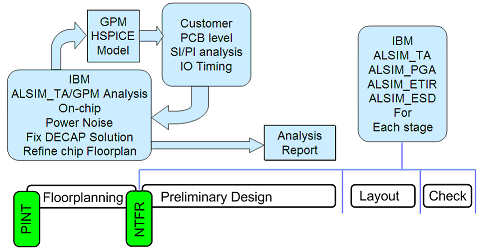

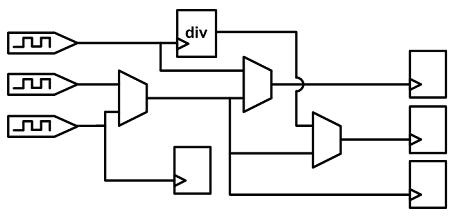

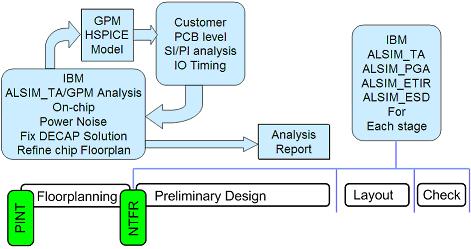

IBM在進(jìn)行超大規(guī)模集成電路的設(shè)計(jì)過程中,有一套完整的流程對電源噪聲進(jìn)行分析(圖1),能夠在芯片的布局階段盡早發(fā)現(xiàn)和解決芯片布局與電源設(shè)計(jì)上存在的問題,從而減少了設(shè)計(jì)反復(fù)的時(shí)間。電源噪聲檢查在芯片設(shè)計(jì)過程中是一個(gè)重要的簽收環(huán)節(jié),完整的設(shè)計(jì)和分析流程保證了IBM能夠提供高質(zhì)量的專用集成電路芯片。

圖1 電源噪聲分析流程

IBM的電源噪聲分析流程貫穿了整個(gè)芯片設(shè)計(jì)過程,其中包含了兩個(gè)噪聲評審會議和一系列分析工具。在每個(gè)項(xiàng)目開始布局之前,噪聲分析小組會和項(xiàng)目的物理設(shè)計(jì)工程師一起召開PINT(Post-IDRNoiseTeamReview)會議,對芯片的設(shè)計(jì)規(guī)格進(jìn)行審查,找出設(shè)計(jì)中可能存在的風(fēng)險(xiǎn),提出在芯片布局時(shí)需要注意的事項(xiàng),讓物理設(shè)計(jì)工程師在布局前對整個(gè)芯片的電源噪聲情況有所了解,盡量避免由于電源噪聲無法滿足而反復(fù)修改布局。在芯片布局階段,負(fù)責(zé)電源噪聲分析的工程師會緊跟布局的變化,利用IBM的GPM(GenericPackageModel)和ALSIM(AustinLinearSimulator)系列工具及時(shí)評估芯片的電源噪聲。

GPM是一個(gè)可以快速分析IO同步開關(guān)噪聲的建模和分析工具。GPM針對芯片中包含IO的局部區(qū)域建立HSPICE模型,其中包含通用的封裝RLC模型,芯片上的電源分配網(wǎng)絡(luò),IO驅(qū)動器模型和模擬一般邏輯電路翻轉(zhuǎn)的等效模型。由于GPM分析不需要成熟的芯片布局,建模和仿真速度快,因此可以盡早分析IO對電源噪聲的影響,為芯片的IO布局提供快速的參考,評估IO所需的電源濾波方案,避免在設(shè)計(jì)中形成電源噪聲的熱點(diǎn)。一旦芯片布局確定,GPM模型可以代表實(shí)際芯片的IO翻轉(zhuǎn)情況,該模型可以交付客戶,讓客戶聯(lián)合系統(tǒng)的板級模型進(jìn)行芯片、封裝和PCB的信號完整性分析和時(shí)序分析。分析的結(jié)果可以幫助客戶在芯片設(shè)計(jì)早期評估系統(tǒng)的性能,同步地進(jìn)行PCB的設(shè)計(jì),確定更加合理的芯片時(shí)序約束。

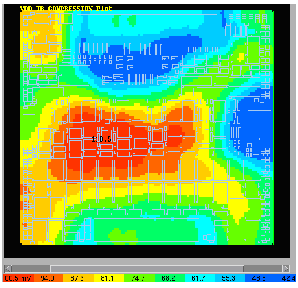

ALSIM_TA(TransientAnalysis)是一個(gè)高效的全芯片動態(tài)電源噪聲仿真分析工具。仿真過程中使用了芯片的封裝模型,片上電源網(wǎng)絡(luò)模型和代表各種邏輯電路翻轉(zhuǎn)的電流波形。通過ALSIM_TA仿真可以得到整個(gè)芯片電源噪聲峰峰值,動態(tài)壓降等信息在芯片上的分布情況,并以二維圖形直觀地顯示,如圖2所示。ALSIM_TA的結(jié)果可以直觀地評估芯片的布局和電源濾波方案對電源噪聲的影響。

圖2 ALSIM_TA仿真結(jié)果

根據(jù)早期的ALSIM_TA和GPM分析結(jié)果,物理設(shè)計(jì)工程師可以盡早優(yōu)化芯片布局,通過增加噪聲源和噪聲敏感的器件之間的距離,增加片上去耦電容等方式獲得較好的噪聲性能。

在芯片布局最終確定之前,噪聲分析小組會和物理設(shè)計(jì)工程師召開NTFR(NoiseTeamFloorplanReview)會議,再次對芯片的布局和電源濾波方案進(jìn)行評審,對高速接口的相關(guān)問題進(jìn)行討論,檢查芯片是否可以滿足電源噪聲簽收的標(biāo)準(zhǔn)并提出建議和進(jìn)一步的分析、優(yōu)化方案。

除了利用GPM和ALSIM_TA對電源動態(tài)噪聲進(jìn)行分析,IBM還使用ALSIM_ETIR對全芯片的靜態(tài)電源壓降進(jìn)行分析。在每個(gè)設(shè)計(jì)階段,ALSIM_ETIR會提取每個(gè)電路上的壓降并反標(biāo)到時(shí)序分析工具中從而得到更真實(shí)的靜態(tài)時(shí)序分析結(jié)果。在每個(gè)設(shè)計(jì)的簽收階段,ALSIM_PGA和ALSIM_ESD是對EM和ESD進(jìn)行檢查和簽收的工具,而GPM則是動態(tài)電源噪聲的簽收工具。通過在每個(gè)設(shè)計(jì)階段對芯片的電源噪聲進(jìn)行完備的檢查,IBM可以設(shè)計(jì)出具有高可靠性的大規(guī)模通信集成電路芯片,保證一次設(shè)計(jì)成功率。

2.2 統(tǒng)計(jì)靜態(tài)時(shí)序分析(SSTA)

隨著工藝技術(shù)的進(jìn)步,芯片制造過程中產(chǎn)生的偏差成為影響芯片性能的重要因素,必須在芯片設(shè)計(jì)的階段就考慮這個(gè)問題。傳統(tǒng)的靜態(tài)時(shí)序分析(StaticTimingAnalysis,STA)方法,建立在以工藝角為基礎(chǔ)的器件時(shí)序模型上。然而隨著工藝技術(shù)的進(jìn)步,反映偏差的參數(shù)迅速增加,不僅包括晶片內(nèi)或晶片間的偏差,還包括各種片上偏差(On-ChipVariation,OCV),例如芯片不同位置上溝道長度、閾值電壓、金屬層厚度等,這導(dǎo)致工藝角的數(shù)目和時(shí)序分析的時(shí)間呈指數(shù)增長。除此之外,STA的另一大缺陷是預(yù)測的時(shí)序過于悲觀,因?yàn)槠骷ぷ髟诿總€(gè)參數(shù)的最壞情況下的機(jī)率是很低的,這導(dǎo)致設(shè)計(jì)的時(shí)序過于保守,從而增加了設(shè)計(jì)難度和時(shí)間。因此,我們需要建立一個(gè)更完備的模型以反映各種工藝偏差對時(shí)序的影響,并在有限的時(shí)間內(nèi),更準(zhǔn)確地進(jìn)行時(shí)序分析。

IBM很早就開始對統(tǒng)計(jì)靜態(tài)時(shí)序分析方法(StatisticalStaticTimingAnalysis,SSTA)進(jìn)行研究,并已取代STA應(yīng)用于65nm、45nm工藝中。SSTA是利用統(tǒng)計(jì)的方式去描述制造工藝中的偏差,采用的模型描述的是各個(gè)偏差的概率分布曲線。

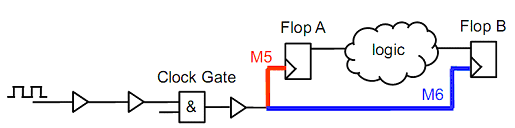

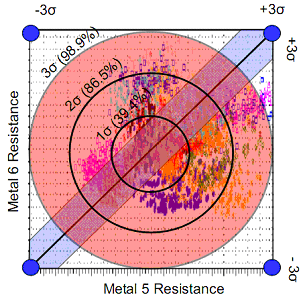

下面我們舉例說明SSTA與STA的不同。如圖3所示,寄存器A和寄存器B的時(shí)鐘端接在同一個(gè)門控時(shí)鐘源,但分別在M5和M6金屬層上布線。傳統(tǒng)的STA沒有考慮不同金屬層之間由于CMP工藝造成的偏差,因此假設(shè)兩條路徑工作在相同的工藝角下,導(dǎo)致實(shí)際的時(shí)鐘偏移(Skew)大于估計(jì)的結(jié)果,電路可能無法正常工作。圖4描述了M5和M6金屬層阻抗偏差的分布,實(shí)際電路可能工作在整個(gè)坐標(biāo)平面內(nèi)的任意一個(gè)點(diǎn)。PrimeTime中通過引入比例因子(DeratingFactor)來解決類似的工藝偏差,兩個(gè)參數(shù)的偏差遵循線性關(guān)系,所覆蓋的范圍為圖4中條狀區(qū)域,比例因子的值決定了所覆蓋區(qū)域的大小。SSTA是基于各個(gè)偏差的概率分布曲線,得到聯(lián)合概率分布曲線,采用3σ分析方法,覆蓋區(qū)域所占比例高達(dá)98.9%。

圖3 金屬層制造偏差引起的時(shí)鐘偏移

圖4 不同時(shí)序分析方法對工藝偏差的覆蓋率

SSTA不以slack作為時(shí)序檢查的依據(jù),而是預(yù)測電路性能對工藝偏差的敏感程度,作為評價(jià)設(shè)計(jì)可靠性的指標(biāo)。SSTA可以分析出芯片上每個(gè)部分能工作在多高的時(shí)鐘頻率下,并為測試方案的設(shè)計(jì)提供依據(jù)。SSTA的基礎(chǔ)是建立可靠的模型來反映工藝偏差的概率分布,IBM已經(jīng)將SSTA應(yīng)用于自主研發(fā)的時(shí)序分析工具Einstimer中,并從65nm工藝開始,作為Sign-off的必要條件。同時(shí),IBM還將SSTA的理念應(yīng)用于布局布線,信號完整性分析等工具中,從統(tǒng)計(jì)學(xué)的角度對電路進(jìn)行優(yōu)化,使設(shè)計(jì)更符合DFM的要求。

2.3 時(shí)鐘樹優(yōu)化

通信集成電路通常需要支持各種應(yīng)用,如HSS、SRAM、DDR、TCAM等;而這些接口電路一般都工作在不同的時(shí)鐘域下。為了實(shí)現(xiàn)各接口電路之間高速的數(shù)據(jù)傳輸,往往需要一些計(jì)算/控制邏輯電路能夠可配置地工作在不同的時(shí)鐘域。這樣就形成了通信領(lǐng)域集成電路芯片獨(dú)特的時(shí)鐘樹拓?fù)浣Y(jié)構(gòu)——網(wǎng)狀時(shí)鐘樹。如圖5所示,多個(gè)異步時(shí)鐘源從PLL、HSS或者IO引入芯片內(nèi)部,經(jīng)過幾級選通器或分頻器,最終到達(dá)每個(gè)時(shí)序器件的時(shí)鐘端。時(shí)鐘結(jié)構(gòu)相同的一組邏輯電路,可以在不同的時(shí)段采用不同的時(shí)鐘頻率;而時(shí)鐘結(jié)構(gòu)不同的邏輯電路,經(jīng)過配置,可以工作在同一時(shí)鐘域下,進(jìn)行同步信號傳輸,滿足特殊的通信需求。因此,在建立和優(yōu)化時(shí)鐘樹時(shí),需要對芯片上各個(gè)時(shí)鐘的到達(dá)時(shí)間進(jìn)行一個(gè)整體的約束,使可能工作在同一時(shí)鐘域下的邏輯電路的時(shí)鐘信號到達(dá)時(shí)間盡量保持一致,從而保證時(shí)序電路正常工作。

圖5 網(wǎng)狀時(shí)鐘樹結(jié)構(gòu)

IBM常用的時(shí)鐘樹優(yōu)化機(jī)制主要由描述時(shí)鐘樹結(jié)構(gòu)的CDOC(ClockDesignerOptimizationControlFile)文件和時(shí)鐘樹優(yōu)化工具BCO兩部分組成。基本工作原理為:首先通過CDOC文件確定需要優(yōu)化的時(shí)鐘樹——CDOC文件描述了各條時(shí)鐘樹的起始點(diǎn)和一個(gè)停止點(diǎn),從起始點(diǎn)開始向后追溯,直到所有分支都遇到停止點(diǎn)為止;其間穿過的結(jié)構(gòu),就是需要優(yōu)化的時(shí)鐘樹;然后BCO根據(jù)CDOC文件所描述的時(shí)鐘樹結(jié)構(gòu),按前后順序依次優(yōu)化——在優(yōu)化每一條時(shí)鐘樹段落時(shí),BCO會按照由葉至根的順序,插入一系列緩沖器或者反向器,使得各個(gè)葉節(jié)點(diǎn)的時(shí)鐘到達(dá)時(shí)間偏差和整個(gè)時(shí)鐘樹延遲都盡量小,BCO還會對時(shí)鐘樹穿過的組合邏輯結(jié)構(gòu)進(jìn)行復(fù)制,放在各個(gè)葉節(jié)點(diǎn)附近,從而滿足優(yōu)化前后邏輯功能的一致性。

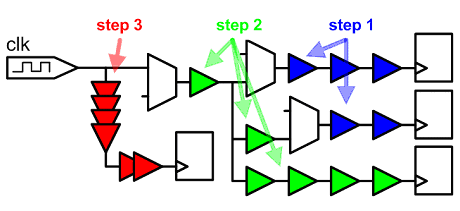

針對通信芯片相對復(fù)雜的時(shí)鐘樹結(jié)構(gòu),BCO在原有機(jī)制的基礎(chǔ)上提供了一種逐級優(yōu)化時(shí)鐘樹的方法:如圖6所示,首先將整個(gè)時(shí)鐘網(wǎng)絡(luò)以選通器或分頻器為節(jié)點(diǎn)分段,按照時(shí)鐘信號的流向,靠近時(shí)鐘源的為父時(shí)鐘樹,反之為子時(shí)鐘樹。然后從最末端的子時(shí)鐘樹開始進(jìn)行優(yōu)化,并將優(yōu)化后的延時(shí)信息標(biāo)記在子時(shí)鐘樹的根節(jié)點(diǎn)上;優(yōu)化父時(shí)鐘樹時(shí),根據(jù)其所有子時(shí)鐘樹的延遲信息,采用時(shí)鐘偏差技術(shù)(PlannedSkewScheduling),使得其下所有時(shí)序器件(包括它的子時(shí)鐘樹)的時(shí)鐘信號到達(dá)時(shí)間相同;以此向前遞歸,直到時(shí)鐘源;從而實(shí)現(xiàn)了整個(gè)時(shí)鐘網(wǎng)絡(luò)優(yōu)化。

圖6 網(wǎng)狀時(shí)鐘樹優(yōu)化方法

2.4 HSS

隨著信息技術(shù)的飛速發(fā)展,特別是通信要求的飛速提高,大容量、高速度的業(yè)務(wù)需求成為了通信系統(tǒng)設(shè)計(jì)的關(guān)鍵考慮因素。在這種背景下,Serdes(串并/并串轉(zhuǎn)換器)應(yīng)運(yùn)而生,并憑借其抗噪性強(qiáng)、傳輸信道數(shù)量少等優(yōu)點(diǎn),越來越顯示出替代高速并行接口電路的趨勢。然而隨著數(shù)據(jù)傳輸速度和容量的不斷提高,信道噪聲對信號質(zhì)量的影響也越來越大,而且不同的業(yè)務(wù)需求也需要有多種的Serdes進(jìn)行支持。如何選擇一款能夠充分滿足業(yè)務(wù)要求的Serdes是大容量通信系統(tǒng)設(shè)計(jì)中的難點(diǎn)。

針對這種需求,IBM提供了多種型號的HSS(HighSpeedSerdes),能夠充分滿足客戶需求。HSS提供了一種可以在多種條件下運(yùn)行的高速串并轉(zhuǎn)換接口,它保證了發(fā)送端數(shù)據(jù)的低噪聲并且能夠根據(jù)接收數(shù)據(jù)提取時(shí)鐘。HSS支持包括從130nm到45nm的半導(dǎo)體工藝,可以達(dá)到最高14Gb的數(shù)據(jù)吞吐率。HSS由接收數(shù)據(jù)、發(fā)送數(shù)據(jù)和內(nèi)建PLL三大部分組成,支持雙工和單工等多種工作模式。HSS支持多種應(yīng)用環(huán)境,包括電纜連接、擴(kuò)展連接單元接口(XAUI)、InfiniBand協(xié)議、串行ATA接口、串行連接SCSI接口、光纖互聯(lián)、SONET以及背板(backplane)應(yīng)用等。

出于減少功耗的考慮,HSS支持多種低功耗模式,所有的數(shù)據(jù)通道可以被關(guān)閉,內(nèi)建PLL也可以被關(guān)閉。通過關(guān)閉不需要的通道和PLL,可以節(jié)省大部分的動態(tài)功耗。另外支持輸出端信號強(qiáng)度調(diào)節(jié)等多種低功耗選擇。

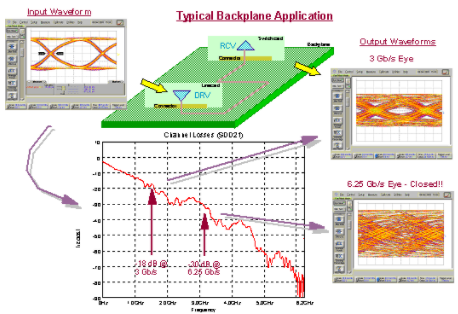

針對越來越復(fù)雜的信道環(huán)境,為了滿足高速大容量業(yè)務(wù)的需要,IBM為HSS提供了完備而精確的仿真和模擬環(huán)境,能夠得到精確的HSS配置結(jié)果從而得到最佳的信號質(zhì)量。客戶通過提取S-parameter,采用IBM提供的HSSCDR工具或者采用業(yè)界通用的AMI模型,以比Hspice高數(shù)十倍的仿真速度,得到最佳的HSS配置,調(diào)節(jié)發(fā)送和接受端的內(nèi)建有限沖激響應(yīng)濾波器(FIR),配合眼圖(Eye-diagram)進(jìn)行信號質(zhì)量檢測,得到包括頻譜分析在內(nèi)的多種圖表,從而有效地輔助客戶設(shè)計(jì),如下圖所示。

圖7 HSSCDR眼圖分析示意圖

3 小結(jié)

本文針對超深亞微米工藝下通信集成電路芯片物理設(shè)計(jì)的各個(gè)難點(diǎn),提出了相應(yīng)的解決方案。本文首先分析了由通信集成電路固有特性所決定的,超深亞微米通信芯片物理設(shè)計(jì)所面臨的挑戰(zhàn),如電源網(wǎng)絡(luò)的穩(wěn)定、時(shí)序的收斂問題、復(fù)雜時(shí)鐘樹的優(yōu)化、高速串并/并串轉(zhuǎn)換器應(yīng)用等;接著較為詳細(xì)地介紹了IBM解決方案,如基于ALSIM系列工具的電源網(wǎng)絡(luò)的分析設(shè)計(jì)流程、統(tǒng)計(jì)靜態(tài)時(shí)序分析方法(SSTA)、時(shí)鐘樹優(yōu)化工具BCO,多種高性能的高速串并轉(zhuǎn)換器及其完備而精確的仿真和建模環(huán)境等。因此,IBM所提出的芯片物理設(shè)計(jì)方法能有效地解決通信集成電路芯片在超深亞微米工藝下的物理實(shí)現(xiàn)難點(diǎn),從而極大地促進(jìn)通信芯片的開發(fā)與應(yīng)用。

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423151 -

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361637 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27290瀏覽量

218087

發(fā)布評論請先 登錄

相關(guān)推薦

Motorola/IBM PowerPC 740/750微處理器的仿真和分析解決方案

Motorola/IBM PowerPC 740/750微處理器的仿真和分析解決方案

無線充電測試難點(diǎn)和解決方案

單片機(jī)之間的通信方式/難點(diǎn)/解決方案

IBM的物聯(lián)網(wǎng)解決方案

IBM發(fā)布混合云時(shí)代新系統(tǒng)解決方案

針對物理設(shè)計(jì)難點(diǎn)進(jìn)行分析及提出解決方案

通信芯片的物理設(shè)計(jì)難點(diǎn)及IBM應(yīng)用解決方案

通信芯片的物理設(shè)計(jì)難點(diǎn)及IBM應(yīng)用解決方案

評論