1、什么是Setup 和Holdup時間? 答:Setup/hold time 是測試芯片對輸入信號和時鐘信號之間的時間要求。

建立時間是指觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間。輸入信號應提前時鐘上升沿(如上升沿有效)T時間到達芯片,這個T就是建立時間-Setup time。如不滿足setup time,這個數據就不能被這一時鐘打入觸發器,只有在下一個時鐘上升沿,數據才能被打入觸發器。

保持時間是指觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間。如果holdtime不夠,數據同樣不能被打入觸發器。

2、什么是競爭與冒險現象?解決辦法?

答:在組合邏輯中,由于門的輸入信號通路中經過了不同的延時,導致到達該門的時間不一致叫競爭。產生毛刺叫冒險。如果布爾式中有相反的信號則可能產生競爭和冒險現象。

解決方法:一是添加布爾式的消去項,二是在芯片外部加電容。三加選通信號。用D觸發器,格雷碼計數器,同步電路等優秀的設計方案可以消除。

3、如何解決亞穩態?

答:亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。

解決方法:

1 、降低系統時鐘頻率

2 、用反應更快的Flip-Flop

3 、引入同步機制,防止亞穩態傳播

4 、改善時鐘質量,用邊沿變化快速的時鐘信號

關鍵是器件使用比較好的工藝和時鐘周期的裕量要大。

4、說說靜態、動態時序模擬的優缺點

靜態時序分析是采用窮盡分析方法來提取出整個電路存在的所有時序路徑,計算信號在這些路徑上的傳播延時,檢查信號的建立和保持時間是否滿足時序要求,通過對最大路徑延時和最小路徑延時的分析,找出違背時序約束的錯誤。它不需要輸入向量就能窮盡所有的路徑,且運行速度很快、占用內存較少,不僅可以對芯片設計進行全面的時序功能檢查,而且還可利用時序分析的結果來優化設計,因此靜態時序分析已經越來越多地被用到數字集成電路設計的驗證中。

動態時序模擬就是通常的仿真,因為不可能產生完備的測試向量,覆蓋門級網表中的每一條路徑。因此在動態時序分析中,無法暴露一些路徑上可能存在的時序問題;

靜態時序分析缺點:

1、無法識別偽路徑

2、不適合異步電路

3、不能驗證功能 5、用VERILOG寫一段代碼,實現消除一個glitch。

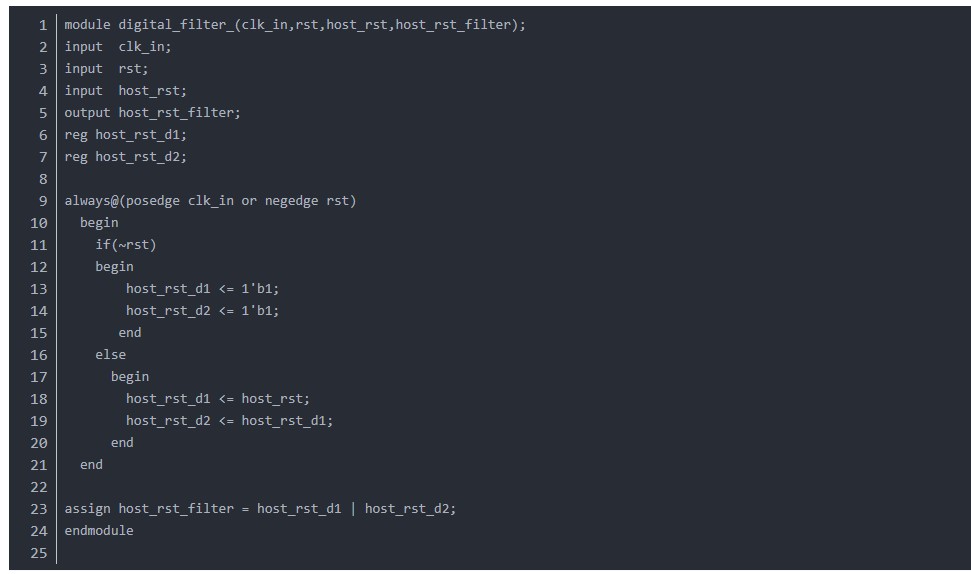

濾掉小于1個周期glitch的原理圖如下:

verilog代碼實現如下:

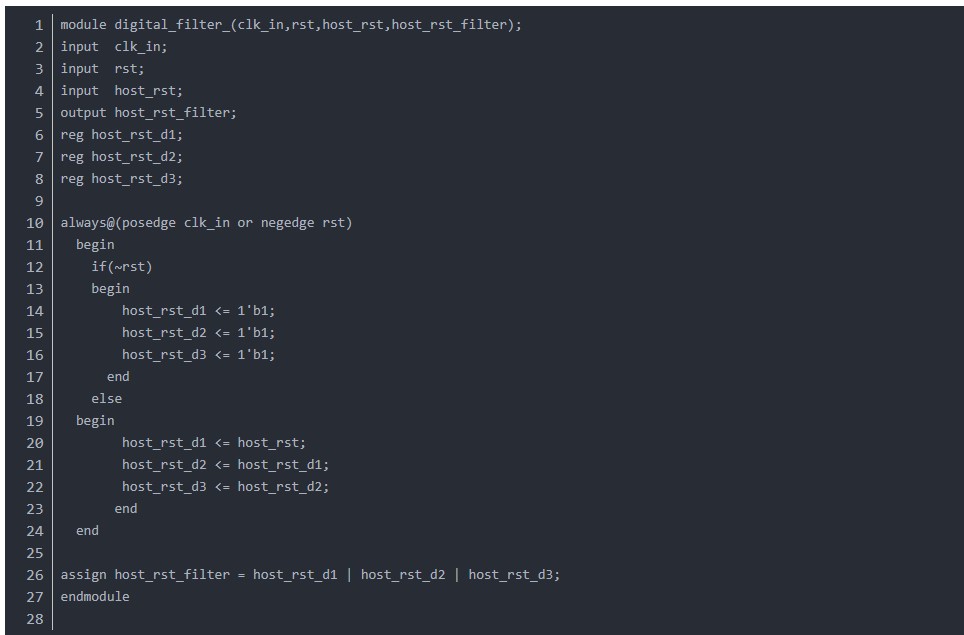

濾掉大于1個周期且小于2個周期glitch的原理圖如下:

verilog代碼實現如下:

6、簡述建立時間和保持時間 建立時間Tsu(setup):觸發器在時鐘上升沿到來之前,其數據輸入端的數據必須保持不變的最小時間。 保持時間Th(hold):觸發器在時鐘上升沿到來之后,其數據輸入端的數據必須保持不變的最小時間。

7、簡述觸發器和鎖存器之間的差別 鎖存器對電平信號敏感,在輸入脈沖的電平作用下改變狀態。 D觸發器對時鐘邊沿敏感,檢測到上升沿或下降沿觸發瞬間改變狀態。 8、計算最小周期Tco:寄存器時鐘輸入到數據輸出的時間 Tdata:寄存器間的走線延遲 Tsu :建立時間 Tskew:時鐘偏斜 最小時鐘周期:

Tmin = Tco + Tdata + Tsu - Tskew。最快頻率Fmax = 1/TminTskew = Tclkd – Tclks。

9、時鐘抖動和時鐘偏移的概念及產生原因,如何避免? 時鐘抖動jitter:指時鐘信號的跳變沿不確定,故是時鐘頻率上的不一致。 時鐘偏移Skew:指全局時鐘產生的各個子時鐘信號到達不同觸發器的時間點不同,是時鐘相位的不一致。 jitter主要受外界干擾引起,通過各種抗干擾手段可以避免。而skew由數字電路內部各路徑布局布線長度和負載不同導致,利用全局時鐘網絡可盡量將其消除。

10、同步復位和異步復位的區別

同步復位是復位信號隨時鐘邊沿觸發有效。異步復位是復位信號有效和時鐘無關。 如異步復位:

同步復位:

同步邏輯和異步邏輯的區別

同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系

同步電路和異步電路區別

同步電路有統一的時鐘源,經過PLL分頻后的時鐘驅動的模塊,因為是一個統一的時鐘源驅動,所以還是同步電路。異步電路沒有統一的時鐘源。

同步復位和異步復位的優缺點:

同步復位優點:

1、有利于仿真器的仿真

2、可以使所設計的系統100%成為同步電路,這有利于時序分析,而且綜合出來的Fmax一般較高

3、因為它只有走有效的時鐘沿到來時才有效,所有濾除了高于時鐘周期頻率的毛刺

缺點:

1、復位信號必須大于時鐘周期,才能使其真正被系統識別并完成復位任務。同時還要考慮諸如時鐘偏斜、組合邏輯路徑延遲等因素。

2、由于大部分的邏輯器件庫中的DFF都只有異步復位端口,所以采用同步復位的情況下,綜合器就會在寄存器的數據輸入端口插入組合邏輯,這樣會耗費更多的邏輯資源。

異步復位的優點:

1、大部分的邏輯器件庫中的DFF都只有異步復位端口,因此采用異步復位更省資源

2、設計相對簡單

3、異步復位信號識別方便,可以很方便的使用FPGA的全局復位端口GSR

缺點:

1、在異步復位釋放的時候容易出問題,具體來說就是:假如復位釋放時正好在時鐘有效沿附近,就很容易出現亞穩態

2、復位信號容易受毛刺影響

11、什么是線與邏輯?在硬件電路上有什么要求? 線與邏輯是指兩根線直接相連能夠實現與的功能。在硬件上需要OC門,如果不采用OC門會會導致門電路管電流過大而燒壞邏輯門。用OC門實現線與,應在輸出端口加一個上拉電阻。

12、什么是競爭冒險?如何判斷?怎么樣消除?

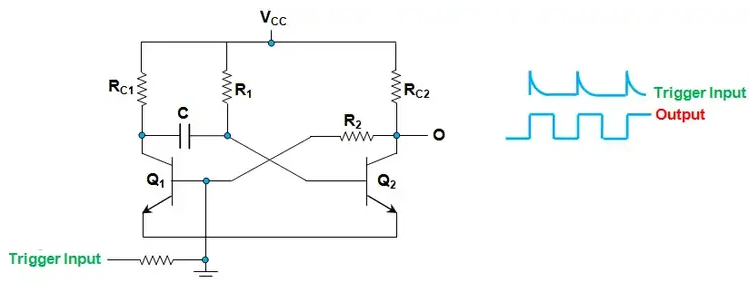

在組合邏輯電路中,同一信號經過不同的路徑到達某一匯合點的時間有先有后,這種現象稱為競爭。 由于競爭而使電路發生瞬時錯誤的現象稱為冒險。 消除方法: 1、輸出端加濾波電容。在輸出端和地直接接一個幾十皮法的電容可以吸收掉尖峰干擾脈沖。 2、加選通脈沖 3、修改邏輯設計 4、利用格雷碼每次只有一位跳變,消除了競爭冒險產生的條件。 舉例: 下面這個電路,使用了兩個邏輯門,一個非門和一個與門,本來在理想情況下F的輸出應該是一直穩定的0輸出,但是實際上每個門電路從輸入到輸出是一定會有時間延遲的,這個時間通常叫做電路的開關延遲。而且制作工藝、門的種類甚至制造時微小的工藝偏差,都會引起這個開關延遲時間的變化。

F = A & ~A

有競爭不一定產生冒險,如紅線處。有冒險一定存在競爭。

F = A & ~A

有競爭不一定產生冒險,如紅線處。有冒險一定存在競爭。

13、異步FIFO深度計算

如果數據流連續不斷則FIFO深度無論多少,只要讀寫時鐘不同源同頻則都會丟數; FIFO用于緩沖塊數據流,一般用在寫快讀慢時,FIFO深度 / (寫入速率 - 讀出速率) = FIFO被填滿時間 應大于 數據包傳送時間= 數據量 / 寫入速率例:A/D采樣率50MHz,dsp讀A/D讀的速率40MHz,要不丟失地將10萬個采樣數據送入DSP,在A/D在和DSP之間至少加多大容量(深度)的FIFO才行? 100,000 / 50MHz = 1/ 500 s = 2ms (50MHz - 40MHz)* 1/500 = 20k既是FIFO深度。

14、畫出用D觸發器實現2倍分頻的邏輯電路

將D觸發器的Q非端接到數據輸入端D即可實現二分頻,說白了就是CLK時鐘信號的一個周期Q端電平反轉一次。Q和~Q輸出的都是二分頻電路,只不過是反相的。~Q是先高后低。 四分頻電路:

15、系統最高速度計算(最快時鐘頻率)和流水線設計思想: 同步電路的速度是指同步系統時鐘的速度,同步時鐘愈快,電路處理數據的時間間隔越短,電路在單位時間內處理的數據量就愈大。假設Tco是觸發器的輸入數據被時鐘打入到觸發器到數據到達觸發器輸出端的延時時間(Tco=Tsetpup+Thold);Tdelay是組合邏輯的延時;Tsetup是D觸發器的建立時間。假設數據已被時鐘打入D觸發器,那么數據到達第一個觸發器的Q輸出端需要的延時時間是Tco,經過組合邏輯的延時時間為Tdelay,然后到達第二個觸發器的D端,要希望時鐘能在第二個觸發器再次被穩定地打入觸發器,則時鐘的延遲必須大于Tco+Tdelay+Tsetup,也就是說最小的時鐘周期Tmin =Tco+Tdelay+Tsetup,即最快的時鐘頻率Fmax =1/Tmin。FPGA開發軟件也是通過這種方法來計算系統最高運行速度Fmax。因為Tco和Tsetup是由具體的器件工藝決定的,故設計電路時只能改變組合邏輯的延遲時間Tdelay,所以說縮短觸發器間組合邏輯的延時時間是提高同步電路速度的關鍵所在。由于一般同步電路都大于一級鎖存,而要使電路穩定工作,時鐘周期必須滿足最大延時要求。故只有縮短最長延時路徑,才能提高電路的工作頻率。可以將較大的組合邏輯分解為較小的N塊,通過適當的方法平均分配組合邏輯,然后在中間插入觸發器,并和原觸發器使用相同的時鐘,就可以避免在兩個觸發器之間出現過大的延時,消除速度瓶頸,這樣可以提高電路的工作頻率。這就是所謂“流水線”技術的基本設計思想,即原設計速度受限部分用一個時鐘周期實現,采用流水線技術插入觸發器后,可用N個時鐘周期實現,因此系統的工作速度可以加快,吞吐量加大。注意,流水線設計會在原數據通路上加入延時,另外硬件面積也會稍有增加。

16、FPGA設計工程師努力的方向: SOPC、SOC,高速串行I/O,低功耗,可靠性,可測試性和設計驗證流程的優化等方面。 隨著芯片工藝的提高,芯片容量、集成度都在增加,FPGA設計也朝著高速、高度集成、低功耗、高可靠性、高可測、可驗證性發展。芯片可測、可驗證,正在成為復雜設計所必備的條件,盡量在上板之前查出bug,將發現bug的時間提前,這也是一些公司花大力氣設計仿真平臺的原因。另外隨著單板功能的提高、成本的壓力,低功耗也逐漸進入FPGA設計者的考慮范圍,完成相同的功能下,考慮如何能夠使芯片的功耗最低,據說altera、xilinx都在根據自己的芯片特點整理如何降低功耗的文檔。高速串行IO的應用,也豐富了FPGA的應用范圍,像xilinx的v2pro中的高速鏈路也逐漸被應用。

17、異步信號同步處理

對于單bit信號: 慢時鐘域到快時鐘域信號的轉換,用沿同步:

要求輸入異步信號的寬度應該有兩個快速時鐘域的時鐘周期(在快時鐘域下打兩拍,采上升沿。需要前面的限制嗎?)。 快時鐘域到慢時鐘域信號的轉換,用脈沖同步:

要求輸入異步脈沖信號之間的間隔至少要在兩個慢速時鐘的時鐘周期之上,如果小于這個值,兩個快時鐘域的單bit信號轉到慢時鐘域可能就變成了一個兩周期寬度的信號了。

18、FPGA中可以綜合實現為RAM/ROM/CAM的三種資源及其注意事項? 三種資源:BLOCK RAM,觸發器(FF),查找表(LUT); 注意事項: 1:在生成RAM等存儲單元時,應該首選BLOCK RAM 資源;其原因有二:第一:使用BLOCK RAM等資源,可以節約更多的FF和4-LUT等底層可編程單元。使用BLOCK RAM可以說是“不用白不用”,是最大程度發揮器件效能,節約成本的一種體現;第二:BLOCK RAM是一種可以配置的硬件結構,其可靠性和速度與用LUT和REGISTER構建的存儲器更有優勢。 2:弄清FPGA的硬件結構,合理使用BLOCK RAM資源; 3:分析BLOCK RAM容量,高效使用BLOCK RAM資源; 4:分布式RAM資源(DISTRIBUTE RAM) 查找表(look-up-table)簡稱為LUT,LUT本質上就是一個RAM。目前FPGA中多使用4(V7和A7都是6輸入)輸入的LUT,所以每一個LUT可以看成一個有 4位地址線的16x1的RAM。當用戶通過原理圖或HDL語言描述了一個邏輯電路以后,PLD/FPGA開發軟件會自動計算邏輯電路的所有可能的結果,并把結果事先寫入RAM,這樣,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出即可

19、HDL語言的層次概念? HDL語言是分層次的、類型的,最常用的層次概念有系統與標準級、功能模塊級,行為級,寄存器傳輸級和門級。系統級,算法級,RTL級(行為級),門級,開關級

20、IC設計前端到后端的流程和EDA工具? 設計前端也稱邏輯設計,后端設計也稱物理設計,兩者并沒有嚴格的界限,一般涉及到與工藝有關的設計就是后端設計。 1:規格制定:客戶向芯片設計公司提出設計要求。 2:詳細設計:芯片設計公司(Fabless)根據客戶提出的規格要求,拿出設計解決方案和具體實現架構,劃分模塊功能。目前架構的驗證一般基于systemC語言,對價后模型的仿真可以使用systemC的仿真工具。例如:CoCentric和Visual Elite等。 3:HDL編碼:設計輸入工具:ultra ,visual VHDL等 4:仿真驗證:modelsim 5:邏輯綜合:synplify 6:靜態時序分析:synopsys的Prime Time 7:形式驗證:Synopsys的Formality.

IC設計分為前端和后端。前端設計主要將HDL語言--》網表,后端設計是網表--》芯片版圖。 前端主要有需求分析與架構設計、RTL設計、仿真驗證、邏輯綜合、STA、形式驗證。后端主要包括DFT、布局規劃、布線以及版圖物理驗證。

21、MOORE 與 MEELEY狀態機的特征?

Moore 狀態機的輸出僅與當前狀態值有關, 且只在時鐘邊沿到來時才會有狀態變化。 Mealy 狀態機的輸出不僅與當前狀態值有關, 而且與當前輸入值有關。

22、說說靜態、動態時序模擬的優缺點? 靜態時序分析是采用窮盡分析方法來提取出整個電路存在的所有時序路徑,計算信號在這些路徑上的傳播延時,檢查信號的建立和保持時間是否滿足時序要求,通過對最大路徑延時和最小路徑延時的分析,找出違背時序約束的錯誤。它不需要輸入向量就能窮盡所有的路徑,且運行速度很快、占用內存較少,不僅可以對芯片設計進行全面的時序功能檢查,而且還可利用時序分析的結果來優化設計,因此靜態時序分析已經越來越多地被用到數字集成電路設計的驗證中。 動態時序模擬就是通常的仿真,因為不可能產生完備的測試向量,覆蓋門級網表中的每一條路徑。因此在動態時序分析中,無法暴露一些路徑上可能存在的時序問題;

23、FPGA內部結構及資源: FPGA主要由可編程單元、可編程I/O單元及布線資源構成。 可編程邏輯單元(可配置邏輯單元,CLB)由兩個SLICE構成,SLICE主要包括實現組合邏輯的LUT和實現時序邏輯的觸發器。FPGA內部還包含專用存儲單元BRAM,運算單元DSP Slice,及專用內嵌功能單元,如:PLL、Serdes等。

24、名詞解釋,寫出下列縮寫的中文(或者英文)含義: FPGA :Field Programmable Gate Array 現場可編程門陣列 VHDL:( Very-High-Speed Integrated Circuit Hardware Description Language) 甚高速集成電路硬件描述語言 HDL :Hardware Description Language硬件描述語言 EDA:Electronic Design Automation 電子設計自動化 CPLD:Complex Programmable Logic Device 復雜可編程邏輯器件 PLD :Programmable Logic Device 可編程邏輯器件 GAL:generic array logic 通用陣列邏輯 LAB:Logic Array Block 邏輯陣列塊 CLB :Configurable Logic Block 可配置邏輯模塊 EAB: Embedded Array Block 嵌入式陣列塊 SOPC: System-on-a-Programmable-Chip可編程片上系統 LUT :Look-Up Table 查找表 JTAG: Joint Test Action Group 聯合測試行為組織 IP: Intellectual Property 知識產權 ASIC :Application Specific Integrated Circuits 專用集成電路 ISP :In System Programmable 在系統可編程 ICR :In Circuit Re-config 在電路可重構 RTL: Register Transfer Level 寄存器傳輸級

25、FPGA內部LUT實現組合邏輯的原理: LUT相當于存放邏輯表達式對應真值表的RAM。軟件將邏輯表達式所有可能結果列出后存放在RAM中,輸入作為RAM地址,輸出為邏輯運算結果。如使用LUT模擬二輸入“與”邏輯。列出真值表:00 – 0,01 – 0,10 – 0,11 – 1。此時將00 01 10 11作為地址線,依次將結果0 0 0 1存放在RAM中。當輸入00時及輸出0&0=0.

26、 低功耗技術: 功耗可用公式描述:Power = KFCV^2,即功率等于常數系數工作頻率負載電容值*電壓的平方。 故從以下幾個方面降低功耗方式: a.控制工作頻率:降低頻率增大數據路徑寬度,動態頻率調整,門控時鐘(時鐘使能有效時鐘才進入寄存器時鐘輸入引腳) b.減少電容負載:使用幾何尺寸更小的邏輯門,其電容負載較小,功率也隨之減少。 c.降低工作電壓:動態改變工作電壓、零操作電壓(直接關閉系統中一部分的電源)

27、MOS管基本概念及畫圖: MOS中文意思是金屬氧化物半導體場效應管,由柵極(G)、漏級(D)、源級(S)組成。分為PMOS和NMOS兩種類型,區別在于G級高電平時,N型管導通,P型管截止。兩者往往是成對出現的,即CMOS。只要一只導通,另一只則不導通,現代單片機主要是采用CMOS工藝制成的。 畫圖一般需要根據一個簡單的邏輯表達式,畫出CMOS電路圖結構。需要掌握常用邏輯門的實現方式。

‘

總體來看還是挺好記的,與非門和或非門都是上下各兩個MOS管,且上面是PMOS,下面是NMOS。不同之處在于與非是“上并下串”,或非是“上串下并”。

28、FPGA詳細設計流程(面試提問) 與數字IC設計流程類似,以xilinx vivado工具為例,主要有以下步驟:系統規劃、RTL輸入、行為仿真、邏輯綜合、綜合后仿真(可選)、綜合后設計分析(時序及資源)、設計實現(包括布局布線及優化)、實現后設計分析(時序及資源)、板級調試、bitstream固化。

29、時序約束相關有哪幾種時序路徑:

input paths:外部引腳到內部寄存器 register-to-register paths:系統內部寄存器到寄存器路徑 output paths:內部寄存器到外部引腳的路徑 port to port paths:FPGA輸入端口到輸出端口路徑(不常用)

30、創建時序約束的關鍵步驟: baseline約束:create clocksdefine clocks interactions I/O約束:set input and output delays 例外約束:set timing execptions(set_max_delay/set_min_delay、set_multicycle_path、set_false_path) 設計初期可先不加I/O約束,但baseline約束要盡早建立。

31、 SRAM和DRAM的區別 SRAM是靜態隨機訪問存儲器,由晶體管存儲數據,無需刷新,讀寫速度快。DRAM是動態隨機訪問存儲器,由電容存儲數據,由于電容漏電需要動態刷新,電容充放電導致讀寫速度較SRAM低。但DRAM成本較低,適合做大容量片外緩存。

32、CMOS和TTL電路區別是什么? 兩者區別主要體現在三個方面: 結構:CMOS電路由場效應管構成,TTL由雙極性晶體管構成。 電平范圍:CMOS邏輯電平范圍大(5~15V),TTL只工作在5V以下,因此CMOS噪聲容限比TTL大,抗干擾能力強。 功耗與速率:CMOS的功耗比TTL小,但工作頻率低于TTL。

TTL不能直接驅動CMOS電平,需要加上拉電阻,而CMOS可以直接驅動TTL

33、JTAG接口信號及功能 JTAG實際上使用的只有四個信號:時鐘TCK、狀態機控制信號TMS、數據輸入信號TDI、數據輸出信號TDO。

34、上拉電阻用途: 1、當 TTL 電路驅動 COMS 電路時,如果 TTL 電路輸出的高電平低于 COMS 電路的最低 高電平 (一般為 3.5V ) , 這時就需要在 TTL 的輸出端接上拉電阻, 以提高輸出高電平的值。 2、 OC 門電路必須加上拉電阻,以提高輸出的高 電平值。 3、為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻。 4、在 COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產生降低輸入阻抗,提供泄荷通路。 5、芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。 6、提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。 7、長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾

35、有四種復用方式,頻分多路復用,寫出另外三種 四種復用方式:頻分多路復用( FDMA ),時分多路復用( TDMA ),碼分多路復用(CDMA ),波分多路復用( WDM A) 。

36、基爾霍夫定理的內容 基爾霍夫定律包括電流定律和電壓定律: 電流定律:在集總電路中, 在任一瞬時, 流向某一結點的電流之和恒等于由該結點流出的電流之和 。 電壓定律:在集總電路中,在任一瞬間, 沿電路中的任一回路繞行一周,在該回路上電動勢之和恒等于各電阻上的電壓降之和

37、三段式狀態機 一段式: 只有一個always block,把所有的邏輯(輸入、輸出、狀態)都在一個always block的時序邏輯中實現。這種寫法看起來很簡潔,但是不利于維護,如果狀態復雜一些就很容易出錯,不推薦這種方法。

在簡單的狀態機可以使用。

二段式: 有兩個always block,把時序邏輯和組合邏輯分隔開來。時序邏輯里進行當前狀態和下一狀態的切換,組合邏輯實現各個輸入、輸出以及狀態判斷。這種寫法不僅便于閱讀、理解、維護,而且利于綜合器優化代碼,利于用戶添加合適的時序約束條件,利于布局布線器實現設計。在兩段式描述中,當前狀態的輸出用組合邏輯實現,可能存在競爭和冒險,產生毛刺。

要求對狀態機的輸出用寄存器打一拍,但很多情況不允許插入寄存器節拍,此時使用三段式描述。其優勢在于能夠根據狀態轉移規律,在上一狀態根據輸入條件判斷出當前狀態的輸出,從而不需要額外插入時鐘節拍。 三段式: 有三個always block,一個時序邏輯采用同步時序的方式描述狀態轉移,一個采用組合邏輯的方式判斷狀態轉移條件、描述狀態轉移規律,第三個模塊使用同步時序的方式描述每個狀態的輸出。代碼容易維護,時序邏輯的輸出解決了兩段式組合邏輯的毛刺問題,但是從資源消耗的角度上看,三段式的資源消耗多一些。 二段式和三段式的區別主要是每個狀態的輸出使用組合邏輯還是用時序邏輯,組合邏輯實現,可能存在競爭和冒險,產生毛刺。

38、什么是狀態圖? 狀態圖是以幾何圖形的方式來描述時序邏輯電路的狀態轉移規律以及輸出與輸入的關系。

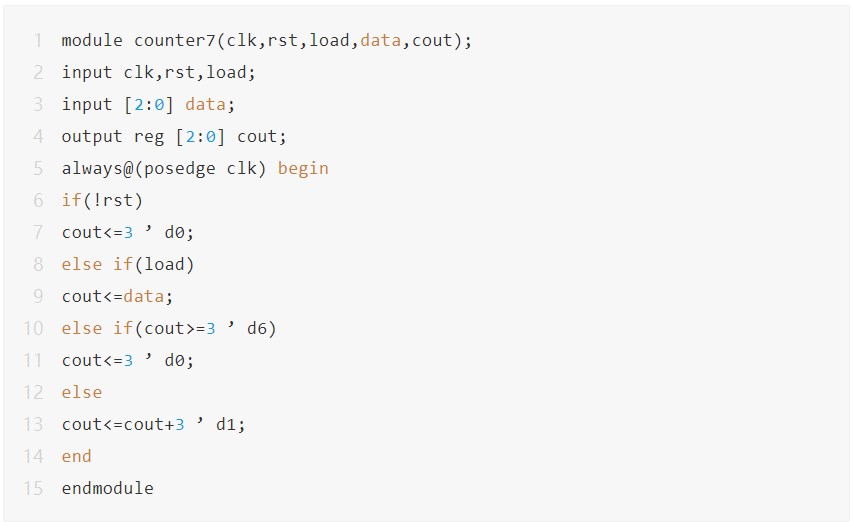

39、用你熟悉的設計方式設計一個可預置初值的 7 進制循環計數器 ,15 進制的呢?

40、你所知道的可編程邏輯器件有哪些?

PAL , PLA , GAL , CPLD , FPGA

41、SRAM,FALSH MEMORY,DRAM , SSRAM及 SDRAM的區別 ? SRAM :靜態隨機存儲器,存取速度快,但容量小,掉電后數據會丟失,不像DRAM需要不停的 REFRESH ,制造成本較高,通常用來作為快取(CACHE)記憶體使用。

FLASH :閃存,存取速度慢,容量大,掉電后數據不會丟失

DRAM :動態隨機存儲器,必須不斷的重新的加強 (REFRESHED) 電位差量,否則電位差將降低至無法有足夠的能量表現每一個記憶單位處于何種狀態。價格比 SRAM 便宜,但訪問速度較慢,耗電量較大,常用作計算機的內存使用。

SSRAM :即同步靜態隨機存取存儲器。對于 SSRAM 的所有訪問都在時鐘的上升 /下降沿啟動。地址、數據輸入和其它控制信號均于時鐘信號相關。

SDRAM :即同步動態隨機存取存儲器。

42、有源濾波器和無源濾波器的區別

無源濾波器:這種電路主要有無源元件 R、 L 和 C組成

有源濾波器:集成運放和 R、C 組成,具有不用電感、體積小、重量輕等優點。集成運放的開環電壓增益和輸入阻抗均很高, 輸出電阻小, 構成有源濾波電路后還具有一定的電壓放大和緩沖作用。但集成運放帶寬有限, 所以目前的有源濾波電路的工作 頻率難以做得很高。

43. 什么是同步邏輯和異步邏輯? 同步時序邏輯電路的特點:各觸發器的時鐘端全部連接在一起,并接在系統 時鐘端,只有當時鐘脈沖到來時,電路的狀態才能改變。改變后的狀態將一直保持到下一個時鐘脈沖的到來,此時無論外部輸入有無變化,狀態表中的每個狀態都是穩定的。 異步時序邏輯電路的特點: 電路中除可以使用帶時鐘的觸發器外,還可以使用不帶 時鐘的觸發器和延遲元件作為存儲元件,電路中沒有統一的時鐘,電路狀態的改變由外 部輸入的變化直接引起。 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。

44. 同步復位和異步復位的區別 同步復位是在時鐘沿變化時,完成復位動作。 優點: 1)抗干擾能力高,可以提出復位信號中周期短于時鐘周期的毛刺; 2)有利于靜態時序分析工具的分析; 3)有利于基于周期的仿真工具的仿真。 缺點: 1)占用更多資源; 2)對復位信號的脈沖寬度有要求,由于線路上的延遲;可能需要多個時鐘周期的復位脈沖的寬度,而且很難保證復位信號到達各個寄存器的時序; 3)同步復位依賴時鐘,如果電路中時鐘信號出現問題則無法復位。 異步復位是只要復位信號滿足條件就完成復位動作。 優點: 1)不需要額外的邏輯資源,實現簡單; 2)復位信號不依賴于時鐘。 缺點: 1)復位信號易受外界干擾,并對電路內的毛刺敏感; 2)復位信號的隨機性可能導致時序違規,也就是復位信號釋放時在時鐘有效沿附近,會使電路處于亞穩態。

45. FPGA芯片內有哪兩種儲存器資源? FPGA 芯片內有兩種存儲器資源:一種叫block ram,另一種是由 LUT 配置成的內部存儲器(也就是分布式ram)。Blockram由一定數量固定大小的存儲塊構成的,使用BLOCK RAM資源不占用額外的邏輯資源,并且速度快。但是使用的時候消耗BLOCKRAM的資源是其塊大小的整數倍。

46. 什么是競爭與冒險現象?怎樣判斷?怎樣消 除? 競爭:在組合邏輯中,由于門的輸入信號通路 中經過了不同的延時,導致到達該門的時間不一致叫競爭。 冒險: 由于競爭而使電路輸出發生瞬時錯誤的現象叫做冒險。(也就是由于競爭產生的毛刺叫做冒險) 判斷方法: 1)代數法:如果布爾式中有相反的信號則很有可能產生競爭和冒險現象; 2)圖形法:有兩個相切的卡諾圈并且相切處沒有被其他卡諾圈包圍,就有可能出現競爭和冒險現象; 3)實驗法:使用示波器觀測。 解決方法: 1)加濾波電路,消除毛刺影響; 2)加選通信號,避開毛刺; 3)增減冗余項消除邏輯冒險。

責任編輯:lq6

-

電容

+關注

關注

100文章

6050瀏覽量

150423 -

Setup

+關注

關注

0文章

30瀏覽量

12005

原文標題:面試中經常會遇到的FPGA基本概念,你會幾個?

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

單穩態觸發器穩態是什么狀態的

單穩態觸發器暫穩態由什么來維持

單穩態觸發器的暫態時間取決于什么

單穩態觸發器有幾個穩態幾個暫穩態

改善系統穩態精度的途徑有哪些

減小系統穩態誤差的方法有哪些?

安裝esp-idf-tools-setup-offline-5.1.2.exe到結尾運行python時顯示應用程序無法正常啟動如何解決?

數字電路中的亞穩態是什么

單穩態多諧振蕩器電路圖分享

什么是Setup和Holdup時間?如何解決亞穩態?

什么是Setup和Holdup時間?如何解決亞穩態?

評論