FPGA是在PAL、GAL、EPLD、CPLD等可編程器件的基礎上進一步發展的產物。它是作為ASIC領域中的一種半定制電路而出現的,即解決了定制電路的不足,又克服了原有可編程器件門電路有限的缺點。

由于FPGA需要被反復燒寫,它實現組合邏輯的基本結構不可能像ASIC那樣通過固定的與非門來完成,而只能采用一種易于反復配置的結構。查找表可以很好地滿足這一要求,目前主流FPGA都采用了基于SRAM工藝的查找表結構,也有一些軍品和宇航級FPGA采用Flash或者熔絲與反熔絲工藝的查找表結構。通過燒寫文件改變查找表內容的方法來實現對FPGA的重復配置。

根據數字電路的基本知識可以知道,對于一個n輸入的邏輯運算,不管是與或非運算還是異或運算等等,最多只可能存在2n種結果。所以如果事先將相應的結果存放于一個存貯單元,就相當于實現了與非門電路的功能。FPGA的原理也是如此,它通過燒寫文件去配置查找表的內容,從而在相同的電路情況下實現了不同的邏輯功能。

查找表(Look-Up-Table)簡稱為LUT,LUT本質上就是一個RAM。目前FPGA中多使用4輸入的LUT,所以每一個LUT可以看成一個有4位地址線的 的RAM。當用戶通過原理圖或HDL語言描述了一個邏輯電路以后,PLD/FPGA開發軟件會自動計算邏輯電路的所有可能結果,并把真值表(即結果)事先寫入RAM,這樣,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出即可。

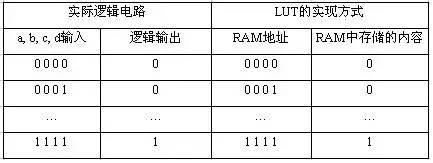

下面給出一個4與門電路的例子來說明LUT實現邏輯功能的原理。

例1-1:給出一個使用LUT實現4輸入與門電路的真值表。

表1-1 4輸入與門的真值表

從中可以看到,LUT具有和邏輯電路相同的功能。實際上,LUT具有更快的執行速度和更大的規模。

由于基于LUT的FPGA具有很高的集成度,其器件密度從數萬門到數千萬門不等,可以完成極其復雜的時序與邏輯組合邏輯電路功能,所以適用于高速、高密度的高端數字邏輯電路設計領域。其組成部分主要有可編程輸入/輸出單元、基本可編程邏輯單元、內嵌SRAM、豐富的布線資源、底層嵌入功能單元、內嵌專用單元等,主要設計和生產廠家有Xilinx、Altera、Lattice、Actel、Atmel和QuickLogic等公司,其中最大的是Xilinx、Altera、Lattice三家。

如前所述,FPGA是由存放在片內的RAM來設置其工作狀態的,因此工作時需要對片內RAM進行編程。用戶可根據不同的配置模式,采用不同的編程方式。FPGA有如下幾種配置模式:

并行模式:并行PROM、Flash配置FPGA;

主從模式:一片PROM配置多片FPGA;

串行模式:串行PROM配置FPGA;

外設模式:將FPGA作為微處理器的外設,由微處理器對其編程。

目前,FPGA市場占有率最高的兩大公司Xilinx和Altera生產的FPGA都是基于SRAM工藝的,需要在使用時外接一個片外存儲器以保存程序。上電時,FPGA將外部存儲器中的數據讀入片內RAM,完成配置后,進入工作狀態;掉電后FPGA恢復為白片,內部邏輯消失。這樣FPGA不僅能反復使用,還無需專門的FPGA編程器,只需通用的EPROM、PROM編程器即可。Actel、QuickLogic等公司還提供反熔絲技術的FPGA,只能下載一次,具有抗輻射、耐高低溫、低功耗和速度快等優點,在軍品和航空航天領域中應用較多,但這種FPGA不能重復擦寫,開發初期比較麻煩,費用也比較昂貴。Lattice是ISP技術的發明者,在小規模PLD應用上有一定的特色。早期的Xilinx產品一般不涉及軍品和宇航級市場,但目前已經有Q Pro-R等多款產品進入該類領域。

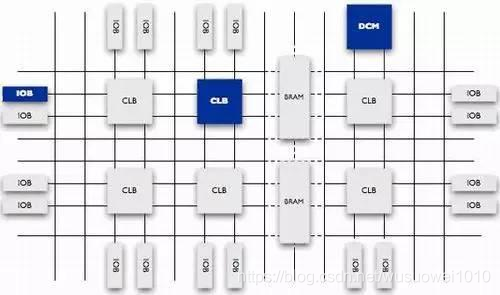

一、 FPGA芯片結構 目前主流的FPGA仍是基于查找表技術的,已經遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、時鐘管理和DSP)的硬核(ASIC型)模塊。如圖1-1所示(注:圖1-1只是一個示意圖,實際上每一個系列的FPGA都有其相應的內部結構),FPGA芯片主要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內嵌的底層功能單元和內嵌專用硬件模塊。

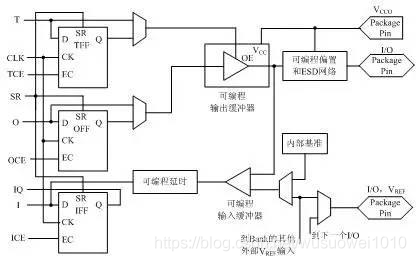

圖1-1 FPGA芯片的內部結構 每個模塊的功能如下:1可編程輸入輸出單元(IOB)可編程輸入/輸出單元簡稱I/O單元,是芯片與外界電路的接口部分,完成不同電氣特性下對輸入/輸出信號的驅動與匹配要求,其示意結構如圖1-2所示。FPGA內的I/O按組分類,每組都能夠獨立地支持不同的I/O標準。通過軟件的靈活配置,可適配不同的電氣標準與I/O物理特性,可以調整驅動電流的大小,可以改變上、下拉電阻。目前,I/O口的頻率也越來越高,一些高端的FPGA通過DDR寄存器技術可以支持高達2Gbps的數據速率。

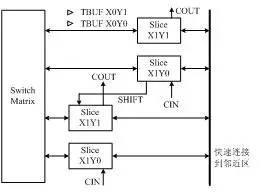

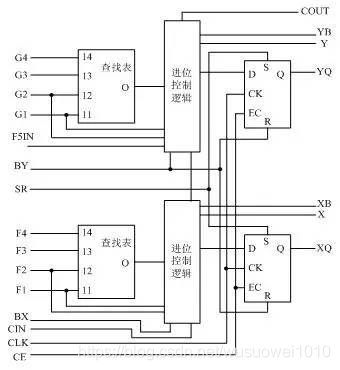

圖1-2 典型的IOB內部結構示意圖 外部輸入信號可以通過IOB模塊的存儲單元輸入到FPGA的內部,也可以直接輸入FPGA 內部。當外部輸入信號經過IOB模塊的存儲單元輸入到FPGA內部時,其保持時間(Hold Time)的要求可以降低,通常默認為0。 為了便于管理和適應多種電器標準,FPGA的IOB被劃分為若干個組(bank),每個bank的接口標準由其接口電壓VCCO決定,一個bank只能有一種VCCO,但不同bank的VCCO可以不同。只有相同電氣標準的端口才能連接在一起,VCCO電壓相同是接口標準的基本條件。 2可配置邏輯塊(CLB)CLB是FPGA內的基本邏輯單元。CLB的實際數量和特性會依器件的不同而不同,但是每個CLB都包含一個可配置開關矩陣,此矩陣由4或6個輸入、一些選型電路(多路復用器等)和觸發器組成。開關矩陣是高度靈活的,可以對其進行配置以便處理組合邏輯、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構成,如圖1-3所示。每個CLB模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為分布式RAM和分布式ROM。

圖1-3 典型的CLB結構示意圖 Slice是Xilinx公司定義的基本邏輯單位,其內部結構如圖1-4所示,一個Slice由兩個4輸入的函數、進位邏輯、算術邏輯、存儲邏輯和函數復用器組成。算術邏輯包括一個異或門(XORG)和一個專用與門(MULTAND),一個異或門可以使一個Slice實現2bit全加操作,專用與門用于提高乘法器的效率;進位邏輯由專用進位信號和函數復用器(MUXC)組成,用于實現快速的算術加減法操作;4輸入函數發生器用于實現4輸入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的兩個輸入函數為6輸入,可以實現6輸入LUT或64比特移位寄存器);進位邏輯包括兩條快速進位鏈,用于提高CLB模塊的處理速度。

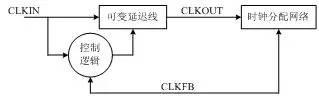

圖1-4 典型的4輸入Slice結構示意圖 3數字時鐘管理模塊(DCM)業內大多數FPGA均提供數字時鐘管理(Xilinx的全部FPGA均具有這種特性)。Xilinx推出最先進的FPGA提供數字時鐘管理和相位環路鎖定。相位環路鎖定能夠提供精確的時鐘綜合,且能夠降低抖動,并實現過濾功能。 4嵌入式塊RAM(BRAM)大多數FPGA都具有內嵌的塊RAM,這大大拓展了FPGA的應用范圍和靈活性。塊RAM可被配置為單端口RAM、雙端口RAM、內容地址存儲器(CAM)以及FIFO等常用存儲結構。RAM、FIFO是比較普及的概念,在此就不冗述。CAM存儲器在其內部的每個存儲單元中都有一個比較邏輯,寫入CAM中的數據會和內部的每一個數據進行比較,并返回與端口數據相同的所有數據的地址,因而在路由的地址交換器中有廣泛的應用。除了塊RAM,還可以將FPGA中的LUT靈活地配置成RAM、ROM和FIFO等結構。在實際應用中,芯片內部塊RAM的數量也是選擇芯片的一個重要因素。 單片塊RAM的容量為18k比特,即位寬為18比特、深度為1024,可以根據需要改變其位寬和深度,但要滿足兩個原則:首先,修改后的容量(位寬 深度)不能大于18k比特;其次,位寬最大不能超過36比特。當然,可以將多片塊RAM級聯起來形成更大的RAM,此時只受限于芯片內塊RAM的數量,而不再受上面兩條原則約束。 5豐富的布線資源布線資源連通FPGA內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類是全局布線資源,用于芯片內部全局時鐘和全局復位/置位的布線;第二類是長線資源,用以完成芯片Bank間的高速信號和第二全局時鐘信號的布線;第三類是短線資源,用于完成基本邏輯單元之間的邏輯互連和布線;第四類是分布式的布線資源,用于專有時鐘、復位等控制信號線。 在實際中設計者不需要直接選擇布線資源,布局布線器可自動地根據輸入邏輯網表的拓撲結構和約束條件選擇布線資源來連通各個模塊單元。從本質上講,布線資源的使用方法和設計的結果有密切、直接的關系。 6底層內嵌功能單元內嵌功能模塊主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等軟處理核(Soft Core)。現在越來越豐富的內嵌功能單元,使得單片FPGA成為了系統級的設計工具,使其具備了軟硬件聯合設計的能力,逐步向SOC平臺過渡。 DLL和PLL具有類似的功能,可以完成時鐘高精度、低抖動的倍頻和分頻,以及占空比調整和移相等功能。Xilinx公司生產的芯片上集成了DLL,Altera公司的芯片集成了PLL,Lattice公司的新型芯片上同時集成了PLL和DLL。PLL 和DLL可以通過IP核生成的工具方便地進行管理和配置。DLL的結構如圖1-5所示。

圖1-5 典型的DLL模塊示意圖

二、內嵌專用硬核

內嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA處理能力強大的硬核(Hard Core),等效于ASIC電路。為了提高FPGA性能,芯片生產商在芯片內部集成了一些專用的硬核。例如:為了提高FPGA的乘法速度,主流的FPGA中都集成了專用乘法器;為了適用通信總線與接口標準,很多高端的FPGA內部都集成了串并收發器(SERDES),可以達到數十Gbps的收發速度。 Xilinx公司的高端產品不僅集成了Power PC系列CPU,還內嵌了DSP Core模塊,其相應的系統級設計工具是EDK和Platform Studio,并依此提出了片上系統(System on Chip)的概念。通過PowerPC、Miroblaze、Picoblaze等平臺,能夠開發標準的DSP處理器及其相關應用,達到SOC的開發目的。 軟核、硬核以及固核的概念IP(Intelligent Property)核是具有知識產權核的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC階段,IP核設計已成為ASIC電路設計公司和FPGA提供商的重要任務,也是其實力體現。對于FPGA開發軟件,其提供的IP核越豐富,用戶的設計就越方便,其市場占用率就越高。目前,IP核已經變成系統設計的基本單元,并作為獨立設計成果被交換、轉讓和銷售。 從IP核的提供方式上,通常將其分為軟核、硬核和固核這3類。從完成IP核所花費的成本來講,硬核代價最大;從使用靈活性來講,軟核的可復用使用性最高。 1 軟核軟核在EDA設計領域指的是綜合之前的寄存器傳輸級(RTL)模型;具體在FPGA設計中指的是對電路的硬件語言描述,包括邏輯描述、網表和幫助文檔等。軟核只經過功能仿真,需要經過綜合以及布局布線才能使用。其優點是靈活性高、可移植性強,允許用戶自配置;缺點是對模塊的預測性較低,在后續設計中存在發生錯誤的可能性,有一定的設計風險。軟核是IP核應用最廣泛的形式。 2 固核固核在EDA設計領域指的是帶有平面規劃信息的網表;具體在FPGA設計中可以看做帶有布局規劃的軟核,通常以RTL代碼和對應具體工藝網表的混合形式提供。將RTL描述結合具體標準單元庫進行綜合優化設計,形成門級網表,再通過布局布線工具即可使用。和軟核相比,固核的設計靈活性稍差,但在可靠性上有較大提高。目前,固核也是IP核的主流形式之一。 3 硬核硬核在EDA設計領域指經過驗證的設計版圖;具體在FPGA設計中指布局和工藝固定、經過前端和后端驗證的設計,設計人員不能對其修改。不能修改的原因有兩個:首先是系統設計對各個模塊的時序要求很嚴格,不允許打亂已有的物理版圖;其次是保護知識產權的要求,不允許設計人員對其有任何改動。IP硬核的不許修改特點使其復用有一定的困難,因此只能用于某些特定應用,使用范圍較窄。

責任編輯:lq6

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603013 -

cpld

+關注

關注

32文章

1248瀏覽量

169336

原文標題:FPGA的工作原理,一篇全掌握!

文章出處:【微信號:EngicoolArabic,微信公眾號:電子工程技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一文讀懂RFID技術的工作原理及技術參數

【古瑞瓦特光伏逆變器品牌】一文讀懂PCS儲能變流器

一文讀懂FPGA的工作原理

一文讀懂FPGA的工作原理

評論