在現(xiàn)代汽車電子中,一般有多個微控制器共同協(xié)調(diào)工作。DSP控制器采用哈佛結構,運算速度快,所以在汽車電子中廣泛采用DSP芯片來實現(xiàn)汽車動力系統(tǒng)的控制。ARM是一種32位微控制器,有豐富的外擴接口,因此在汽車電子中一般用ARM來實現(xiàn)大容最的數(shù)據(jù)存儲和人機交互或GPS全球定位系統(tǒng),故在DSP和ARM之間需要進行數(shù)據(jù)交換。

CPLD(Complex Programmable Logic Device)是一種復雜的用戶可編程邏輯器件,由于采用硬件可編程技術,從而使沒計硬件電路也像設計軟件一樣方便。DSP2407A是T1公司設計的一款專為滿足大范圍的數(shù)字電動機控制應用的微控制器。S3C4480是三星公司專為手持設備設計的高性價比的微控制器。本設計以Xilinx公司的XC95108為例,通過在CPLD中開辟2塊獨立的SRAM區(qū)域(各1字節(jié))來實現(xiàn)DSP2407A與S3C4480的并行通信。采用這種通信方式,數(shù)據(jù)傳輸準確、高速,基本可以滿足DSP2407A與S3C4480總線接口實時通信的要求,從而將整車動力控制和人機交互有機地統(tǒng)一起來。

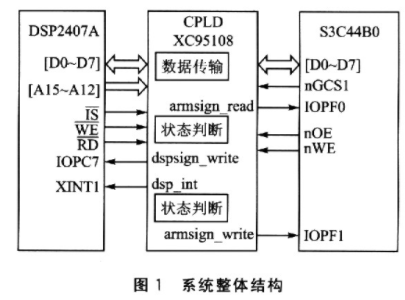

1 整體系統(tǒng)結構設計

DSP2407A負責采集汽車所有的數(shù)據(jù),再將數(shù)據(jù)通過CPLD發(fā)給S3C44B0進行數(shù)據(jù)存儲和人機交互。有時S3C4480要接收觸摸屏命令,命令也通過CPLD發(fā)給DSP2407A控制器,從而控制整臺汽車的動作。對DSP2407A,要及時響應由S3C44B0發(fā)過來的命令;而對于S3C4480,要隨時接收DSP2407A送來的數(shù)據(jù),這樣,雙方通信的實時性就要很強。因此在系統(tǒng)設計中,DSP2407A用中斷方式接收數(shù)據(jù),S3C44BO用查詢方式接收數(shù)據(jù)。

在DSP2407A中,[DO~D7]是數(shù)據(jù)線,[A15~A12]是地址線,IS是I/0空間選通引腳,當訪問外部的存儲器或I/O空間時為低電平。WE是寫使能,RD是讀使能。IOPC7足通用I/O引腳,用來判斷DSP2407A是否可以往CPLD寫數(shù)據(jù)。當IOPC7為低電平時,代表DSP2407A可以往CPLD中寫數(shù)據(jù);若為高電平,則表示CPLD中已有數(shù)據(jù),這時DSP2407A不能往CPLD中寫數(shù)據(jù)。XINT1是外部中斷,用來通知DSP2407A準備讀取CPLD中的數(shù)據(jù)。

在CPLD中,用l片XC95l08來實現(xiàn)。XC95108共有108個宏單元,有足夠的空間來實現(xiàn)2個8位的SRAM區(qū);主要用來實現(xiàn)DSP2407A和S3C44B0之間的數(shù)據(jù)交換,沒置DSP2407A和S3C44B0讀/寫控制的狀態(tài)位。在S3C44B0中’[D0~D7]是數(shù)據(jù)線,nGCSl是芯片選擇信號,當存儲器地址在相應段的地址區(qū)域時芯片被激活。nWE是寫允許信號,nOE是讀允許信號。IOPF0是通用I/O口,用來監(jiān)視可否從CPLD中讀取數(shù)據(jù):當它為高電平時,代表CPLD中有數(shù)據(jù),可以讀取數(shù)據(jù);當它為低電平時。表示CPLD中無數(shù)據(jù)可讀取。IOPF1是通用I/O口,用來監(jiān)視可否向CPLD中寫數(shù)據(jù):當它為高電平時,代表CPLD中無數(shù)據(jù),可以向CPLD中寫數(shù)據(jù);當它為低電平時,代表CPLD中已有數(shù)據(jù),S3C44B0不能向CPLD中寫數(shù)據(jù)。系統(tǒng)結構如圖1所示。

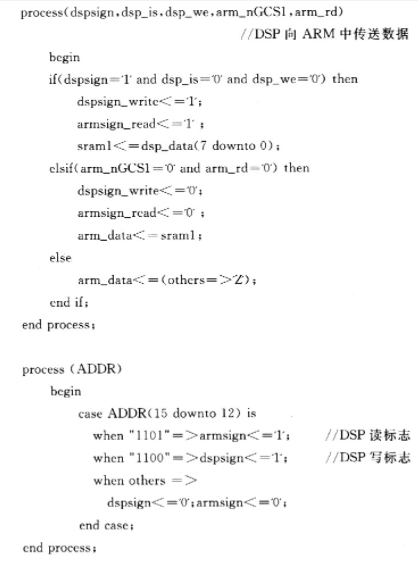

2 CPLD的設計

采用Xilinx ISE8.1為設計工具,用國際上通用的VHDL語言來編寫源程序。

2.1 8位數(shù)據(jù)從DSP中傳送到ARM中

當[A15~A12]是1100時,DSP2407A開始向CPLD中寫數(shù)據(jù),并置dspsign_write和armsign_read為1;表示CPLD中已經(jīng)有數(shù)據(jù)了,通知S3C4480可以讀取數(shù)據(jù)和DSP2407A暫時不能向CPLD中寫數(shù)據(jù);同時將數(shù)據(jù)寫入鎖存器sraml中。

當ARM發(fā)出讀取數(shù)據(jù)信號,開始將數(shù)據(jù)從sraml中讀出,并且置dspsign_write和armsign_read為0時,表示CPLD中沒有數(shù)據(jù)了,DSP2407A可以向CPLD中重新寫數(shù)據(jù)。

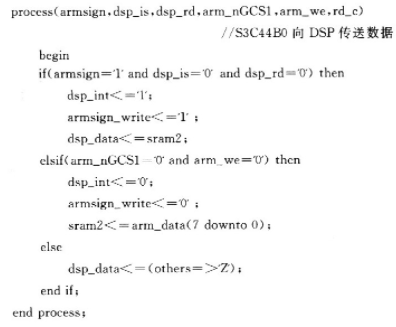

2.2 8位數(shù)據(jù)從83CA480中傳送到DSP2407A中

當S3C4480向CPLD寫數(shù)據(jù)時,將數(shù)據(jù)寫入到鎖存器sram2中,同時置dsp_int為0,通知DSP2407A產(chǎn)生一個外部中斷,可以從CPLD中取數(shù)據(jù);置armsign_write為0,表示CPLD中已有數(shù)據(jù),S3C4480不能再向CPLD中寫數(shù)據(jù)。

當[A15~12]是1101時,DSP2407A向CPLD中發(fā)出一個讀取信號,數(shù)據(jù)從鎖存器sram2傳送給DSP2407A中,并且置dsp_int為1,armsign_write為l,表示數(shù)據(jù)已被DSP2407A讀走,S3C4480可以繼續(xù)向CPLD中寫數(shù)據(jù)。

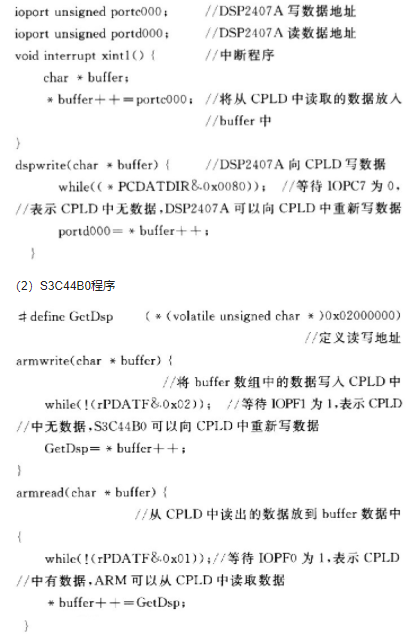

3 S3C4480和DSP2407A通信軟件設計

在本程序中,DSP2407A采用中斷方式接收數(shù)據(jù),S3C4480采用查詢端口方式接收數(shù)據(jù)。

(1)DSP2407A程序

責任編輯:gt

-

芯片

+關注

關注

455文章

50714瀏覽量

423136 -

cpld

+關注

關注

32文章

1248瀏覽量

169333 -

通信系統(tǒng)

+關注

關注

6文章

1187瀏覽量

53325

發(fā)布評論請先 登錄

相關推薦

FPGA+DSP+ARM開發(fā)板

什么是基于FPGA的ARM并行總線?

怎么實現(xiàn)ARM/DSP雙核系統(tǒng)的通信接口的設計?

如何用CPLD實現(xiàn)DSP2407A與S3C4480的通信?

如何實現(xiàn)arm與多DSP之間的通信問題呢求解

XC9572和XC95108 DIY CPLD實驗板的PCB

在HP 3070系列檢測器上的XC95216和XC95108

ARM與DSP的SPI通信設計實現(xiàn)

ARM+DSP實現(xiàn)遠程視頻監(jiān)控系統(tǒng)

基于DSP和ARM便攜式電能質量監(jiān)測系統(tǒng)的設計與實現(xiàn)

ARM芯片通過HPI接口與DSP通信的接口技術

XC9572和XC95108 DIY CPLD實驗板的PCB

基于XC95108芯片實現(xiàn)DSP和ARM的并行通信系統(tǒng)的設計

基于XC95108芯片實現(xiàn)DSP和ARM的并行通信系統(tǒng)的設計

評論