摘要

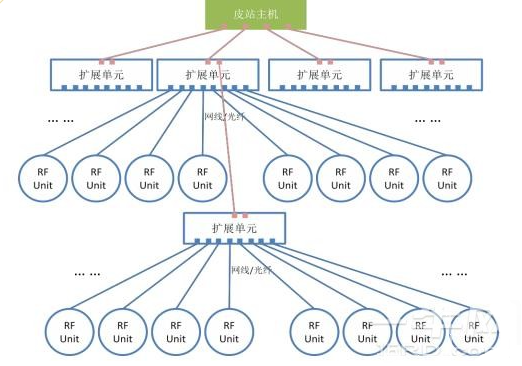

近日,F(xiàn)lex Logix宣布與Socionext簽署協(xié)議,Socionext獲得其EFLX 4K eFPGA授權(quán)許可,并應(yīng)用于5G平臺7nm ASIC 項目開發(fā) 。通過利用eFPGA,Socionext可為客戶提供可編程ASIC,即在流片后也能進(jìn)行再配置,滿足新要求并根據(jù)需求改變標(biāo)準(zhǔn)和協(xié)議。

通過集成 FPGA,Socionext可通過消除基站中的單顆芯片來提高性能并降低功耗。這為運(yùn)營商提供了個性化優(yōu)勢,他們不再需要與 ASIC 供應(yīng)商共享其專有軟件才能集成到 FPGA 中。

無線基站一般通過使用 FPGA 來提高運(yùn)營商個性化和可升級性,但5G需要更高性能和更低的系統(tǒng)功耗和成本,這就需要通過采用 ASIC 解決方案并利用Flex Logix的eFPGA來實現(xiàn)。ASIC 解決方案具有可重新配置性,能為我們的無線客戶提供靈活的5G平臺,更好地為運(yùn)營商支持當(dāng)前和未來的特定需求。

—— Socionext數(shù)據(jù)中心及網(wǎng)絡(luò)事業(yè)部副總裁 林豊

隨著對通過硬件加速、降低系統(tǒng)功耗和成本獲得高性能的需求越來越多,我們看到 ASIC 內(nèi)對RTL可重構(gòu)性的需求不斷增長。無線基站尤其適合利用這種靈活的設(shè)計方式。我們期待與Socionext 合作,幫助他們?yōu)榭蛻籼峁┏瑥?qiáng)適應(yīng)性且面向未來的解決方案。

—— Flex Logix 首席執(zhí)行官 Geoff Tate

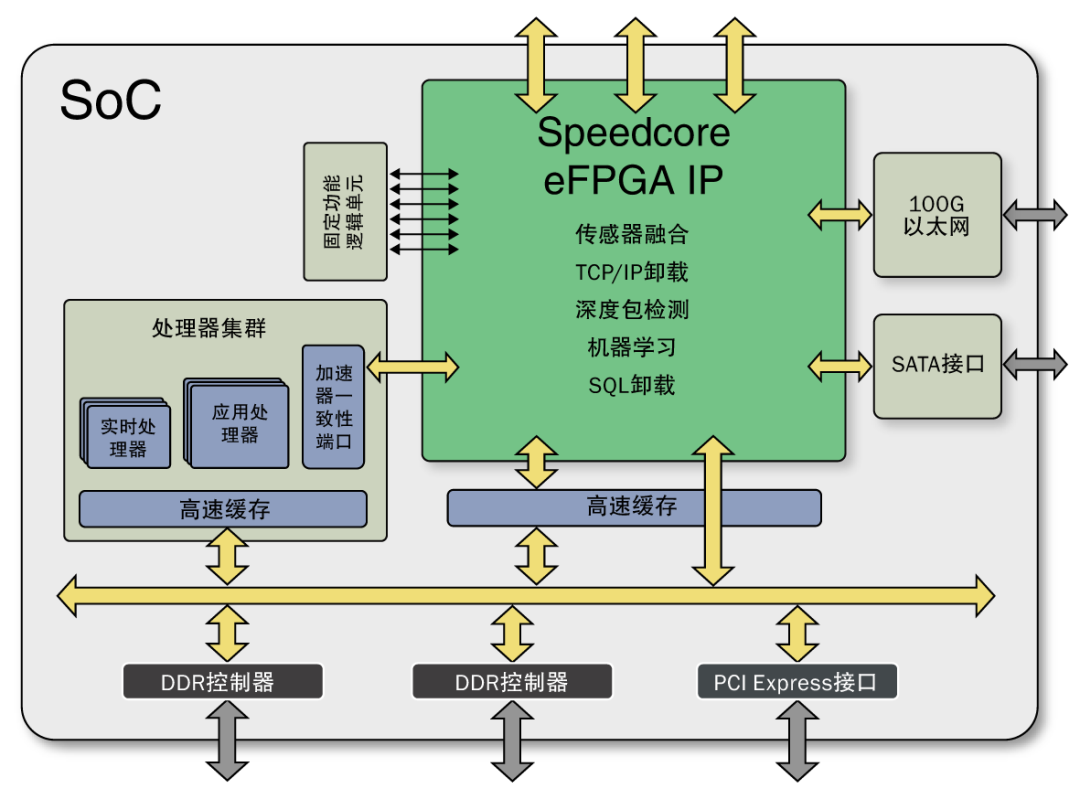

EFLX 是一種用于開發(fā)嵌入式 FPGA 的數(shù)字架構(gòu),可集成到任意尺寸的SoC、ASIC和 MCU中。EFLX4K Logic IP 內(nèi)核具有 4K個等效4輸入LUT、632 個輸入和 632 個輸出,是一個完整的 eFPGA。EFLX4K DSP IP 內(nèi)核用 40 個乘法累加器替換了大約 1/4 的 LUT,用于 DSP 和人工智能(AI) 應(yīng)用。兩個 EFLX4K 內(nèi)核可以平鋪在一起以形成更大的陣列,支持需要更多 LUT 的應(yīng)用程序(最高支持超過 250,00 個 LUT 以及任意混合的邏輯和 DSP 內(nèi)核)。

EFLX 陣列使用 Verilog 或 VHDL 進(jìn)行編程,EFLX Compiler 采用 Synopsys Synplify 等綜合工具的輸出,進(jìn)行布局、布線、時序和比特流生成。比特流在加載到陣列中時,將對其進(jìn)行編程并執(zhí)行所需的 RTL。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

vhdl

+關(guān)注

關(guān)注

30文章

817瀏覽量

128121 -

5G

+關(guān)注

關(guān)注

1354文章

48436瀏覽量

563968

原文標(biāo)題:Socionext 選用Flex Logix嵌入式eFPGA用于5G無線基站平臺

文章出處:【微信號:Socionext,微信公眾號:Socionext】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

ADI收購了一家eFPGA公司,可重構(gòu)芯片成為FPGA發(fā)展新風(fēng)向?

Achronix Speedcore eFPGA的特性和功能

ADI收購Flex Logix,強(qiáng)化數(shù)字產(chǎn)品組合

5G基站核心部件有哪些

今日看點(diǎn)丨ADI收購eFPGA公司Flex Logix;業(yè)界首款!湖北發(fā)布高性能車規(guī)級芯片DF30

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺

嵌入式設(shè)備中的4G/5G模塊管理

飛凌嵌入式4G/5G網(wǎng)卡自管理工具,你的守護(hù)進(jìn)程專家

嵌入式fpga是什么意思

fpga是嵌入式嗎

fpga與嵌入式的區(qū)別 嵌入式和fpga開發(fā)有什么關(guān)系

5G分布式小基站組網(wǎng)結(jié)構(gòu)及優(yōu)勢

Socionext將選用Flex Logix嵌入式eFPGA用于5G無線基站平臺

Socionext將選用Flex Logix嵌入式eFPGA用于5G無線基站平臺

評論