以太網(wǎng)數(shù)據(jù)傳輸硬件設(shè)計(jì)實(shí)現(xiàn)

系統(tǒng)方案設(shè)計(jì)

1.1 設(shè)計(jì)思想

本文研究的是基于FPGA的以太網(wǎng)的MAC層數(shù)據(jù)處理,目的是能廣泛應(yīng)用于多種嵌入式網(wǎng)絡(luò)設(shè)備的前端設(shè)計(jì),如網(wǎng)絡(luò)視頻監(jiān)控設(shè)備、IP數(shù)字電視設(shè)備、家庭智能設(shè)備等。根據(jù)FPGA的可重復(fù)擦寫編程的特點(diǎn),采用FPGA可以方便對(duì)設(shè)備的升級(jí)和維護(hù)。本文為了設(shè)計(jì)能滿足于各種不同的以太網(wǎng)網(wǎng)絡(luò)環(huán)境,和增強(qiáng)系統(tǒng)的可移植性,采取了一系列的措施。

首先,考慮到以太網(wǎng)高速而又龐大的數(shù)據(jù)量,尤其是載有音視頻流的1000M網(wǎng)絡(luò),以及開發(fā)的成本問題,我們引入了一種針對(duì)普通產(chǎn)品開發(fā)的Xilinx芯片——Spartan系列。FPGA具有并行執(zhí)行的特點(diǎn),相對(duì)于其他器件在數(shù)據(jù)處理上具有明顯的速度上的優(yōu)勢(shì),同時(shí)Spartan系列FPGA擁有幾百Kb甚至幾千Kb的塊RAM資源,可用于數(shù)據(jù)的緩存,完全可以滿足于1000M以太網(wǎng)數(shù)據(jù)量的要求。在FPGA的系統(tǒng)設(shè)計(jì)開發(fā)中,常常會(huì)采用某些具有特定功能的IP核以提高系統(tǒng)開發(fā)的效率,減少成本。考慮到開發(fā)周期和設(shè)計(jì)要求,本系統(tǒng)設(shè)計(jì)方案采用Xilinx公司的Tri Mode Ethernet MAC IP核實(shí)現(xiàn)對(duì)MAC數(shù)據(jù)的主要處理工作,該IP核支持多種工作模式,同時(shí)用戶可以根據(jù)要求實(shí)現(xiàn)自定義配置。其次,為了實(shí)現(xiàn)網(wǎng)絡(luò)的IP地址和MAC地址的自動(dòng)映射,本系統(tǒng)還增加了對(duì)ARP數(shù)據(jù)包的解析和ARP應(yīng)答功能的設(shè)計(jì)。除此之外,為了提高系統(tǒng)的通用性,物理芯片需能夠支持1000/100/10M以太網(wǎng)、雙工/半雙工工作模式以及1000M光纖的接入。

1.2 系統(tǒng)功能

根據(jù)以述的設(shè)計(jì)思想,為了滿足大部分設(shè)備對(duì)以太網(wǎng)的MAC數(shù)據(jù)處理的需求,確定了本系統(tǒng)設(shè)計(jì)的功能如下:

(1)支持10M/100M/1000M以太網(wǎng);

(2)支持雙工/半雙工;

(3)CRC校驗(yàn)和幀長度校驗(yàn);

(4)MAC地址濾波;

(5)支持ARP解析;

(6)支持RJ45標(biāo)準(zhǔn)網(wǎng)口和SFP插口的輸入;

1.3 系統(tǒng)總體結(jié)構(gòu)設(shè)計(jì)

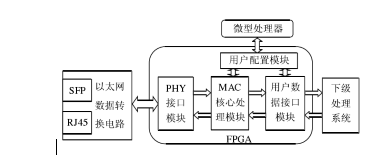

根據(jù)上述技術(shù)指標(biāo)及設(shè)計(jì)思想,圖3-1給出了本系統(tǒng)的總體結(jié)構(gòu)框圖。本系統(tǒng)可分為五大模塊:以太網(wǎng)數(shù)據(jù)轉(zhuǎn)換電路、PHY接口模塊、MAC核心處理模塊、用戶配置模塊和用戶數(shù)據(jù)接口模塊。

圖3-1系統(tǒng)總體結(jié)構(gòu)框圖

(1)以太網(wǎng)數(shù)據(jù)交換電路

以太網(wǎng)數(shù)據(jù)交換電路,主要功能是實(shí)現(xiàn)雙絞線或光纖電纜的以太網(wǎng)物理層數(shù)據(jù)與MAC層數(shù)據(jù)的轉(zhuǎn)換,為FPGA提供處理的MAC數(shù)據(jù)源和送出FPGA的上傳MAC數(shù)據(jù),是傳輸介質(zhì)和FPGA數(shù)據(jù)交流的橋梁。

(2)PHY接口模塊

PHY接口模塊,可分為接收PHY和發(fā)送PHY接口兩個(gè)子模塊,實(shí)現(xiàn)接收數(shù)據(jù)和發(fā)送數(shù)據(jù)的同步。

(3)MAC核心處理模塊

根據(jù)以上設(shè)計(jì)思想,MAC數(shù)據(jù)的核心處理模塊直接采用Xilinx的Tri Mode Ethernet MAC IP核,可以完成MAC地址濾波、數(shù)據(jù)CRC和長度校驗(yàn)、封裝MAC數(shù)據(jù)幀格式等基本功能,對(duì)接受的數(shù)據(jù)進(jìn)行相應(yīng)的好壞標(biāo)記和對(duì)上傳的數(shù)據(jù)進(jìn)行封裝標(biāo)記。

(4)用戶配置模塊

用戶配置模塊主要是實(shí)現(xiàn)主控系統(tǒng)正確地完成對(duì)IP核寄存器和系統(tǒng)地址信息(IP地址和MAC地址)的配置,同時(shí)實(shí)時(shí)地監(jiān)控IP核的工作狀態(tài)。該模塊可分為I2C接口和IP核配置兩個(gè)子模塊,I2C接口子模塊采用400Kb/s的I2C總線協(xié)議,模擬從設(shè)備I2C時(shí)序;IP核配置子模塊模擬IP核HOST配置時(shí)序,以實(shí)現(xiàn)對(duì)IP核寄存器的配置。

(5)用戶數(shù)據(jù)接口模塊

用戶數(shù)據(jù)接口模塊涉及對(duì)通過IP核處理后的接收數(shù)據(jù)幀和待上傳的數(shù)據(jù)包兩部分?jǐn)?shù)據(jù)的處理以及ARP功能的實(shí)現(xiàn),可分為接收數(shù)據(jù)用戶接口、上傳數(shù)據(jù)用戶接口、ARP解析與應(yīng)答三個(gè)子模塊。

芯片的選取

2.1 物理層芯片選擇

以太網(wǎng)物理層的處理工作大多數(shù)直接采用專業(yè)的物理層芯片來完成,完成數(shù)據(jù)的物理層編解碼和收發(fā)功能。目前,物理層芯片的生產(chǎn)商以國外為主,如Marvell、NS、Broadcom公司等,其主流產(chǎn)品為100/10M和1000M物理層芯片,隨著以太網(wǎng)的速率的提高,萬兆物理層芯片也被廣泛應(yīng)用于光纖以太網(wǎng)。國內(nèi)對(duì)芯片的研發(fā)起步比較晚,華為、中興、天津中晶微電子等企業(yè)近些年也推出了不少的產(chǎn)品,但是技術(shù)還有待發(fā)展。

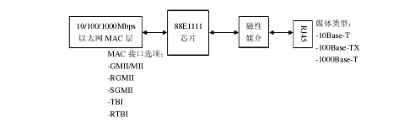

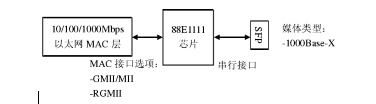

88E1111芯片是Marvell公司Alaska系列的一款千兆以太網(wǎng)收發(fā)器,主要應(yīng)用于10Base-T、100Base-TX、1000Base-T的以太網(wǎng),采用CMOS工藝,能實(shí)現(xiàn)基于CAT5非屏蔽雙絞線標(biāo)準(zhǔn)的以太網(wǎng)物理層數(shù)據(jù)的收發(fā)。88E1111支持多種MAC接口模式,有GMII/MII、RGMII、SGMII、TBI和RTBI,是一款應(yīng)用廣泛的以太網(wǎng)物理層芯片。

88E1111芯片采用了Marvell公司的VCT(Virtual Cable Tester,虛擬電纜測(cè)試儀)功能,可以使用時(shí)域反射技術(shù)遠(yuǎn)程測(cè)試電纜故障,減少了設(shè)備應(yīng)答和服務(wù)請(qǐng)求的次數(shù),同時(shí)還能通過VCT檢測(cè)線纜潛在的問題和線纜的開路、短路或阻抗不匹配問題,準(zhǔn)確度能達(dá)到一米。另外,88E1111芯片具有先進(jìn)的混合信號(hào)處理能力,可以以1Gbps的速率完成自適應(yīng)均衡、消除反射或串?dāng)_、數(shù)據(jù)恢復(fù)、誤碼糾正等功能,是一款抗噪聲能力強(qiáng)的低功耗以太網(wǎng)物理層芯片。

88E1111芯片中嵌入了一個(gè)可選的1.25GHzSERDES(并串轉(zhuǎn)換/串并轉(zhuǎn)換器),可以直接與光纖收發(fā)器連接,實(shí)現(xiàn)1000Base-X光纖標(biāo)準(zhǔn)與1000Base-T雙絞線標(biāo)準(zhǔn)傳輸媒體的轉(zhuǎn)換。通過選擇,88E1111可以通過RJ45接口接入1000Base-T雙絞線網(wǎng)絡(luò)或SFP(小型可插拔)模塊接入光纖網(wǎng)絡(luò),分別如圖3-2和3-3所示。

圖3-2 88E1111接入雙絞線網(wǎng)絡(luò)

圖3-3 88E1111接入光纖網(wǎng)絡(luò)

除了以上所述,88E1111芯片還支持光纖與銅線自動(dòng)檢測(cè)、網(wǎng)絡(luò)連接的自動(dòng)協(xié)商、可編程的LED驅(qū)動(dòng)等功能,方便了用戶對(duì)以太網(wǎng)接入的開發(fā)。

根據(jù)本文系統(tǒng)設(shè)計(jì)的功能的要求,以太網(wǎng)物理層芯片需滿足同時(shí)支持RJ45和SFP兩種接口,10Base-T、100Base-TX、1000Base-T標(biāo)準(zhǔn)雙絞線和千兆光纖介質(zhì)的傳輸,半雙工和雙工切換的工作模式。Marvell公司的以太網(wǎng)物理層芯片88E1111,采用0.13μm的CMOS工藝,是一款低成本、低功耗的千兆以太網(wǎng)物理層芯片,足以滿足系統(tǒng)設(shè)計(jì)的要求

2.2 FPGA主芯片選擇

在FPGA的開發(fā)設(shè)計(jì)中,F(xiàn)PGA芯片的選取非常重要,不合理的選取會(huì)導(dǎo)致一系列的后續(xù)設(shè)計(jì)問題,甚至?xí)。缓侠淼倪x取不僅避免設(shè)計(jì)問題,而且可以提高系統(tǒng)的性價(jià)比,延長產(chǎn)品的生命周期。通常,F(xiàn)PGA芯片選取需從芯片的供貨商和開發(fā)工具的支持、電氣接口標(biāo)準(zhǔn)、硬件資源、速度等級(jí)、溫度等級(jí)、封裝形式、價(jià)格七個(gè)方面入手。

(1)供貨商和開發(fā)工具的支持

目前,主要的FPGA供應(yīng)商有Xilinx公司、Altera公司、Lattice公司和Actel公司等,F(xiàn)PGA的發(fā)展迅速,器件的淘汰率隨之提高,為了延長產(chǎn)品的生命周期,最好選擇貨源比較足的主流器件。

從開發(fā)工具來看,Xilinx公司的ISE和Altera公司的QuartusⅡ,更新及時(shí)、功能強(qiáng)大、界面友好,支持本公司所有器件的設(shè)計(jì)開發(fā)和很多第三方軟件的應(yīng)用,如Synplify Pro、ModleSim等,能將器件的性能發(fā)揮到最佳。因此,一般在沒有特殊要求情況下,器件從這兩家公司中選取。

雖然Altera公司的開發(fā)智能程度相對(duì)Xilinx公司要高一些,但Xilinx公司具有更強(qiáng)的硬件功能,通過IP核的使用可以達(dá)到更高的效率。目前,Xllinx公司的主流器件有Spartan-3、Spartan-3A/3ADSP/3AN、Virtex-4LX、Virtex-4SX、Virtex-4FX、Virtex-5LX、Virtex-5SX、Virtex-5FX、Spartan-6和Virtex-6等系列,其中Spartan-3系列主要應(yīng)用于邏輯設(shè)計(jì);Spartan-3A/3ADSP/3AN主要應(yīng)用于簡(jiǎn)單數(shù)字信號(hào)處理,Virtex-4LX和Virtex-5LX系列主要應(yīng)用于高速邏輯設(shè)計(jì),Virtex-4SX和Virtex-5SX系列主要應(yīng)用于高速復(fù)雜數(shù)字信號(hào)處理,Virtex-4FX和Virtex-5FX系列主要應(yīng)用于嵌入式系統(tǒng)。本設(shè)計(jì)只需要對(duì)MAC數(shù)據(jù)幀做簡(jiǎn)單的邏輯處理和緩存等等,Spartan-3系列器件足以滿足這一需求。

(2)芯片的電氣接口標(biāo)準(zhǔn)

目前,數(shù)字電路的電氣接口標(biāo)準(zhǔn)非常多,在某些大型的系統(tǒng)設(shè)計(jì)中常常需要同時(shí)支持多種電氣接口標(biāo)準(zhǔn)。本設(shè)計(jì)中的FPGA的接口電氣標(biāo)準(zhǔn)只采用了LVCMOS2.5V和LVCMOS3.3V,Xilinx公司的絕大部分器件均能夠滿足。

(3)硬件資源

硬件資源是FPGA芯片選取的重要指標(biāo),包括邏輯資源、I/O資源、布線資源、存儲(chǔ)器資源和某些底層內(nèi)嵌功能單元和內(nèi)嵌專用硬核等。在FPGA設(shè)計(jì)中,I/O資源和邏輯資源的需求是最需要重點(diǎn)考慮的問題。邏輯資源一般要求消耗的資源不超過70%,主流FPGA器件中,邏輯資源都比較豐富,比較容易選擇。I/O資源需要注意的是避免過度的消耗,因?yàn)檫^度的消耗可能會(huì)導(dǎo)致FPGA負(fù)荷過重,器件發(fā)熱量過大,以影響器件的速度性能、工作穩(wěn)定性和壽命,設(shè)計(jì)中也要充分考慮器件的散熱問題。另外,局部布線資源也要充足,以免影響電路的運(yùn)行速度。在一些特殊場(chǎng)合,特別是數(shù)據(jù)量比較大的情況下,還得考慮存儲(chǔ)器資源,如BRAM或LUT資源。還有鎖相環(huán)、DSP等底層內(nèi)嵌功能單元或內(nèi)嵌專用硬核可以根據(jù)具體的設(shè)計(jì)作為參考需求。

(4)速度等級(jí)

對(duì)于芯片速度等級(jí)的選取,有一個(gè)基本原則:在滿足應(yīng)用需求的情況下,盡量選擇速度等級(jí)低的芯片。因?yàn)樗俣鹊燃?jí)高的芯片更容易產(chǎn)生信號(hào)反射,增加價(jià)格成本,延長開發(fā)周期。本設(shè)計(jì)的主時(shí)鐘最高位125M,XC3S400芯片具有-4和-5兩個(gè)速度等級(jí),-4等級(jí)的最高可以達(dá)到250M,為節(jié)約成本,選取的芯片采用-4等級(jí)。

3.1 以太網(wǎng)變換電路設(shè)計(jì)

以太網(wǎng)數(shù)據(jù)變換電路,實(shí)現(xiàn)的是以太網(wǎng)傳輸媒介上的物理層數(shù)據(jù)與MAC層數(shù)據(jù)的轉(zhuǎn)換,為FPGA提供待處理的MAC數(shù)據(jù)源和輸出待上傳的MAC數(shù)據(jù),本設(shè)計(jì)主要是選擇物理層專業(yè)芯片88E1111完成這一功能,其電路設(shè)計(jì)包括以下幾個(gè)方面:

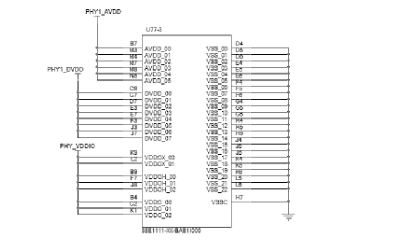

88E1111芯片支持兩種電平:2.5V和1.0V,有時(shí)也可用1.2V代替1.0V。如圖3-4所示為芯片的電源電路圖,PHY_VDDIO采用2.5V,為芯片I/O引腳供電,與芯片引腳VDDO、VDDOH、VDDOX相連;PHY1_AVDD提供內(nèi)部模擬邏輯電平,為2.5V,與AVDD引腳相連;PHY1_DVDD提供內(nèi)部數(shù)字邏輯電平

圖3-488E1111芯片電源電路

為1.0V,與DVDD引腳相連。為了提高電源的穩(wěn)定性,電源PHY_VDDIO、

PHY1_AVDD、PHY1_DVDD需接入一些濾波電容,以減少電源噪聲。

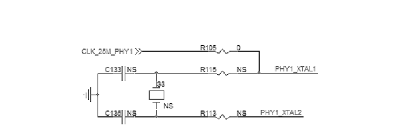

88E1111芯片對(duì)數(shù)據(jù)的處理需要有一個(gè)參考時(shí)鐘,一般通過XAT1引腳輸入25M或125M的參考時(shí)鐘,或通過XAT1和XAT2直接接一個(gè)晶振。本設(shè)計(jì)采用XAT1引腳輸入25M的時(shí)鐘,以減少晶振的使用數(shù)量,如圖3-5所示,CLK_25M_PHY1與XAT1引腳相連,提供25M的時(shí)鐘;為了保證電路的可調(diào)性,同時(shí)在XAT1和XAT2的兩端添加一個(gè)晶振,作為參考時(shí)鐘的備用方案。

圖3-588E1111芯片時(shí)鐘電路

(2)配置電路設(shè)計(jì)

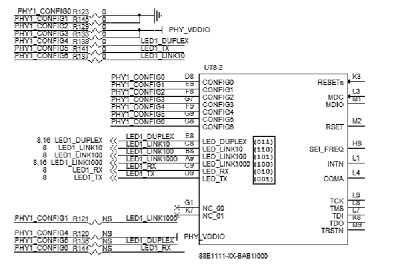

在88E1111的芯片設(shè)計(jì)中,器件物理地址、PHY操作模式、自動(dòng)協(xié)商模式、MDI(Media Dependent Interface,媒介相關(guān)接口)交叉功能、PHY接口模式等的配置需通過芯片CONFIG0~CONFIG6引腳硬件配置來實(shí)現(xiàn),CONFIG0~CONFIG6引腳配置位映射關(guān)系表和各配置寄存器的定義描述分別如表3-3和表3-4所示。

在硬件電路設(shè)計(jì)中,CONFIG0~CONFIG6配置位的選擇通常是通過與LED輸出引腳、VDDO或者VSS引腳的連接來完成的,其各引腳與配置位的映射關(guān)系如表3-5所示。

為了方便開發(fā)設(shè)計(jì),本設(shè)計(jì)將芯片地址設(shè)置為00000,屏蔽PAUSE幀,同時(shí)使能MDI交叉連接、光纖與銅線接入自動(dòng)識(shí)別、能量檢測(cè)功能,其自動(dòng)協(xié)商支持所有網(wǎng)路模式;125MHz的數(shù)據(jù)發(fā)送的參考時(shí)鐘由FPGA提供,125MHz時(shí)

表3-3CONFIG0~CONFIG6引腳配置位映射關(guān)系表

| 引腳 | Bit[2] | Bit[1] | Bit[0] |

| CONFIG0 | PHYADR[2] | PHYADR[1] | PHYADR[0] |

| CONFIG1 | ENA_PAUSE | PHYADR[4] | PHYADR[3] |

| CONFIG2 | ANEG[3] | ANEG[2] | ANEG[1] |

| CONFIG3 | ANEG[0] | ENA_XC | DIS_125 |

| CONFIG4 | HWCFG_MODE[2] | HWCFG_MODE[1] | HWCFG_MODE[0] |

| CONFIG5 | DIS_FC | DIS_SLEEP | HWCFG_MODE[3] |

| CONFIG6 | SEL_TWSI | INT_POL | 75/60OHM |

表3-4各配置寄存器定義描述

| 配置寄存器 | 定義描述 |

| PHYADR[4:0] | 器件的物理地址,在MDC/MDIO配置模式下,表示器件五位的物理件地址;在I2C配置模式下,表示器件物理地址phyaddr[4:0],phyaddr[6:5]固定為10。 |

| ENA_PAUSE | PAUSE 幀使能信號(hào),高有效;同時(shí)影響寄存器4 的默認(rèn)值 |

| ANEG[3:0] | 自動(dòng)協(xié)商模式配置寄存器,10/100/1000Base-T模式下由ANEG[3:0]配置決定,而1000Base-X模式下由ANEG[3:2]配置決定,具體的配置映射關(guān)系可參考88E1111芯片手冊(cè)。 |

| ENA_XC | 交叉連接使能信號(hào),1時(shí)MDI交叉功能有效,反之則無效。 |

| DIS_125 | 125MHz時(shí)鐘使能信號(hào),0使能。 |

| HWCFG_MODE[3:0] | 硬件配置模式,決定了PHY接口模式,常用的有:1000Base-X模式下RGMII為0011;1000Base-X模式下GMII 為0111;10/100/1000Base-T模式下RGMII為1011;10/100/1000Base-T模式下RGMII為1111;其他的模式配置可參考88E1111芯片手冊(cè) |

| DIS_FC | 光纖與銅線接入自動(dòng)識(shí)別使能信號(hào),0有效。 |

| DIS_SLEEP | 能量檢測(cè)使能信號(hào),0有效。 |

| SEL_TWSI | 寄存器配置模式選擇,0表示采用MDC/MDIO配置模式,1表示采用I2C配置模式。 |

| INT_POL | 中斷電平值,0表示高電平中斷,1表示低電平中斷。 |

| 75/60 OHM | 終端電阻匹配選擇信號(hào),主要用于光纖接入模式下,0采用50OHM,1采用75OHM。 |

表3-5各引腳與配置位的映射關(guān)系

| 引腳 | Bit[2:0] |

| VDDO | 111 |

| LED_LINK10 | 110 |

| LED_LINK100 | 101 |

| LED_LINK1000 | 100 |

| LED_DUPLEX | 011 |

| LED_RX | 010 |

| LED_TX | 001 |

| VSS | 000 |

鐘輸出設(shè)置為無效;IPQAM項(xiàng)目的CPU對(duì)從設(shè)備的寄存器配置采用的是I2C總線方式,因此88E1111需配置成I2C從模式;PHY接口采用GMII/MII模式,減少FPGA對(duì)時(shí)鐘的時(shí)序要求。因此,如圖3-6配置電路圖所示,默認(rèn)情況下將CONFIG0~CONFIG6引腳分別配置為000、000、111、111、111、001、110。但是為了系統(tǒng)的升級(jí)維護(hù),對(duì)CONFIG1、CONFIG4、CONFIG5、CONFIG6引腳設(shè)置了配置保留值,根據(jù)不同的需求本系統(tǒng)可以支持PAUSE幀的傳輸、RGMII的PHY 接口、MDC/MDIO寄存器配置等工作模式。

圖3-6 88E1111配置電路

(3)RJ45接口和SFP接口電路設(shè)計(jì)

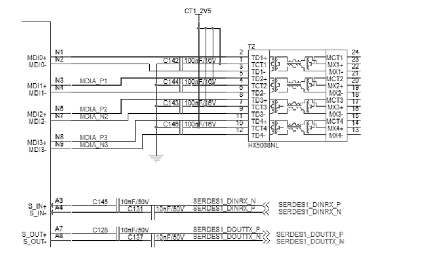

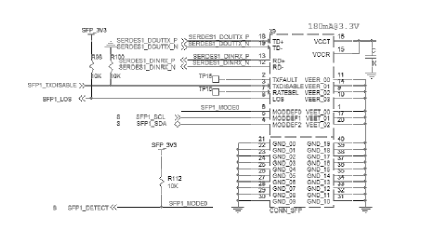

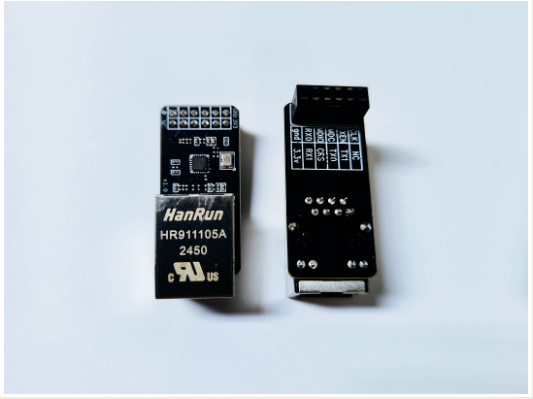

本系統(tǒng)支持普通雙絞線和光纖兩種媒介接入方式,雙絞線的接入采用通用的RJ45接口,其電路圖如圖3-7所示,88E1111芯片的四對(duì)MDI引腳直接與HX5008NL芯片的四對(duì)TD引腳相連,實(shí)現(xiàn)與RJ45接口的連接,完成雙絞線與88E1111芯片的數(shù)據(jù)交換;光纖的接入采用SFP接口,其電路圖如圖3-8所示,88E1111芯片的S_IN±引腳與SFP接口芯片的RD±引腳相連,接收光纖電纜上的數(shù)據(jù);S_OUT±引腳與TD±引腳相連,完成本地的數(shù)據(jù)的輸出;同時(shí)SFP接口芯片采用I2C配置模式,與系統(tǒng)設(shè)計(jì)一致。

圖3-7 RJ45接口電路

圖3-8 SFP接口電路

責(zé)任編輯:lq6

-

FPGA

+關(guān)注

關(guān)注

1643文章

21932瀏覽量

612927 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5559瀏覽量

174447 -

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

1994瀏覽量

65538

原文標(biāo)題:以太網(wǎng)數(shù)據(jù)傳輸硬件設(shè)計(jì)實(shí)現(xiàn)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

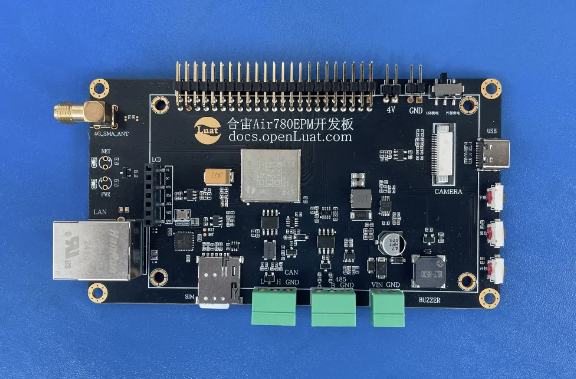

釋放無限可能!支持WAN和LAN,以太網(wǎng)功能兩種用法隨心用!

一文讀懂~ 源碼開放:Air8101快速實(shí)現(xiàn)以太網(wǎng)功能!

單對(duì)以太網(wǎng)供電技術(shù)的演進(jìn)和應(yīng)用

ptp對(duì)實(shí)時(shí)數(shù)據(jù)傳輸的影響

LORA模塊的數(shù)據(jù)傳輸速率

以太網(wǎng)端口雙工模式是什么意思

以太網(wǎng)交換模式有哪幾種

以太網(wǎng)的傳輸介質(zhì)和工作模式

以太網(wǎng)幀結(jié)構(gòu)是怎樣的

以太網(wǎng)數(shù)據(jù)采集網(wǎng)關(guān):數(shù)據(jù)匯聚與傳輸的關(guān)鍵橋梁

以太網(wǎng)端口的類型和特性

速銳得解碼汽車以太網(wǎng)技術(shù)特點(diǎn)接口定義數(shù)據(jù)傳輸及應(yīng)用

以太網(wǎng)接口的數(shù)據(jù)傳輸原理詳解

TIDA-010076-通過單對(duì)以太網(wǎng) (T1) 實(shí)現(xiàn)菊花鏈?zhǔn)诫娫春?b class='flag-5'>數(shù)據(jù)傳輸的PCB layout 設(shè)計(jì)

評(píng)論