作者:周云鋒,孫書鷹,王宏

USB(Universal Serial Bus)總線是INTEL、NEC、MICROSOFT、IBM等公司聯合提出的一種新的串行總線接口規范。為了適應高速傳輸的需要,2000年4月,這些公司在原1.1協議的基礎上制訂了USB2.0傳輸協議,已超過了目前IEEE1394接口400Mbps的傳輸速度,達到了480Mbps。USB總線使用簡單,支持即插即用PnP(Plug And Play),一臺主機可串連127個USB設備。設備與主機之間通過輕便、柔性好的USB線纜連接,最長可達5m,使設備具有移動性,可自由掛接在具有USB接口的運行在Windows98/NT平臺的PC機上。USB總線已被越來越多的標準外設和用戶自定義外設所使用,如鼠標、鍵盤、掃描儀、音箱等。

結合設備檢測中數據采集的實際需要,設計了該高速同步數據采集系統。該系統最多可四路同步采樣,單通道采樣速度可達620ksps,四通道同時采樣速度可達180ksps。USB接口控制芯片采用Cypress公司FX2系列中的CY7C68013,通過對其可編程接口控制邏輯的合理設計和芯片內部FIFO的有效運用,實現了數據的高速連續采樣和傳輸。

1 基本原理

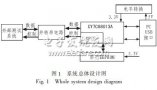

該采集系統總體框架分三部分:主機(能支持USB2.0協議的PC機)、內部包含CPU及高速緩存的USB接口控制芯片(CY7C68013)和高速同步采樣芯片(MAX115),如圖1所示。其數據傳輸分兩部分:控制信號傳輸和采集數據傳輸。控制信號方向為由主機到外設,由外設CPU控制,數據量較小;采集到的數據由外設到主機,數據量較大。為了保證較高的傳輸速度,不經過CPU。系統基本操作過程為:主機給外設一個采樣控制信號,FX2根據該信號向A/D轉換器送出相應控制信號,即采樣模式控制字;之后由A/D轉換器自主控制轉換,并將各通道采樣數據存入其片內緩存。一旦轉換完成,由A/D的完成位向FX2的可編程控制接口發讀采樣結果信號;然后由可編程接口的控制邏輯依次將各通道采樣結果從A/D的緩存讀入FX2的內部FIFO。當FIFO容量達到指定程度后,自動將數據打包傳送給USB總線。期間所有操作不需要CPU的干預。采樣過程中接口控制邏輯依次取走批量數據,在打包傳送時A/D仍持續轉換,內部FIFO也持續寫入轉換結果。只要內部FIFO寫指針和讀指針位置相差達到指定的值就立即取走數據。從而保證了同步連續高速采集的可靠性。

2 硬件部分

2.1 芯片介紹

CY7C68013屬于Cypress公司的FX2系列產品,它提供了對USB2.0的完整解決方案。該芯片包括帶8KB片內RAM的高速CPU、16位并行地址總線+8位數據總線、I2C總線、4KB FIFO存儲器以及通用可編程接口(GPIF)、串行接口引擎(SIE)和USB2.0收發器。在代碼的編寫上,與8051系列單片機兼容,且速度是標準8051的3~5倍。

CY7C68013與外設有兩種接口方式:可編程接口GPIF和Slave FIFOs。

可編程接口GPIF是主機方式,可以由軟件設置讀寫控制波形,靈活性很大,幾乎可以對任何8/16 bit接口的控制器、存儲器和總線進行數據的主動讀寫,使用非常靈活。Slave FIFOs方式是從機方式,外部控制器可象對普通FIFO一樣對FX2的多層緩沖FIFO進行讀寫。FX2的Slave FIFOs工作方式可設為同步或異步;工作時鐘為內部產生或外部輸入可選;其它控制信號也可靈活地設置為高有效或低有效。筆者在設計中采用主機方式。

MAX115是美信公司的高速多通道同步采樣芯片。含有兩組4路同步通道,共8個輸入端。采樣精度為12位,采樣模式由采樣控制字決定,可靈活地在兩組中的1~4個通道間選擇。采樣時,各通道轉換結果先存入其內部相對應的4個12bit存儲單元,各通道都轉換完后再一起取走。

2.2 電路原理及設計

考慮CY7C68013與MAX115接口時,采樣模式不同,控制波形有所差別,筆者選擇主機方式即可編程控制接口(GPIF)。

GPIF是FX2端點FIFO的內部控制器。在這種方式下,接口內核可產生6個控制輸出端(CTL0~CTL5)和9根線的地址(GADR[8:0])輸出,同時可以接收6個外部輸入(RDY0~RDY5)和2個內部輸入。FX2有4個波形描述符控制各個狀態。這些波形描述符可以動態地配置給任何一個端點FIFO。例如,一個波形描述符可以配置為寫FIFO,而另一個配置為讀FIFO。FX2的固件程序可以把這些描述符配置給四個FIFO中的任意一個,配置后,GPIF將依據波形描述符產生相應的控制邏輯和握手信號給外界接口,滿足向FIFO讀寫數據的需要。GPIF的數據總線既可以是單字節寬(8位FD[7:0])也可以是雙字節寬(16位FD[15:0])。每個波形描述符包含了S0~S6 七個有效狀態和一個空閑狀態。在每個有效狀態對應的時間段里,經過預先設置,GPIF可以做以下幾件事情:(1)驅動(使為高或低)或懸浮6個輸出控制端;(2)采樣或驅動FIFO的數據總線;(3)增加GPIF地址總線的值;(4)增加指向當前FIFO指針的值;(5)啟動GPFIWF(波形描述符)中斷。除此之外,在每個狀態,GPIF可以對以下幾個信號中任意兩個進行采樣,它們是:(1)RDYX輸入端;(2)FIFO狀態標志位;(3)內部RDY標志位;(4)傳輸計數中止標志位。把其中兩個信號相與、相或或者相異或,根據結果跳轉到其它任意一個狀態或延遲1~256個IFCLK時鐘周期。當然也可以根據輸入端的信號進行跳轉或延遲。GPIF波形描述符通常用Cepress公司的GPIF工具(GPIFTOOL)進行配置。它是一個可運行于Windows平臺的應用程序,與FX2的開發包一起發布。

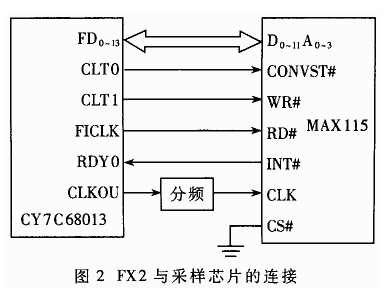

在這種方式下,所有的讀寫及控制邏輯通過CY7C68013 的GPIF以軟件編程的方式實現,且控制邏輯的變換方便靈活(只需要改變接口的一個配置寄存器的值)。電路連接如圖2所示。

本數據采集系統只用到了兩個輸出控制CTL0、CTL1和一個外部輸入RDY0,它們分別接MAX115的CONVST#、WR#和INT#。數據總線用雙字節,其中FD0~FD11接MAX115的數據輸入端D0~D11,FD12和FD13接控制字輸入端的A2和A3,FD0和FD1復用做控制字輸入端的A0和A1。MAX115的采樣基準時鐘由FX2的輸出時鐘經三分頻得到,為16MHz。對應四種數據傳輸方式(八種不同的采樣模式),GPIF的控制及握手信號波形有所不同。四通道同步采樣的時序圖如圖3所示。

在第一個判決點,若采樣數據已準備就緒,MAX115傳給GPIF一個負脈沖信號RDY0;根據此信號,波形按順序轉入2、3、4、5狀態,使指向內部FIFO的指針在每個時鐘上升沿加1,依次讀取四個數據,取完數據后利用CTL0的上升沿啟動下一次采樣。若在狀態1時沒有出現負脈沖,則直接跳轉到狀態6,之后重復執行此波形描述符。

三通道同步采樣時,讀取數據的狀態只需要持續三次。其它采樣模式控制波形的設計依此類推。

2.3 固件程序設計

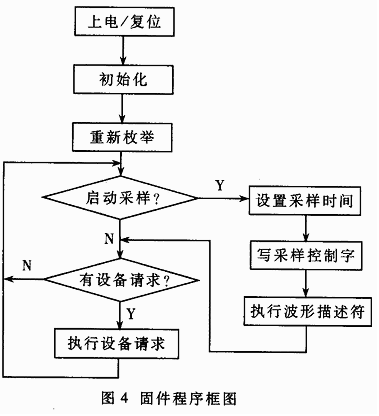

固件程序是指運行在設備CPU中的程序。只有在該程序運行時,外設才能稱之為具有給定功能的外部設備。固件程序負責初始化各硬件單元,重新配置設備及A/D采樣控制。固件代碼的存儲位置有三種:第一種是存在主機中,設備加電后由驅動程序把固件下載到片內RAM后執行,即“重新枚舉”;第二種方法是把固件代碼固化到一片EEPROM中,外設加電后由FX2通過I2C總線下載到片內RAM后自動執行;最后一種方法是把程序固化到一片ROM中,使之充當外部程序存儲器,連在FX2三總線上。筆者選用第一種方式,這種方式便于系統的調試和升級。固件程序框圖如圖4所示。

3 用戶程序和驅動程序

3.1 驅動程序的編寫

該系統需要兩個驅動程序,即通用驅動和下載固件的驅動。通用驅動完成與外設和用戶程序的通信及控制;而下載固件的驅動則只負責在外設連接USB總線后把特定的固件程序下載到FX2的RAM中,使FX2的CPU重啟,模擬斷開與USB總線的連接,完成對外設的重新設置。主機根據新的設置安裝通用驅動程序,重新枚舉外設為一個新的USB設備。

通用驅動程序一般不需要重新編寫,用Cypress公司已經編好的驅動ezusb.sys;而下載固件的驅動則必須定做,其詳細操作過程見參考文獻[2]。

3.2 用戶程序的編寫

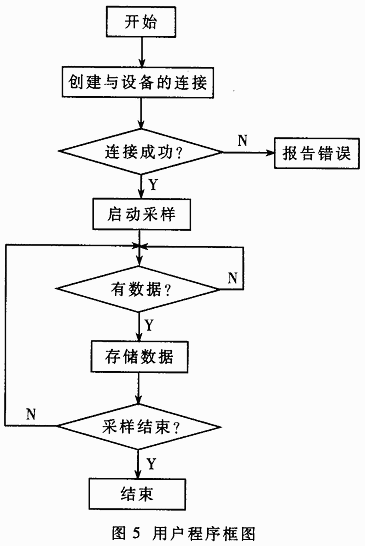

用戶程序是系統與用戶的接口,它通過通用驅動程序完成對外設的控制和通信。在編寫用戶程序時,首先要建立與外設的連接,然后才能實施數據的傳輸。啟動采樣后,為了保證不丟失數據,用戶程序應該建立一個新的工作線程專門獲取外設傳來的數據。程序中主要用到兩個API函數:CreateFile()和DeviceIoControl ()。CreateFile()取得設備句柄后,DeviceIoControl ()根據該句柄完成數據傳輸。程序代碼簡要如下:

hDevice = CreateFile(″\\\\。\\EZUSB-0″)

GENERIC_READ | GENERIC_WRITE,

FILE_SHARE_WRITE,

NULL,

OPEN_EXISTING,

FILE_ATTRIBUTE_NORMAL,

NULL);

If (hDevice == INVALID_HANDLE_VALUE)

{

Application-》MessageBoxA(“無法創建設備,請確認設備是否連上!”,NULL,IDOK);

}

else

{

DeviceIoControl (

hDevice,

IOCTL_EZUSB_BULK_WRITE,

&blkctl,

sizeof(BULK_TRANSFER_CONTROL),

&inBuffer, //定義的數據緩沖區

sizeof(inBuffer),

&nBytes,

NULL);

……

}

程序框圖如圖5所示。

在該高速同步數據采集系統的設計中,CY7C68013芯片靈活的接口和可編程特性簡化了外部硬件的設計,提高了系統的可靠性,也利于PCB板的制作與調試。另外,USB設備的可熱插拔特性使得該系統具有便攜式的特點,使用方便,無需關機重啟或打開機箱進行安裝。該數據采集系統已成功地應用于某型。

責任編輯:gt

-

芯片

+關注

關注

455文章

50714瀏覽量

423152 -

數據采集

+關注

關注

38文章

6053瀏覽量

113622 -

總線

+關注

關注

10文章

2878瀏覽量

88052

發布評論請先 登錄

相關推薦

求大俠幫忙 CY7C68013 與CPLD通信問題

如何利用MAX115的電網數據采集和模/數轉換對已使用多年的系統進行改進?

cy7c68013開發包及驅動

基于CY7C68013的USB數據采集系統

基于USB2.0的同步高速數據采集器的設計

基于CY7C68013的CCD圖像傳輸系統

基于CY7C68013A的并口轉USB口數據采集系統設計

基于CY7C68013和MAX115芯片實現高速同步數據采集系統的應用方案

基于CY7C68013和MAX115芯片實現高速同步數據采集系統的應用方案

評論