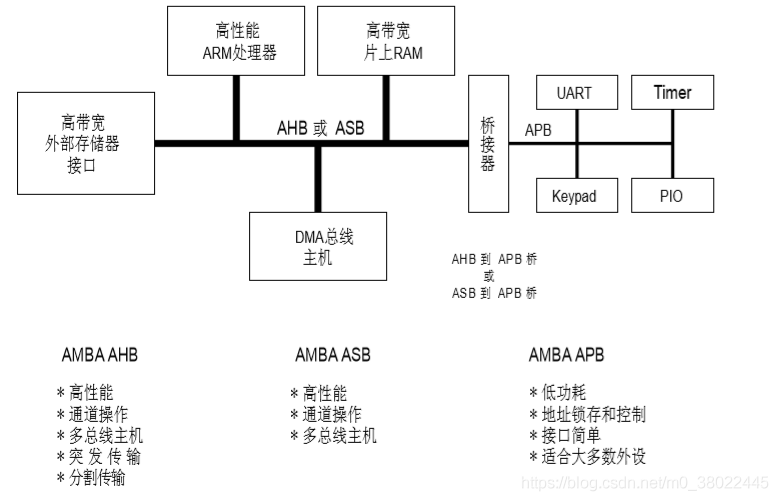

AHB(高級高性能總線):用于高性能高時鐘頻率的系統模塊,AHB 擔當高性能系統的中樞總線。AHB 支持處理器,片上存儲器,片外存儲器以及低功耗外設宏功能單元之間的有效連接。

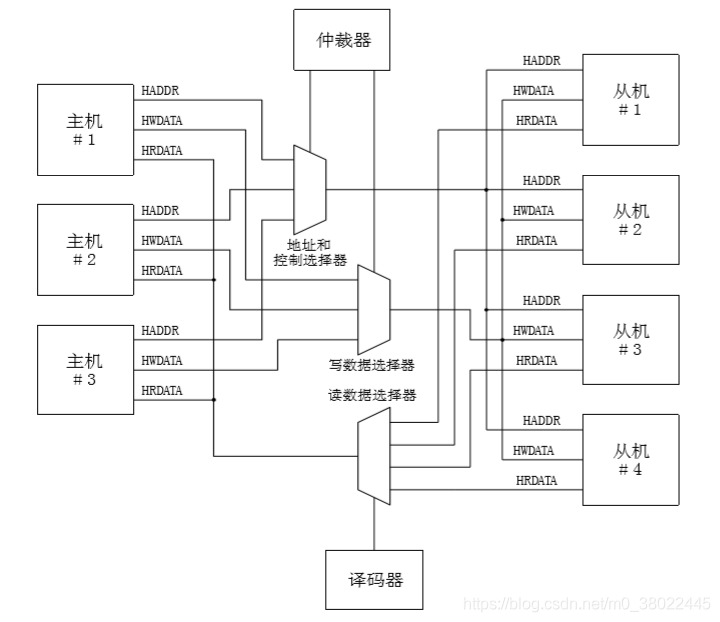

下圖為典型AMBA系統:

AHB總線特征:

流水線操作/支持多個主線總設備(EMI/APB_bridge/DMA/CPU/DSP/LCDC)/上升沿觸發操作

典型AHB總線包含:

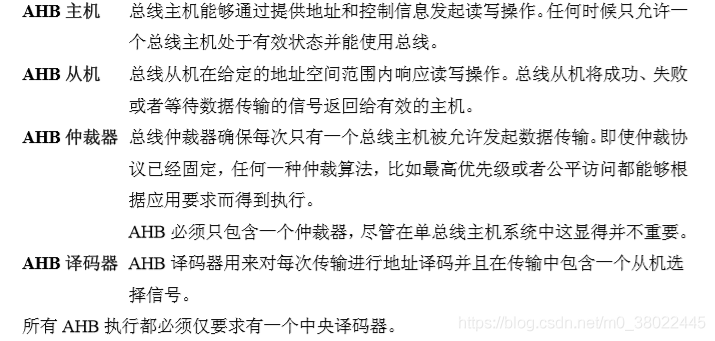

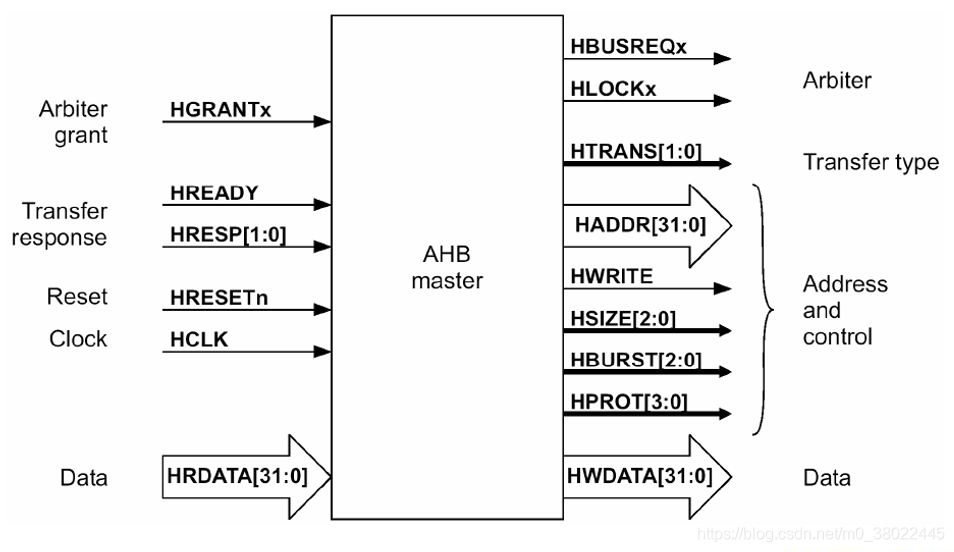

AHB信號列表:

AHB主/從設備端口:

AHB結構:

AHB中,寫數據總線用來將數據從主機傳輸到從機上,而讀數據總線用來將數據從從機傳輸到主機上。

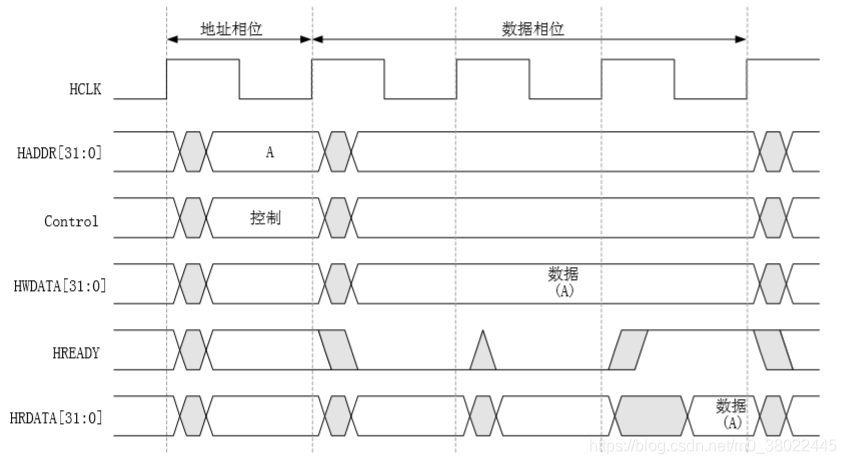

AHB簡單傳輸分析:第一個HCLK上升沿后將地址和控制信號驅動到總線上,第二個上升沿到來,由于HREADY為1則數據寫,HWDATA存在一定延時,再過一段延時后數據到達HRDATA

AHB等待傳輸 :HREADY=0表示從機讓主機等待,等恢復1后進行傳輸

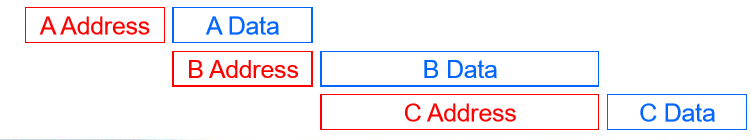

AHB的流水線傳輸:到地址A和C都為無等待傳輸,到地址B由于HREADY=0為一個等待狀態,傳輸到地址B的擴展數據相位對傳輸到地址 C 的擴展地址相位有影響,因為C的地址信號寫入和B數據寫入在同一周期。

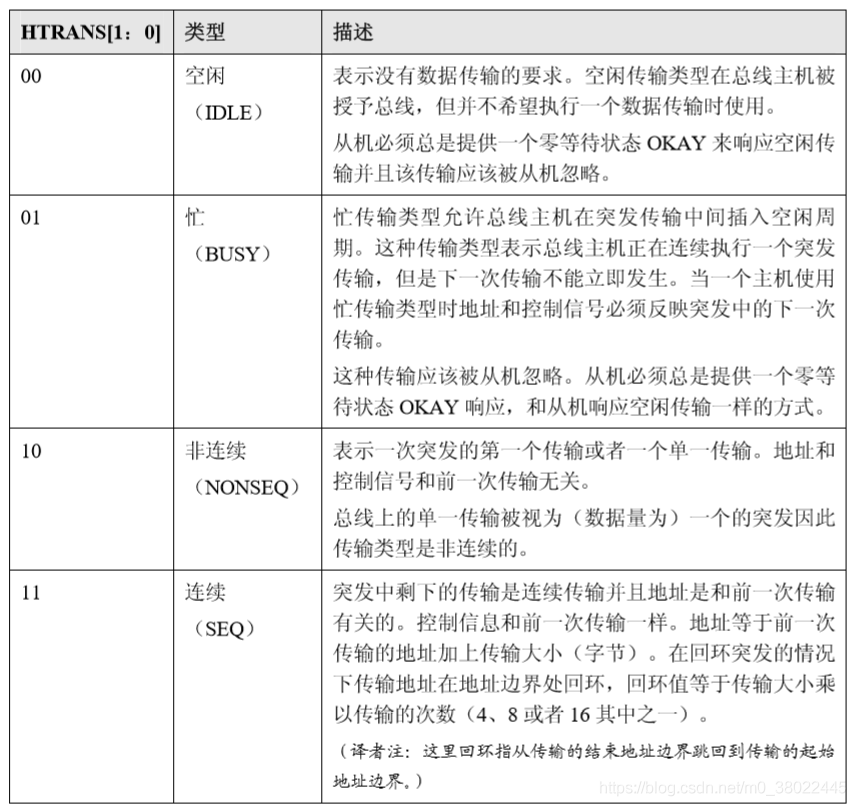

AHB傳輸類型可以分為4類:

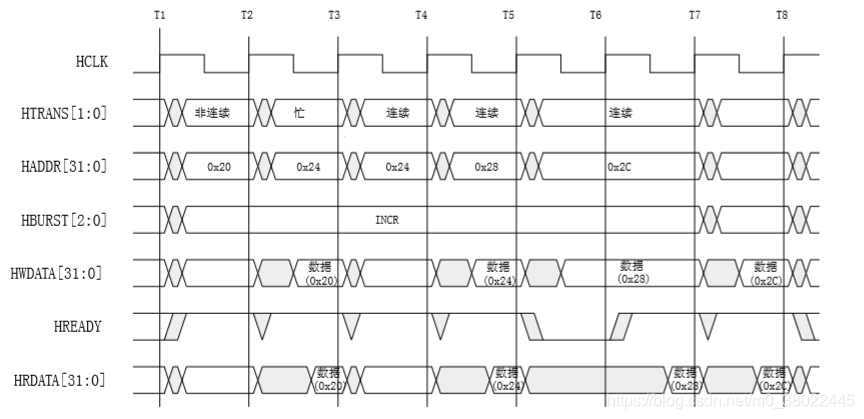

傳輸類型實例分析:

T1開始一個非連續傳輸,T1中將地址和控制信號寫入;T2開始數據傳輸,T2原本有地址和控制信號寫入過程,但是由于BUSY信號主機讓從機等待一周期;第二個地址和控制信號順延至T3,開始連續傳輸,T4開始第三個地址及控制信號/第二個數據信號傳輸,T5本來是進行第四個信號的地址和控制信號傳輸,由于HREADY為低,從機讓主機等待一周期,主機信號保持,在T7后進行第四個數據信號傳輸

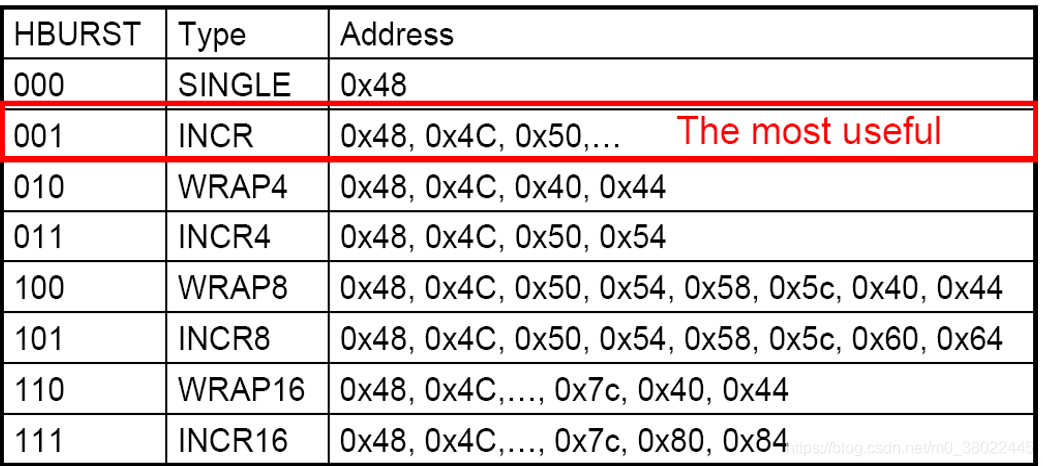

AHB中的突發操作,增量突發訪問連續地址并且突發中的每次傳輸地址僅是前一次地址的一個增量;對于回環突發,如果傳輸的起始地址并未和突發(x 拍)中字節總數對齊那么突發傳輸地址將在達到邊界處回環。例如,一個四拍回環突發的字(4 字節)訪問將在 16 字節邊界回環。因此,如果傳輸的起始地址是 0x34,那么它將包含四個到地址 0x34、0x38、0x3C 和 0x30;突發信息通過HBURST[2:0]進行判斷:

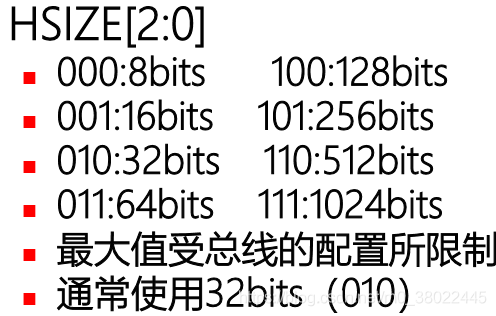

一次突發傳輸的數據總量可以用節拍數(1/4/8/16)乘以每拍數據的字節數來計算,每拍字節數由 HSIZE[2:0]指示:

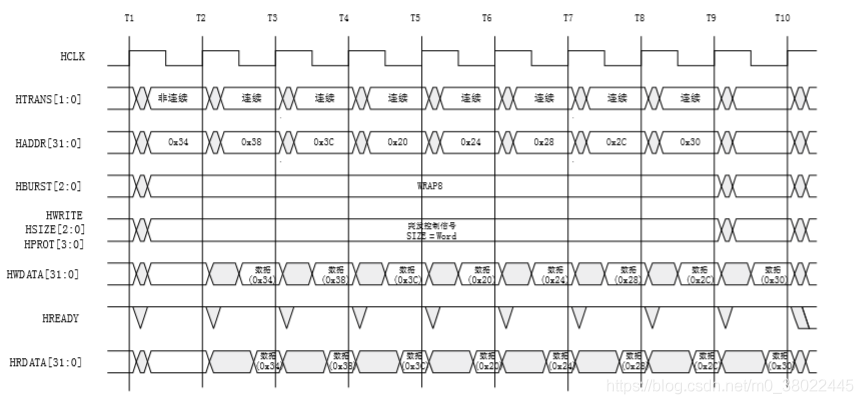

八拍回環突發傳輸時序(HSIZE=010):

8拍4字節,32為邊界,時序圖可見0x3C后回卷至0x20

AHB傳輸方向:HWRITE為高,該信號表示一個寫傳輸并且主機將數據傳輸到寫數據總線HWDATA[31:0]。當該信號為低時將會執行一個讀傳輸并且從機必須產生數據到讀數據總線HRDATA[31:0]

HPROT[3:0]信號:,提供總線訪問的附加信息并且是給那些希望執行某種保護級別的模塊使用的,用于表示傳輸是否為一次預取指/特權模式訪問或用戶模式訪問,對于帶有存儲器管理單元的總線主機來說這些信號也表示當前訪問是帶高速緩存(cache)還是帶緩沖的(buffer)。并不是所有總線主機都能產生正確的保護信息,因此建議從機在沒有嚴格必要的情況下不要使用 HPROT 信號。

文章出處:【微信公眾號:FPGA之家】

責任編輯:gt

-

處理器

+關注

關注

68文章

19535瀏覽量

231859 -

soc

+關注

關注

38文章

4243瀏覽量

219899 -

總線

+關注

關注

10文章

2914瀏覽量

88695

原文標題:SoC設計之AMBA總線-AHB總線詳解

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DA14531-00000FX2 超低功耗藍牙5.1 SOC芯片介紹

如何優化總線系統的性能

RISC-V芯片中使用的各種常用總線釋義

SOPC、SoC 、FPGA的異同優缺點介紹及常見應用場景

AI高性能計算平臺是什么

如何優化SOC芯片性能

usb主機控制器位于ahp總線上嗎

Astra? SL系列SL1640詳細介紹,嵌入式物聯網處理器SoC

AMBA總線協議的基本原理和應用場景

現場總線的種類介紹及其特點分析

混合信號 SOC 產品用戶指南

SoC設計中總線協議AXI4與AXI3的主要區別詳解

多軸高性能EtherCAT總線運動控制器ZMC408CE硬件介紹

SoC設計AHB高級高性能總線的詳細介紹

SoC設計AHB高級高性能總線的詳細介紹

評論