本來講一講FPGA的重構(gòu),在說FPGA重構(gòu)之前,需要先了解FPGA的配置方式。

FPGA 配置

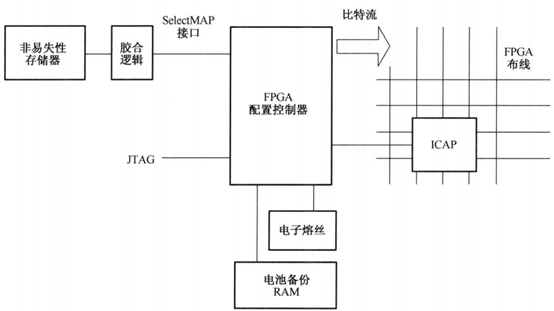

所有現(xiàn)代FPGA的配置分為兩類:基于SRAM的和基于非易失性的。其中,前者使用外部存儲(chǔ)器來配置FPGA內(nèi)的SRAM后者只配置一次。 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置技術(shù),其主要優(yōu)點(diǎn)是系統(tǒng)設(shè)計(jì)更加簡單、不需要外部存儲(chǔ)器和配置控制器、功耗低、成本低和FPGA配置時(shí)間更快。最大的缺點(diǎn)在于配置是固定的。 大多數(shù)現(xiàn)代FPGA都是基于SRAM包括Xilinx Spartan和Virtex系列。每個(gè)FPGA上電后或在后續(xù)的FPGA配置期間,從外部非易失性存儲(chǔ)器中讀取比特流,由配置控制器處理,并加載到內(nèi)部配置SRAM中。SRAM保持了配置邏輯、IO、嵌入式存儲(chǔ)器、布線、時(shí)鐘、收發(fā)器和其他FPGA原語等所有的設(shè)計(jì)信息。 下圖是Xilinx 的配置結(jié)構(gòu)。

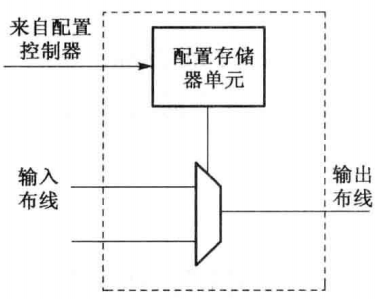

配置是由FPGA內(nèi)部的配置控制器執(zhí)行。比特流存儲(chǔ)在外部非易失性存儲(chǔ)器(如Flash)中。外部存儲(chǔ)器通過使用SelectMAP接口連接到配置控制器,這是Xilinx特有的。額外的膠合邏輯可能需要架起SelectMAP和外部存儲(chǔ)器接口之間的橋梁。此外,比特流可以通過JTAG或ICAP加載到配置控制器中。比特流可以選擇加密,以提高安全性。內(nèi)部電池備份RAM(BBR)和eFuse保存用于比特流解密的加密密鑰。 FPGA配置存儲(chǔ)器也稱為配置存儲(chǔ)器單元,它的每一位與比特流中的對(duì)應(yīng)位一起初始化。每個(gè)存儲(chǔ)器單元的輸出連接到可配置的功能塊上,如LUT寄存器、BRAM10、布線等。圖2是配置存儲(chǔ)器單元連接到多路復(fù)用器,以設(shè)置FPGA架構(gòu)中元件之間的特定布線路徑。在FPGA配置階段,邏輯狀態(tài)被置位為1或0。

圖 2 FPGA 的布線配置

Xilinx 的 FPGA 配置模式

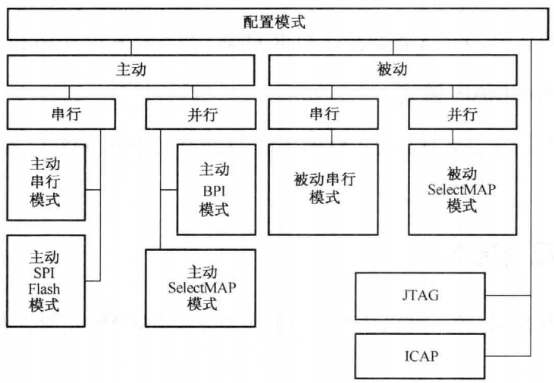

多種FPGA配置模式可滿足不同的使用模式。圖3是XilinxFPGA配置模式的分類。

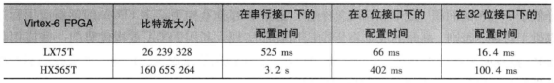

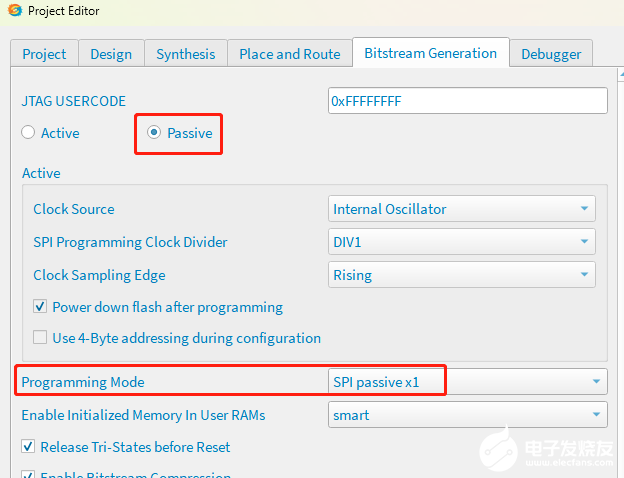

圖3FPGA配置模式的分類 配置模式分為兩類:主動(dòng)(master)模式和被動(dòng)(slave)模式。在主動(dòng)配置模式下,F(xiàn)PGA控制配置過程。在被動(dòng)模式下,由外部設(shè)備(如單片機(jī)、CPLD或其他FPGA)控制FPGA的配置過程。此外,還有兩個(gè)特殊的配置模式,即使用JTAG和內(nèi)部配置訪問端口(ICAP) 有4種數(shù)據(jù)寬度支持不同的外部存儲(chǔ)器:32位、16位、8位、1位(串行)。下面是配置模式的簡要介紹。 JTAG JTAG接口主要在調(diào)試期間使用。為了與Xilinx Chip Scope和IMPACT軟件應(yīng)用程序接口,特殊的適配器連接到專用FPGA引腳上。 ICAP 專用的ICAP原語用于與用戶邏輯的接口,在FPGA架構(gòu)內(nèi)進(jìn)行配置。 主動(dòng)串行模式 在主動(dòng)串行模式中,F(xiàn)PGA控制Xilinx Platform Flash,以提供配置數(shù)據(jù)Xilinx Platform Flash是一種特殊的非易失性存儲(chǔ)器,旨在通過使用Select MAP接口直接與Xilinx FPGA接口。 主動(dòng)SPI Flash模式 在主動(dòng)SPI Flash模式中,F(xiàn)PGA控制串行SPI閃存,以提供配置數(shù)據(jù)。 主動(dòng)Selec tMAP模式 在主動(dòng)Select MAP模式中,F(xiàn)PGA控制Xilinx Platform Flash,以提供8位或16位的配置數(shù)據(jù)。 主動(dòng)BPI模式 在主動(dòng)BPI模式中,F(xiàn)PGA控制并行NOR Flash,以提供8位或16位的配置數(shù)據(jù)。 被動(dòng)串行和Select MAP模式 在被動(dòng)串行模式下,外部設(shè)備(如單片機(jī)、CPLD或其他FPGA)控制FPGA的配置過程。 設(shè)計(jì)FPGA配置方案 對(duì)于特定設(shè)計(jì)來說,有一些設(shè)計(jì)考慮用于選擇最合適的FPGA配置方案。主要的選擇標(biāo)準(zhǔn)是 ?選擇是否通過外部設(shè)備(被動(dòng)模式)或由FPGA本身(主動(dòng)模式)控制配置過程。從系統(tǒng)復(fù)雜性角度來看,主動(dòng)模式最簡單,但未必適合所有設(shè)計(jì)。被動(dòng)模式接口作為簡單的串行接口,直接連接到處理器的10引腳,讀取比特流數(shù)據(jù)進(jìn)人配置控制器。 ?選擇外部非易失性存儲(chǔ)器的類型和大小,用于存儲(chǔ)一個(gè)或多個(gè)FPGA比特流。盡管與FPGA的成本相比,外部存儲(chǔ)器的成本相對(duì)較低,但仍然是不可忽略的。設(shè)計(jì)者可以在SHFlash并行NOR Flash或Xilinx Platform Flash之間進(jìn)行選擇。在某些設(shè)計(jì)中,F(xiàn)PGA可以使用連接到被動(dòng)模式下的FPGA配置控制器直接配置。 ?數(shù)據(jù)寬度的選擇—串行、8位、16位或32位—影響配置速度和FPGA中用于設(shè)計(jì)的10數(shù)目。 ?現(xiàn)場(chǎng)升級(jí)配置比特流可以是一個(gè)重要的需求。配置方案必須解決當(dāng)比特流正在編程進(jìn)入非易失性存儲(chǔ)器時(shí)發(fā)生損壞的情況。 ?Xilinx FPGA提供了一個(gè)選項(xiàng),用來加密在更高設(shè)計(jì)安全要求情況下的比特流。解密密鑰可以存儲(chǔ)在內(nèi)部的BBR或者eFuse中。BBR存儲(chǔ)器是易失性的,需要外部電池。使用BBR與使用非易失性eFuse相比,重新編程相對(duì)容易。 計(jì)算配置時(shí)間 在許多應(yīng)用中,F(xiàn)PGA配置時(shí)間很關(guān)鍵,要準(zhǔn)確估計(jì)配置方案選擇過程中的時(shí)間是很重要的。配置時(shí)間取決于比特流大小、時(shí)鐘頻率和配置接口的數(shù)據(jù)寬度,按下列公式定義: 配置時(shí)間=比特流大小x時(shí)鐘頻率x數(shù)據(jù)寬度 表1提供了配置接口在不同數(shù)據(jù)寬度下,對(duì)于使用50MHz時(shí)鐘的最小和最大Xilinx Virtex-6 FPGA的預(yù)期配置時(shí)間。 表 1 FPGA 配置時(shí)間

Xilinx 配置相關(guān)的原語

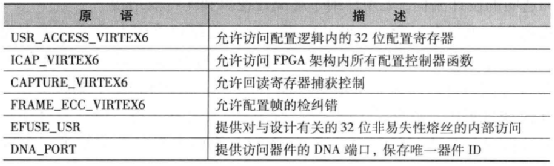

表 2 提供了 Xilinx FPGA 支持的與配置相關(guān)的原語列表。 表 2 Xilinx Virtex-6 配置相關(guān)的原語

文章出處:【微信公眾號(hào):OpenFPGA】

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1629文章

21744瀏覽量

603614 -

收發(fā)器

+關(guān)注

關(guān)注

10文章

3429瀏覽量

106018 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7493瀏覽量

163873

原文標(biāo)題:【Vivado那些事】FPGA的配置方式

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

易靈思FPGA PS配置模式--v7

高級(jí)定時(shí)器PWM輸入模式的配置方法

PCM5142如何在FPGA中通過SPI配置寄存器?

固化FPGA配置芯片的方式

配置直接測(cè)試模式的低功耗藍(lán)牙器件應(yīng)用說明

易靈思Trion FPGA PS配置模式--update(6)

FPGA如何估算分析功耗

FPGA的配置模式有哪些?具體配置過程是怎樣的?

AMD FPGA中MicroBlaze的固化流程詳解

AMD Xilinx 7系列FPGA的Multiboot多bit配置

FPGA分類

ESP32-S3模組是怎么配置低功耗模式的?低功耗模式下功耗大概是多少?

FPGA的配置模式的分類及應(yīng)用分析

FPGA的配置模式的分類及應(yīng)用分析

評(píng)論