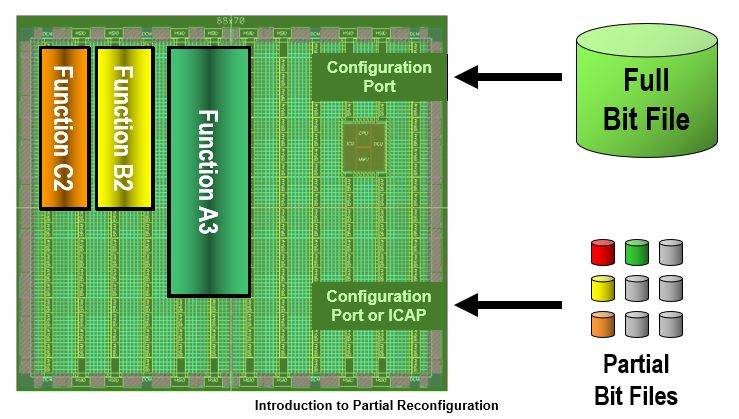

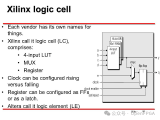

所謂FPGA動態(tài)可重構(gòu)技術(shù),就是要對基于SRAM編程技術(shù)的FPGA實(shí)現(xiàn)全部或部分邏輯資源的動態(tài)功能變換。根據(jù)實(shí)現(xiàn)重構(gòu)的面積不同,動態(tài)可重構(gòu)技術(shù)又可分為全局重構(gòu)和局部重構(gòu)。

1、何為局部動態(tài)可重構(gòu)

局部動態(tài)可重構(gòu)可以簡單的理解為通過下載局部分區(qū)bit 文件來動態(tài)修改對應(yīng)分區(qū)的邏輯功能,同時其余分區(qū)的邏輯功能持續(xù)運(yùn)行而不中斷。

2、局部動態(tài)可重構(gòu)技術(shù)的優(yōu)勢

a、系統(tǒng)靈活性:可以在保持通信連接的同時執(zhí)行更多的系統(tǒng)功能;

b、降低FPGA資源和成本:通過分時復(fù)用的方式降低FPGA硬件尺寸;

c、降低功耗:通過卸載掉暫時不用的局部邏輯的方式降低FPGA功耗;

3、FPGA局部動態(tài)重構(gòu)流程

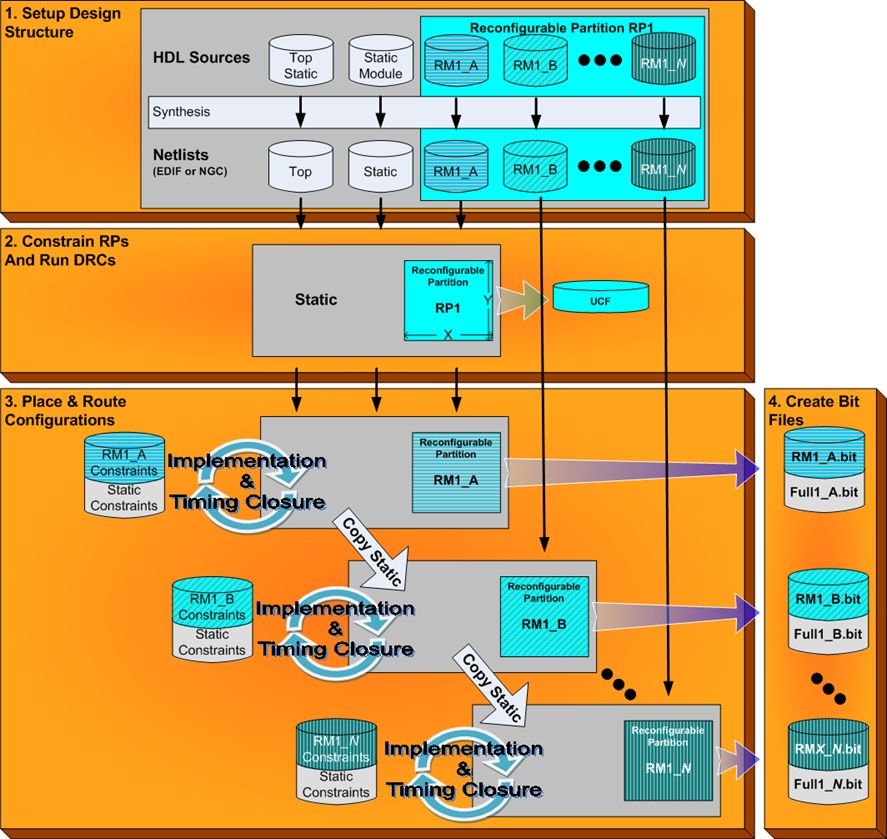

a、規(guī)劃系統(tǒng)整體框架和可重構(gòu)模塊框架,編寫各模塊HDL代碼,綜合生成各子模塊網(wǎng)表文件;

b、規(guī)劃分區(qū)以及給各分區(qū)分配足夠資源,創(chuàng)建各分區(qū)及靜態(tài)部分的時序約束文件,執(zhí)行DRC檢查;

c、對各分區(qū)進(jìn)行布局布線配置;

d、遍歷各種可能的配置,編譯生成全局bit文件和可重構(gòu)模塊的局部bit文件。

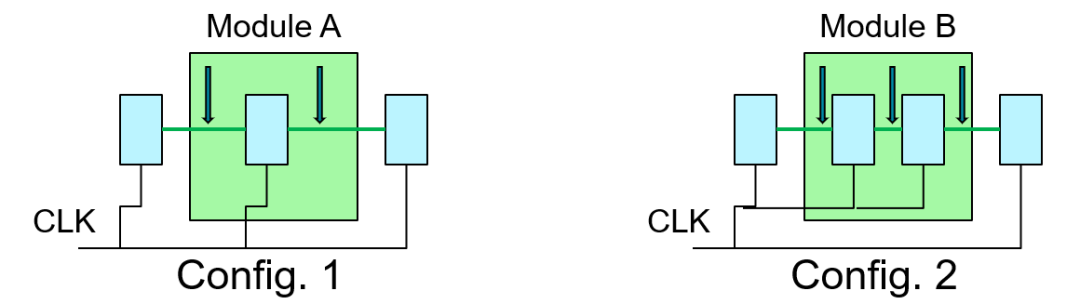

4、局部動態(tài)可重構(gòu)的時序問題

如上圖所示,局部重構(gòu)會帶來時序路徑的變化,使得局部可重構(gòu)工程的時序約束問題變得更加復(fù)雜。

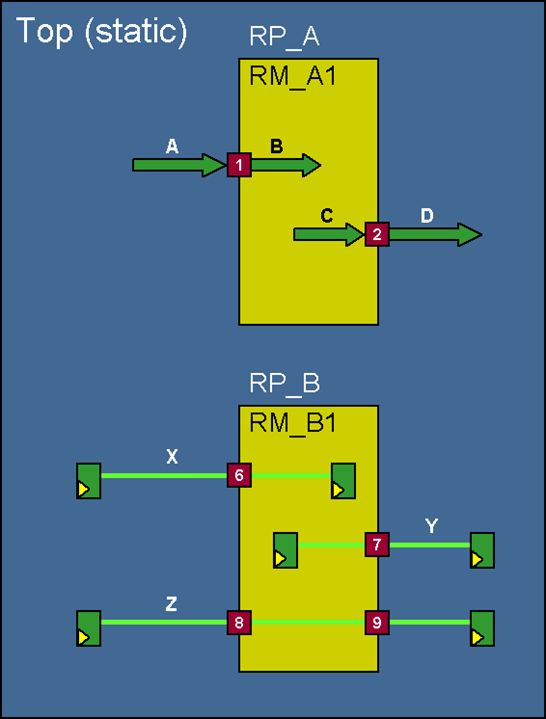

解決方法:在靜態(tài)邏輯和可重構(gòu)模塊間的信號傳遞路徑上添加代理邏輯點(diǎn),如下圖紅色數(shù)字點(diǎn),將單條時序路徑分割為兩個獨(dú)立的部分,然后分別對兩部分的路徑進(jìn)行單獨(dú)約束,以達(dá)到時序要求。

文章出處:【微信公眾號:OpenFPGA】

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

代碼

+關(guān)注

關(guān)注

30文章

4779瀏覽量

68525

原文標(biāo)題:淺析FPGA局部動態(tài)可重構(gòu)技術(shù)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

基于相變材料的可重構(gòu)超構(gòu)表面用于圖像處理

C2000 F28004x系列MCU PLL鎖相失敗問題解決方案

【電磁兼容技術(shù)案例分享】對地電容接地點(diǎn)差異導(dǎo)致輻射發(fā)射問題解決案例

麥格納為中國本土汽車制造商提供可重構(gòu)座椅系統(tǒng)

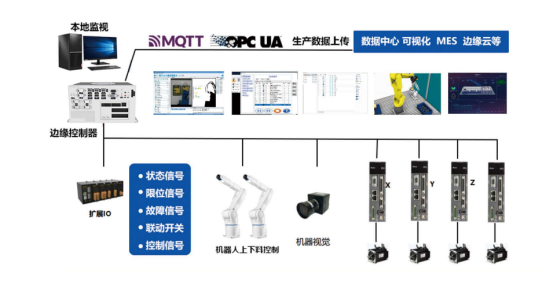

可重構(gòu)柔性裝配產(chǎn)線:AI邊緣控制技術(shù)的嶄新探索

可重構(gòu)柔性裝配產(chǎn)線整體解決方案,智能化生產(chǎn)轉(zhuǎn)型的引領(lǐng)者

瑞薩發(fā)布下一代動態(tài)可重構(gòu)人工智能處理器加速器

【電磁兼容技術(shù)案例分享】由SGMII通訊導(dǎo)致的輻射發(fā)射高頻單支超標(biāo)問題解決案例

【電磁兼容技術(shù)案例分享】某控制器產(chǎn)品傳導(dǎo)電壓法超標(biāo)問題解決案例

FPGA動態(tài)可重構(gòu)技術(shù)是什么,局部動態(tài)可重構(gòu)的時序問題解決方案

FPGA動態(tài)可重構(gòu)技術(shù)是什么,局部動態(tài)可重構(gòu)的時序問題解決方案

評論