時序仿真與功能仿真的步驟大體相同,只不過中間需要添加仿真庫、網表(.vo)文件和延時(.sdo)文件。到了這里,問題來了,仿真庫、網表(.vo)文件和延時(.sdo)文件怎么獲得呢?網表(.vo)文件和延時(.sdo)文件,其實我們在自動仿真的配置仿真功能中已經生成了,當我們配置好仿真功能之后,我們在 Quartus 進行一次全編譯。

這時,我們打開 Quartus 工程目錄下 simulation/modelsim 中就能夠看到 Verilog_First.vo 和 Verilog_First_v.sdo 這兩個文件。我們將這兩個文件復制到我們的 manual_modelsim 文件夾下。

仿真庫,我們需要到我們 Altera的安裝目錄下,也就是 C:altera13.1modelsim_asealteraverilog 中找到 cycloneive 文件夾,然后我們將 cycloneive 文件夾也復制到我們的 manual_modelsim 文件夾下。萬事具備,接下來我們就可以打開我們的 ModelSim 軟件

通過該圖,我們可以看出,這個工程是我們之前做功能仿真的工程,當我們關閉 ModelSim之后,我們再次打開 ModelSim 這個軟件,它會自動記錄上一個我們使用的工程并打開。我們就直接在這個工程上進行更改,首先我們右鍵在彈出的菜單欄中找到【Add to Project】→【Existing File.。。】按鈕并點擊打開

在該對話框中我們點擊【Browse】,在彈出的對話框中我們找到 manual_modelsim 文件夾下的 Verilog_First.vo,然后將 Verilog_First.vo 添加至我們的 ModelSim 仿真工程中。接下來我們進行代碼全編譯,編譯完成后,我們在 ModelSim 的菜單欄中找到【Simulate】→【StartSimulation.。。】按鈕并點擊打開,我們打開 Libraries 標簽,將仿真庫添加至配置仿真環境中

這里我們需要注意的是,只添加一個 cycloneive 仿真庫是不夠的,我們還需要將我們ModeSim 仿真庫中的 altera_ver 庫添加進來

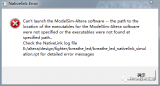

如果不知道需要選擇哪個庫,我們可以先直接運行仿真,這時候 ModelSim 控制窗口中會提示錯誤信息,我們根據錯誤信息便能夠分析出我們需要的庫名,然后我們再重復上述步驟添加完了仿真庫,接下來我們在 SDF 標簽頁面中添加 Verilog_First_v.sdo 文件

這里需要我們注意的是,因為的我們的實例化名是 i1,所以我們填寫的是/i1。添加完成之后,最后我們在返回 Design 標簽頁面中,找到 work 下的 Verilog_First_vlg_tst

在該頁面中,我們點擊【OK】就可以開始進行時序仿真了,到了這里,后面的工作就和我們的功能仿真是一樣的了。至此,我們 ModelSim 軟件的使用就講解完了。

編輯:jq

-

ModelSim

+關注

關注

5文章

174瀏覽量

47570

原文標題:ModelSim 使用【六】modelsim手動時序仿真

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【紫光同創盤古100Pro+開發板,MES2L676-100HP教程】盤古676系列——Modelsim的使用和do文件編寫

集成電路設計中靜態時序分析介紹

電源時序器3.0:數字化與網絡化的融合

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Efinity FIFO IP仿真問題 -v1

電源時序器常見故障維修

如何在ModelSim中添加Xilinx仿真庫

FPGA入門必備:Testbench仿真文件編寫實例詳解

fpga開發一般用什么軟件

ISE 關聯 Modelsim 詳細操作

最實用的Modelsim使用教程

fpga仿真文件怎么寫

ISE與Modelsim關聯設置的詳細操作步驟

基于ModelSim使用modelsim手動時序仿真教程

基于ModelSim使用modelsim手動時序仿真教程

評論