過去,FPGA設計者主要關心時序和面積使用率問題。但隨著FPGA不斷取代ASSP和ASIC器件,設計者們現正期望能夠開發低功耗設計,在設計流程早期就能對功耗進行正確估算,以及管理和對與FPGA相關的各種內部電壓及I/O電壓排序。

電源管理已成為FPGA設計者的一個重要考慮因素,特別是在設計便攜式、電池供電的產品時。通過功率監控設計技術能夠減少功耗、增強可靠性、降低生產成本,并減少對電源和冷卻的要求。

設計者可能會面臨的與FPGA電源相關的主要問題如下:系統級電源要求是什么?將要消耗多少電流?要求多大的電壓水平以及上電和斷電問題?器件的溫度條件如何,在該設計給定的溫度環境下器件能否可靠地工作?在電路板上是否需要針對發熱器件內置冷卻裝置?

電源理論

在電子器件中,功率通常被定義為電流做功的量。器件往往將電能轉換為熱能,但遺憾的是,除非是設計一個加熱器或者是電燈泡,否則在大多數應用中熱都被認為是無用的。了解FPGA的熱動力學原理將有助于設計者選擇事半功倍的方法來降低功耗。總功耗是某些類型的低功耗器件以及工藝節點和器件封裝特性的函數。

功耗的AC部分(與電路資源相關)是功耗的動態部分。AC功耗與電路資源的工作頻率和操作狀態,以及電路資源的數量直接成正比。以下等式說明了降低供電電壓(最主要的因素)、開關電容、節點的轉換頻率或信號轉換頻率是如何影響功耗的。

CMOS FPGA的功耗主要來自兩個方面:靜態與動態。式中的功耗用焦耳/秒或者瓦特來表示 :

式中各字符的含義為:P-功率(焦耳/秒或瓦特);V-電壓(焦耳/庫侖或伏特);I-電流(庫侖/秒或安培);R-電阻(歐姆);-每個節點的轉換頻率;C-開關電容;V2DD-電源電壓;F-頻率(每秒轉換的次數)。

PStatic相對于PDynamic的功耗隨處理節點而變化。在130納米和90納米器件中,靜態功耗是總功耗的一小部分。例如,假定一個內部邏輯工作頻率50MHz、I/O工作頻率250MHz的設計實例,在130納米FPGA(如LatticeECP或LatticeXP系列)中PStatic約為10%,而在90納米的LatticeECP2或LatticeXP2中則PStatic約為20%。

動態的轉換操作以及負載電容的充/放電消耗了大部分能量,這在很大程度上是由用戶設計來決定的。在65納米和更小的工藝節點上,這一傳統會發生變化。

晶體管物理特性在尺寸較小時會發生變化,這使得靜態泄漏非常大。由于晶體管泄漏不斷增加,靜態功耗成指數增長。靜態功耗在65納米處超過動態功耗。萊迪思(Lattice)半導體公司和其它FPGA供應商主要采用改進制造工藝,以及混合使用不同類型晶體管的方法來處理這些問題。

AC功耗與電路資源的工作頻率和操作狀態,以及電路資源的數量直接成正比。以上PDynamic等式指出了供電電壓(最主要的因素)、開關電容、節點的轉換頻率以及信號轉換頻率是如何影響功耗的。

隨著FPGA工藝的尺寸在縮小,使得設計者從更小的晶體管和IC裸片所帶來的功耗減小中獲益。但增加的時鐘速度和大尺寸設計往往在某種程度上抵消了這些好處。FPGA結構單元的相關功耗在不同的工藝節點之間也會發生變化。

例如,130納米LatticeECP和90納米LatticeECP2/M FPGA的各部分電路資源、走線以及LUT、寄存器、嵌入式存儲器塊(EBR)等邏輯的動態功耗比例進行了比對。這里假定設計中的邏輯部分利用率為90%、PLL/DLL、存儲器、DSP等嵌入式ASIC的利用率為100%,采用混合LVCMOS 1.2V和LVDS 2.5V DDR信號標準的I/O的利用率為80%。

雖然90納米器件中的總功耗可能有所下降,但I/O所占功耗的比例大大增加。對于一個特定的器件系列而言,這將影響采用何種降低功耗的策略。

熱管理

熱是IC工作時的副產品,必須利用工藝確保FPGA工作在規定的結溫范圍之內。只要溫度不超過指定的環境溫度和硅片結溫的上限,半導體器件就能正常工作。當超過溫度上限時,IC會停止正常工作并將被損壞。在大功率應用或高工作溫度下采用IC時,熱管理是絕對必要的。

為避免出現可靠性方面的問題,半導體供應商在器件數據表中規定了最大允許結溫。設計工程師應對其特定設計進行熱分析以便確保器件和封裝不超過結溫要求。內部數據是相對的,實際值取決于各種因素,例如裸片尺寸、焊盤尺寸、氣流、電源,PCB設計及應用本身。

盡管總功耗、環境溫度、熱阻和氣流都對器件的熱有影響,但器件數據表中規定的結溫(Tj)無疑是最關鍵的因素。例如帶有各種結構塊(包括DSP、存儲器和SERDES I/O)的LatticeECP2/M,商業級器件允許的結溫是0℃至85℃,工業級器件為-40℃至100℃。器件工作在上述范圍內時,AC特性能夠得到保證。這種器件工藝的結溫可靠性限制是125℃。了解供電電壓的最大最小值會有助于設計者降低靜態功耗。

工作在較高溫度下的器件同樣意味著有較大的靜態電流(SICC)。在給定溫度下SICC和總ICC(靜態ICC和動態ICC)的差值提供可用動態預算。如果器件運行時的動態ICC高于這一預算,總ICC也比預算值高,則將導致裸片溫度上升至超過規定的工作條件。器件的結溫受諸多因素的影響,例如功率、環境溫度,熱阻或氣流。減少一個或多個因素會引起變化以減少器件的結溫。

當考慮熱耗散時,用到了熱阻的概念。在IC中,熱阻(()表示對于裸片表面耗散的每瓦功率(熱)而言,裸片結點的穩態溫升超過一個給定的參考值。它的單位是℃/W。最普通的例子是熱阻Junction-to-Ambient (JA(℃/W),以及熱阻Junction-to-Case (JC(℃/W)。另外一個因素是熱阻Junction-to-Board (JB(℃/W)。

除了器件和封裝,電路的熱特性取決于工作溫度、器件功耗以及系統散熱能力。器件的最大結溫計算如下:

TJ = TA + P * θJA (1)

TJ = TC + P * θJC (2)

TJ = TB + P * JB (3)

式中的TJ、TA、TC和TB分別為結溫、環境溫度、表面(或封裝)溫度和電路板溫度(℃)。P是器件的總耗散功率。(JA通常用于自然和強制的對流冷卻系統。當器件封裝具有一個直接安裝在PCB板或散熱片上的高導電性外殼時,(JC非常有用。(JB則在與器件封裝相鄰的電路板溫度已知的情況下使用。

對于功率(P=Vcc * Icc)因素而言,ICC可通過各個器件數據表的功耗來估算,或者視為功率評估軟件的輸出。下圖列出了各種不同IC封裝的熱阻((JA和(JC)特性,并展示了某些封裝類型的優勢以及氣流和靜止空氣環境的對比。

當設計一個系統時,設計者必須確保器件工作在系統環境所規定的溫度范圍之內。這個問題應在設計系統之前重點考慮。利用FPGA功率評估工具,設計者能夠預測器件的發熱并估計動態功耗預算。在設計電路板之前估計器件的工作溫度還使設計者能夠更好地對功率預算和氣流進行規劃。

管理功耗

對于一個設計者必須解決功耗問題的目標應用,應采用功耗逼近的方法。第一步,設計者應尋找降低功耗的RTL。事半功倍的方法包括目標嵌入式模塊、小型FSM的格雷(gray)編碼,采用可減小尺寸而對性能影響不大的方式來組織各個模塊。如果FPGA是高密度的90納米器件,則應該對I/O編程和轉換進行仔細考慮以節省功率。其次,應該采用可節省功耗的綜合、布局和布線優化,例如寄存器再定時和面積優化。最后,可反映實際工作情況的強大測試平臺將有助于用功率評估軟件創建用于后仿真分析的精確的活動因子和轉換速率因子。

有許多設計技術可以幫助降低系統的整體功耗。

減小靜態功耗的方法包括:

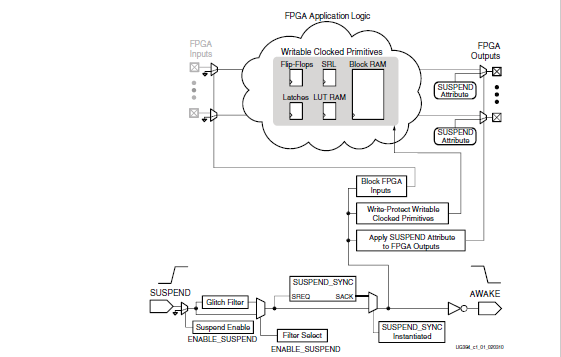

使用睡眠模式(如果提供的話)。例如在系統不工作期間,可以把LatticeXP “C”(VCC= 1.8/2.5/3.3V)器件設置成睡眠模式。睡眠模式期間待機電流可減小1000倍。如果電源處于工作范圍內,則無需切換電源。

減小工作電壓。采用器件規范中VCC和VCCJ的較低值。

利用以下方法盡可能地減小工作溫度:采用較低熱阻能更好散熱的封裝;將散熱片和散熱層放置在PCB板上器件的周圍;采用諸如機械導管和風扇等氣流技術。

減小I/O的開關電容和頻率。

當睡眠模式時對I/O去耦。如果無法實現的話,關閉內核電壓,只留下VCCO。

減小I/O電壓擺幅。使I/O驅動盡可能地低。例如,如果驅動3.3V CMOS,可以嘗試采用2.5V~3.0V VCCO。這樣做會降低抗噪聲能力,但對減小功耗十分有益。I/O采用低電壓標準。

利用壓擺率控制來減小輸出開關電流。一些FPGA能提供對LVCMOS或LVTTL輸出緩沖器的控制,這些緩沖器能被配置成低噪聲性能或者高速性能。

減小動態(AC)的方法:

優化綜合資源。減小設計在器件間的跨度。在緊湊型設計中采用較少的布線資源以減少功耗。

用嵌入式ASIC模塊。現代FPGA中EBR、DSP和PCS模塊在通用LUT/寄存器邏輯上的功耗較低。

采用計數器/FSM模塊的信號編碼優化。例如,16位二進制計數器平均只有12%的活動因子,7位二進制計數器平均有28%的活動因子。另一方面,7位線性反饋移位寄存器(LFSR)能以50%活動因子進行翻轉(即觸發),這會導致較高的功耗。由于活動因子小于10%,格雷碼計數器在每個時鐘邊沿僅有一位發生變化,因此耗用的功率最少。

采用優化的時鐘頻率。由于動態功耗直接與工作頻率成正比,這樣可以減小功耗。設計者必須確定設計的某部分是否工作在較低時鐘速率下,以減少功耗。

采用門控時鐘優化。由于時鐘信號始終都在轉換,會消耗大量功率,所以門控時鐘能幫助減少同步寄存器中過多的轉換操作。應該將門控時鐘列為FPGA布線資源的最高優先級。

時分復用(TDM)類型算法。

同步計數器與異步計數器實現。

FPGA功率評估工具

和仿真類似,FPGA熱分析是一種與傳統FPGA實現工具并行運作的驗證流程。在面向萊迪思FPGA的ispLEVER設計工具流程中,設計者可以在任何階段評估功耗:即利用功率計算器進行綜合前、布線后和仿真后評估。FPGA功率計算軟件工具通常可使設計者在三個不同的精確級上估計功耗:

驅動估計,此時手工輸入占用的電路資源和轉換頻率。

Post-PAR,此時面向一個更精確的使用模型引入后布局和布線。

后仿真,此時為獲得更精確的活動因子和轉換速率模型,導入由HDL仿真器產生的轉換頻率。

功率計算器采用諸如器件特性、電壓、溫度、器件參數差異、氣流、散熱片、使用的資源、活動因子和頻率等各種輸入參數來計算器件的功耗。計算器求出功耗的靜態(DC)和動態(AC)部分,以及預計的結溫(TJ)。

在進行綜合前,用邏輯塊的活動因子和I/O切換率估算切換頻率。如果在布局和布線后使用功率計算器,則可以通過本地電路描述(NCD)數據庫導入實際的器件利用率。系統采用post-map、 post-place或post-route NCD的結果時,功率計算是最準確的。基于仿真結果含有活動因子和切換率的可選VCD文件將進一步增加精確性。

可從下列方程得出AC功率:

總AC功率(資源)= KRESOURCE * fMAX * AFRESOURCE * NRESOURCE

其中,KRESOURCE是針對資源的功率常數(mW/MHz)。fMAX是運行時的最高頻率,用MHz量度頻率。

AFRESOURCE是針對資源的活動因子。活動因子為開關頻率的百分比。NRESOURCE是設計中所用資源的數目。

活動因子(或AF%)被定義為信號激活或轉換輸出時的頻率(或時間)的百分比。與時鐘域相關的大部分資源以與時鐘相同的頻率百分比運行或轉換。功率計算器的使用者可以手工輸入參數,或者引入基于模擬結果的活動因子。

可針對每個布線資源、輸出或者PFU計算出AF。如果沒有模擬結果,那么對于一個占用約30% 到70%器件資源的設計,通常推薦AF%在15% 至25%之間。AP精確性取決于時鐘頻率、設計的激勵信號和最終的輸出。

I/O功耗的關鍵輸入參數是I/O轉換速率。用戶提供的信號(輸入情況下)或者作為設計輸出(輸出情況下)的信號決定了I/O的操作情況。I/O的轉換速率定義了它們的操作狀況。下列方程定義了輸出的轉換速率(或者TR),單位用MHz表示。

轉換速率(MHz) = 1/2 * fMAX * AF%

本文小結

設計中最關鍵的因素之一是降低系統的功耗,特別對于手持設備和其它現代電子產品而言。降低功耗的技術多種多樣,這取決于目標器件的類型和設計的特性。理解FPGA功耗、靜態和動態功耗、內核與I/O資源將影響降低功耗的策略。采用節省功率的設計技術以及估計方法將有助于設計者滿足目標器件的工作規范要求。

編輯:jq

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603260

原文標題:FPGA設計中的電源管理

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

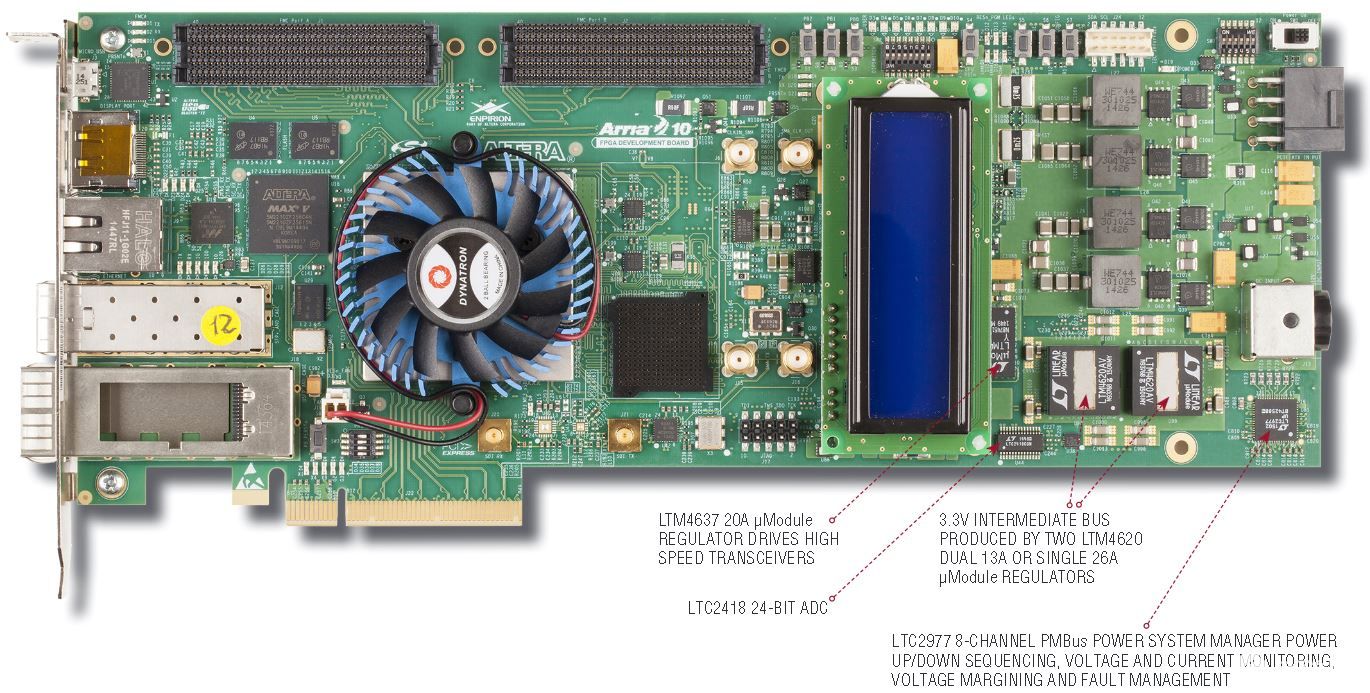

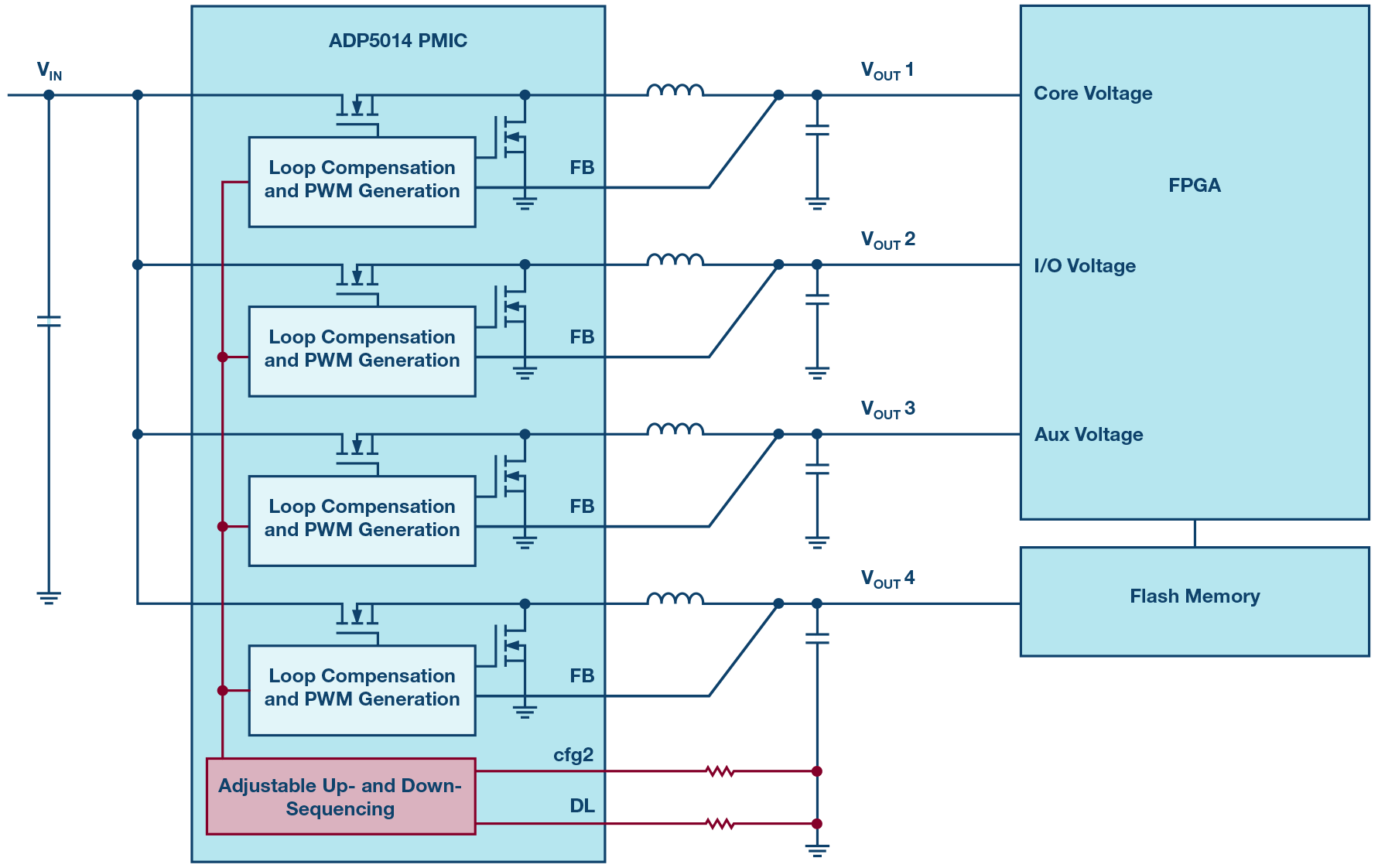

基于FPGA應用設計優秀電源管理解決方案

適用于FPGA、GPU和ASIC系統的電源管理

適用于FPGA、GPU和ASIC系統的電源管理

基于FPGA應用設計優秀電源管理解決方案

如何有效的管理FPGA設計中的時序問題

TI將數字電源管理應用于Xilinx FPGA設計

spartan-6 FPGA電源管理的用戶指南資料免費下載

詳解FPGA中的電源管理創新分析介紹

篇1:如何為FPGA選擇合適的電源管理方案

避免FPGA、GPU和ASIC系統電源管理中的調試周期

FPGA設計中的電源管理

FPGA設計中的電源管理

評論