MSI和MSI-X中斷機制

在PCI總線中,所有需要提交中斷請求的設備,必須能夠通過INTx引腳提交中斷請求,而MSI機制是一個可選機制。而在PCIe總線中,PCIe設備必須支持MSI或者MSI-X中斷請求機制,而可以不支持INTx中斷消息。

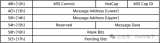

在PCIe總線中,MSI和MSI-X中斷機制使用存儲器寫請求TLP向處理器提交中斷請求,下文為簡便起見將傳遞MSI/MSI-X中斷消息的存儲器寫報文簡稱為MSI/MSI-X報文。

不同的處理器使用了不同的機制處理這些MSI/MSI-X中斷請求,如PowerPC處理器使用MPIC中斷控制器處理MSI/MSI-X中斷請求,本章將在第6.2節(jié)中介紹這種處理情況;而x86處理器使用FSB Interrupt Message方式處理MSI/MSI-X中斷請求。

不同的處理器對PCIe設備發(fā)出的MSI報文的解釋并不相同。但是PCIe設備在提交MSI中斷請求時,都是向MSI/MSI-X Capability結構中的Message Address的地址寫Message Data數據,從而組成一個存儲器寫TLP,向處理器提交中斷請求。

有些PCIe設備還可以支持Legacy中斷方式[1]。但是PCIe總線并不鼓勵其設備使用Legacy中斷方式,在絕大多數情況下,PCIe設備使用MSI或者MSI/X方式進行中斷請求。

PCIe總線提供Legacy中斷方式的主要原因是,在PCIe體系結構中,存在許多PCI設備,而這些設備通過PCIe橋連接到PCIe總線中。這些PCI設備可能并不支持MSI/MSI-X中斷機制,因此必須使用INTx信號進行中斷請求。

當PCIe橋收到PCI設備的INTx信號后,并不能將其直接轉換為MSI/MSI-X中斷報文,因為PCI設備使用INTx信號進行中斷請求的機制與電平觸發(fā)方式類似,而MSI/MSI-X中斷機制與邊沿觸發(fā)方式類似。

這兩種中斷觸發(fā)方式不能直接進行轉換。因此當PCI設備的INTx信號有效時,PCIe橋將該信號轉換為Assert_INTx報文,當這些INTx信號無效時,PCIe橋將該信號轉換為Deassert_INTx報文。

與Legacy中斷方式相比,PCIe設備使用MSI或者MSI-X中斷機制,可以消除INTx這個邊帶信號,而且可以更加合理地處理PCIe總線的“序”。目前絕大多數PCIe設備使用MSI或者MSI-X中斷機制提交中斷請求。

MSI和MSI-X機制的基本原理相同,其中MSI中斷機制最多只能支持32個中斷請求,而且要求中斷向量連續(xù),而MSI-X中斷機制可以支持更多的中斷請求,而并不要求中斷向量連續(xù)。

與MSI中斷機制相比,MSI-X中斷機制更為合理。本章將首先介紹MSI/MSI-X Capability結構,之后分別以PowerPC處理器和x86處理器為例介紹MSI和MSI-X中斷機制。

[1] 通過發(fā)送Assert_INTx和Deassert_INTx消息報文進行中斷請求,即虛擬中斷線方式。

MSI/MSI-X Capability結構

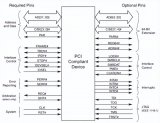

PCIe設備可以使用MSI或者MSI-X報文向處理器提交中斷請求,但是對于某個具體的PCIe設備,可能僅支持一種報文。在PCIe設備中含有兩個Capability結構,一個是MSI Capability結構,另一個是MSI-X Capability結構。通常情況下一個PCIe設備僅包含一種結構,或者為MSI Capability結構,或者為MSI-X Capability結構。

MSI Capability結構

MSI Capability結構共有四種組成方式,分別是32和64位的Message結構,32位和64位帶中斷Masking的結構。MSI報文可以使用32位地址或者64位地址,而且可以使用Masking機制使能或者禁止某個中斷源。

?Capability ID字段記載MSI Capability結構的ID號,其值為0x05。在PCIe設備中,每一個Capability結構都有唯一的ID號。

?Next Pointer字段存放下一個Capability結構的地址。

?Message Control字段。該字段存放當前PCIe設備使用MSI機制進行中斷請求的狀態(tài)與控制信息,如表6 1所示。

表6 1 MSI Cabalibities結構的Message Control字段

| Bits | 定義 | 描述 |

|---|---|---|

| 15:9 | Reserved | 保留位。系統軟件讀取該字段時將返回全零,對此字段寫無意義。 |

| 8 | Per-vector Masking Capable | 該位為1時,表示支持帶中斷Masking的結構;如果為0,表示不支持帶中斷Masking的結構。該位對系統軟件只讀,該位在PCIe設備初始化時設置。 |

| 7 | 64 bit Address Capable | 該位為1時,表示支持64位地址結構;如果為0,表示只能支持帶32位地址結構。該位對系統軟件只讀,該位在PCIe設備初始化時設置。 |

| 6:4 | Multiple Message Enable | 該字段可讀寫,表示軟件分配給當前PCIe設備的中斷向量數目。系統軟件根據Multiple Message Capable字段的大小確定該字段的值。在系統的中斷向量資源并不緊張時,Multiple Message Capable字段和該字段的值相等;而資源緊張時,該字段的值可能小于Multiple Message Capable字段的值。 |

| 3:1 | Multiple Message Capable | 該字段對系統軟件只讀,表示當前PCIe設備可以使用幾個中斷向量號,在不同的PCIe設備中該字段的值并不不同。當該字段為0b000時,表示PCIe設備可以使用1個中斷向量;為0b001、0b010、0b011、0b100和0b101時,表示使用4、8、16和32個中斷向量;而0b110和0b111為保留位。該字段與Multiple Message Enable字段的含義不同,該字段表示,當前PCIe設備支持的中斷向量個數,而Multiple Message Enable字段是系統軟件分配給PCIe設備實際使用的中斷向量個數。 |

| 0 | MSI Enable | 該位可讀寫,是MSI中斷機制的使能位。該位為1而且MSI-X Enable位為0時,當前PCIe設備可以使用MSI中斷機制,此時Legacy中斷機制被禁止。一個PCIe設備的MSI Enble和MSI-X Enable位都被禁止時,將使用INTx中斷消息報文發(fā)出/結束中斷請求[1]。 |

Message Address字段。當MSI Enable位有效時,該字段存放MSI存儲器寫事務的目的地址的低32位。該字段的31:2字段有效,系統軟件可以對該字段進行讀寫操作;該字段的第1~0位為0。Message Upper Address字段。如果64 bit Address Capable位有效,該字段存放MSI存儲器寫事務的目的地址的高32位。

Message Data字段,該字段可讀寫。當MSI Enable位有效時,該字段存放MSI報文使用的數據。該字段保存的數值與處理器系統相關,在PCIe設備進行初始化時,處理器將初始化該字段,而且不同的處理器填寫該字段的規(guī)則并不相同。

如果Multiple Message Enable字段不為0b000時(即該設備支持多個中斷請求時),PCIe設備可以通過改變Message Data字段的低位數據發(fā)送不同的中斷請求。Mask Bits字段。PCIe總線規(guī)定當一個設備使用MSI中斷機制時,最多可以使用32個中斷向量,從而一個設備最多可以發(fā)送32種中斷請求。

Mask Bits字段由32位組成,其中每一位對應一種中斷請求。當相應位為1時表示對應的中斷請求被屏蔽,為0時表示允許該中斷請求。系統軟件可讀寫該字段,系統初始化時該字段為全0,表示允許所有中斷請求。該字段和Pending Bits字段對于MSI中斷機制是可選字段,但是PCIe總線規(guī)范強烈建議所有PCIe設備支持這兩個字段。

Pending Bits字段。該字段對于系統軟件是只讀位,PCIe設備內部邏輯可以改變該字段的值。該字段由32位組成,并與PCIe設備使用的MSI中斷一一對應。該字段需要與Mask Bits字段聯合使用。

當Mask Bits字段的相應位為1時,如果PCIe設備需要發(fā)送對應的中斷請求時,Pending Bits字段的對應位將被PCIe設備的內部邏輯置1,此時PCIe設備并不會使用MSI報文向中斷控制器提交中斷請求;

當系統軟件將Mask Bits字段的相應位從1改寫為0時,PCIe設備將發(fā)送MSI報文向處理器提交中斷請求,同時將Pending Bit字段的對應位清零。在設備驅動程序的開發(fā)中,有時需要聯合使用Mask Bits和Pending Bits字段防止處理器丟棄中斷請求[2]。

MSI-X Capability結構

MSI-X Capability中斷機制與MSI Capability的中斷機制類似。PCIe總線引出MSI-X機制的主要目的是為了擴展PCIe設備使用中斷向量的個數,同時解決MSI中斷機制要求使用中斷向量號連續(xù)所帶來的問題。

MSI中斷機制最多只能使用32個中斷向量,而MSI-X可以使用更多的中斷向量。目前Intel的許多PCIe設備支持MSI-X中斷機制。與MSI中斷機制相比,MSI-X機制更為合理。

首先MSI-X可以支持更多的中斷請求,但是這并不是引入MSI-X中斷機制最重要的原因。因為對于多數PCIe設備,32種中斷請求已經足夠了。而引入MSI-X中斷機制的主要原因是,使用該機制不需要中斷控制器分配給該設備的中斷向量號連續(xù)。

如果一個PCIe設備需要使用8個中斷請求時,如果使用MSI機制時,Message Data的[2:0]字段可以為0b000~0b111,因此可以發(fā)送8種中斷請求,但是這8種中斷請求的Message Data字段必須連續(xù)。在許多中斷控制器中,Message Data字段連續(xù)也意味著中斷控制器需要為這個PCIe設備分配8個連續(xù)的中斷向量號。

有時在一個中斷控制器中,雖然具有8個以上的中斷向量號,但是很難保證這些中斷向量號是連續(xù)的。因此中斷控制器將無法為這些PCIe設備分配足夠的中斷請求,此時該設備的“Multiple Message Enable”字段將小于“Multiple Message Capable”。

而使用MSI-X機制可以合理解決該問題。在MSI-X Capability結構中,每一個中斷請求都使用獨立的Message Address字段和Message Data字段,從而中斷控制器可以更加合理地為該設備分配中斷資源。

與MSI Capability寄存器相比,MSI-X Capability寄存器使用一個數組存放Message Address字段和Message Data字段,而不是將這兩個字段放入Capability寄存器中,本篇將這個數組稱為MSI-X Table。從而當PCIe設備使用MSI-X機制時,每一個中斷請求可以使用獨立的Message Address字段和Message Data字段。

除此之外MSI-X中斷機制還使用了獨立的Pending Table表,該表用來存放與每一個中斷向量對應的Pending位。這個Pending位的定義與MSI Capability寄存器的Pending位類似。MSI-X Table和Pending Table存放在PCIe設備的BAR空間中。MSI-X機制必須支持這個Pending Table,而MSI機制的Pending Bits字段是可選的。

1 MSI-X Capability結構

MSI-X Capability結構比MSI Capability結構略微復雜一些。在該結構中,使用MSI-X Table存放該設備使用的所有Message Address和Message Data字段,這個表格存放在該設備的BAR空間中,從而PCIe設備可以使用MSI-X機制時,中斷向量號可以并不連續(xù),也可以申請更多的中斷向量號。

?Capability ID字段記載MSI-X Capability結構的ID號,其值為0x11。在PCIe設備中,每一個Capability都有唯一的一個ID號。

?Next Pointer字段存放下一個Capability結構的地址。

?Message Control字段,該字段存放當前PCIe設備使用MSI-X機制進行中斷請求的狀態(tài)與控制信息,如表6 2所示。

表6 2 MSI-X Capability結構的Message Control字段

| Bits | 定義 | 描述 |

|---|---|---|

| 15 | MSI-X Enable | 該位可讀寫,是MSI-X中斷機制的使能位,復位值為0,表示不使能MSI-X中斷機制。該位為1且MSI Enable位為0時,當前PCIe設備使用MSI-X中斷機制,此時INTx和MSI中斷機制被禁止。當PCIe設備的MSI Enble和MSI-X Enable位為0時,將使用INTx中斷消息報文發(fā)出/結束中斷請求。 |

| 14 | Function Mask | 該位可讀寫,是中斷請求的全局Mask位,復位值為0。如果該位為1,該設備所有的中斷請求都將被屏蔽;如果該位為0,則由Per Vector Mask位,決定是否屏蔽相應的中斷請求。Per Vector Mask位在MSI-X Table中定義,詳見下文。 |

| 10:0 | Table Size | MSI-X中斷機制使用MSI-X Table存放Message Address字段和Message Data字段。該字段用來存放MSI-X Table的大小,該字段對系統軟件只讀。 |

Table BIR(BAR Indicator Register)。該字段存放MSI-X Table所在的位置,PCIe總線規(guī)范規(guī)定MSI-X Table存放在設備的BAR空間中。該字段表示設備使用BAR0~5寄存器中的哪個空間存放MSI-X table。

該字段由三位組成,其中0b000~0b101與BAR0~5空間一一對應。Table Offset字段。該字段存放MSI-X Table在相應BAR空間中的偏移。PBA(Pending Bit Array) BIR字段。

該字段存放Pending Table在PCIe設備的哪個BAR空間中。在通常情況下,Pending Table和MSI-X Table存放在PCIe設備的同一個BAR空間中。PBA Offset字段。該字段存放Pending Table在相應BAR空間中的偏移。

2 MSI-X Table

由上圖可見,MSI-X Table由多個Entry組成,其中每個Entry與一個中斷請求對應。其中每一個Entry中有四個參數,其含義如下所示。

?Msg Addr。當MSI-X Enable位有效時,該字段存放MSI-X存儲器寫事務的目的地址的低32位。該雙字的31:2字段有效,系統軟件可讀寫;1:0字段復位時為0,PCIe設備可以根據需要將這個字段設為只讀,或者可讀寫。不同的處理器填入該寄存器的數據并不相同。

?Msg Upper Addr,該字段可讀寫,存放MSI-X存儲器寫事務的目的地址的高32位。

?Msg Data,該字段可讀寫,存放MSI-X報文使用的數據。其定義與處理器系統使用的中斷控制器和PCIe設備相關。

?Vector Control,該字段可讀寫。該字段只有第0位(即Per Vector Mask位)有效,其他位保留。當該位為1時,PCIe設備不能使用該Entry提交中斷請求;為0時可以提交中斷請求。該位在復位時為0。Per Vector Mask位的使用方法與MSI機制的Mask位類似。

3 Pending Table

在Pending Table中,一個Entry由64位組成,其中每一位與MSI-X Table中的一個Entry對應,即Pending Table中的每一個Entry與MSI-X Table的64個Entry對應。與MSI機制類似,Pending位需要與Per Vector Mask位配置使用。

當Per Vector Mask位為1時,PCIe設備不能立即發(fā)送MSI-X中斷請求,而是將對應的Pending位置1;當系統軟件將Per Vector Mask位清零時,PCIe設備需要提交MSI-X中斷請求,同時將Pending位清零。

[1] 此時PCI設備配置空間Command寄存器的“Interrupt Disable”位為1。[2] MSI機制提交中斷請求的方式類似與邊界觸發(fā)方式,而使用邊界觸發(fā)方式時,處理器可能會丟失某些中斷請求,因此在設備驅動程序的開發(fā)過程中,可能需要使用這兩個字段。

編輯:jq

-

PCI

+關注

關注

4文章

663瀏覽量

130251 -

PCIe

+關注

關注

15文章

1234瀏覽量

82581 -

中斷控制器

+關注

關注

0文章

59瀏覽量

9452

原文標題:PCIe中MSI和MSI-X中斷機制

文章出處:【微信號:gh_339470469b7d,微信公眾號:FPGA與數據通信】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

TMS320x280x、2801x、2804x DSP系統控制和中斷參考指南

單片機的中斷機制

TMS320C64x+和TMS320C674x的檢錯糾錯機制

esp32-korvo-v1.1編譯wake_word_detection程序報錯怎么解決?

千視N50 4K超高清編解碼器助力《英雄聯盟》MSI季中賽閃耀收官

STM32L051的MSI怎么校準的?

STM32L451VET6串口波特率紊亂引起的數據通信問題求解

STM32L151RBTX6在stop模式喚醒之后默認進入MSI,在工程里找不到是為什么?

STM32L031斷電重啟后,數據只能收到第一個字節(jié)是哪里出了問題?

使用stm32l072cbt6作為系統時鐘源,為什么生成的代碼對于systick的重裝載值是按MSI計算的?

MSI中斷簡介和生成方法

Linux內核PCIE基礎知識整理

簡述MSI和MSI-X中斷機制

簡述MSI和MSI-X中斷機制

評論