同步復(fù)位和異步復(fù)位

異步復(fù)位

異步復(fù)位是指無(wú)論時(shí)鐘沿是否到來(lái),只要復(fù)位信號(hào)有效,就對(duì)系統(tǒng)進(jìn)行復(fù)位。

RTL代碼如下:

always@(posedgeclkornegedgerst_n) if(!rst_n)b<=?1'b0; ?????????else?b?<=?a;

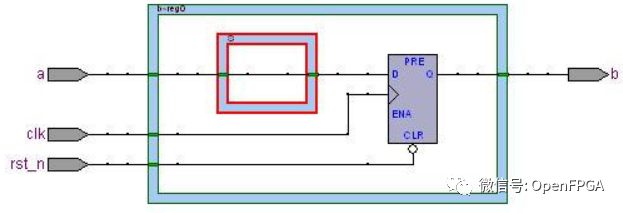

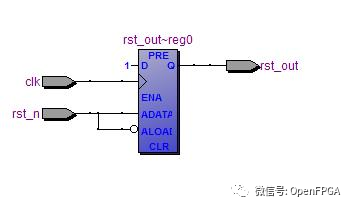

綜合后如下:

我們可以看到FPGA的寄存器都有一個(gè)異步的清零端(CLR),在異步復(fù)位的設(shè)計(jì)中這個(gè)端口一般就是接低電平有效的復(fù)位信號(hào)rst_n。即使說(shuō)你的設(shè)計(jì)中是高電平復(fù)位,那么實(shí)際綜合后會(huì)把你的復(fù)位信號(hào)反向后接這個(gè)CLR端。公眾號(hào):OpenFPGA

同步復(fù)位

同步復(fù)位是指只有在時(shí)鐘上升沿到來(lái)時(shí)才會(huì)對(duì)復(fù)位信號(hào)進(jìn)行采樣,也就是只有在時(shí)鐘上升沿時(shí),復(fù)位信號(hào)才有效。

其RTL代碼如下:

always@(posedgeclk) if(!rst_n)b<=?1'b0; ?????????else?b?<=?a;

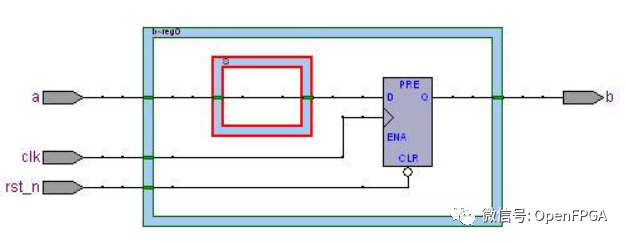

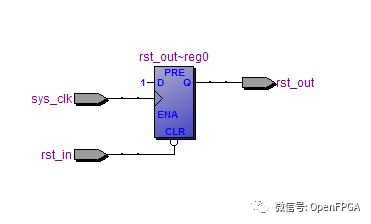

綜合后如下:

和異步復(fù)位相比,同步復(fù)位沒(méi)有用上寄存器的CLR端口,綜合出來(lái)的實(shí)際電路只是把復(fù)位信號(hào)rst_n作為了輸入邏輯的使能信號(hào)。那么,這樣的同步復(fù)位勢(shì)必會(huì)額外增加FPGA內(nèi)部的資源消耗。

那么同步復(fù)位和異步復(fù)位到底孰優(yōu)孰劣呢?

只能說(shuō),各有優(yōu)缺點(diǎn)。同步復(fù)位的好在于它只在時(shí)鐘信號(hào)clk的上升沿觸發(fā)進(jìn)行系統(tǒng)是否復(fù)位的判斷,這降低了亞穩(wěn)態(tài)出現(xiàn)的概率;它的不好上面也說(shuō)了,在于它需要消耗更多的器件資源,這是我們不希望看到的。FPGA的寄存器有支持異步復(fù)位專(zhuān)用的端口,采用異步復(fù)位的端口無(wú)需額外增加器件資源的消耗,但是異步復(fù)位也存在著隱患,特權(quán)同學(xué)曾說(shuō)過(guò)從沒(méi)有意識(shí)到也沒(méi)有見(jiàn)識(shí)過(guò)。異步時(shí)鐘域的亞穩(wěn)態(tài)問(wèn)題同樣的存在與異步復(fù)位信號(hào)和系統(tǒng)時(shí)鐘信號(hào)之間。公眾號(hào):OpenFPGA

上面的分析似乎都讓人意識(shí)到同步復(fù)位和異步復(fù)位都不可靠,那么如何將兩者結(jié)合,取長(zhǎng)補(bǔ)短呢?

異步復(fù)位、同步釋放

所謂異步復(fù)位,同步釋放就是在復(fù)位信號(hào)到來(lái)的時(shí)候不受時(shí)鐘信號(hào)的同步,而是在復(fù)位信號(hào)釋放的時(shí)候受到時(shí)鐘信號(hào)的同步。

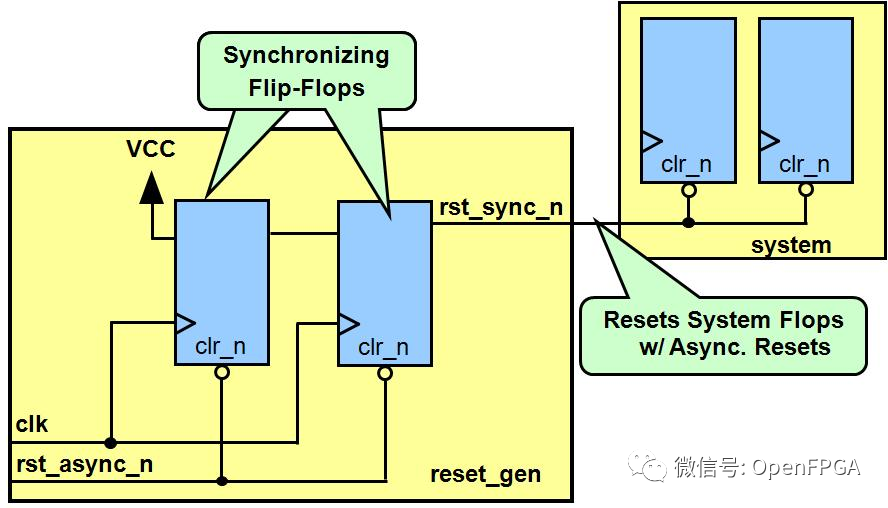

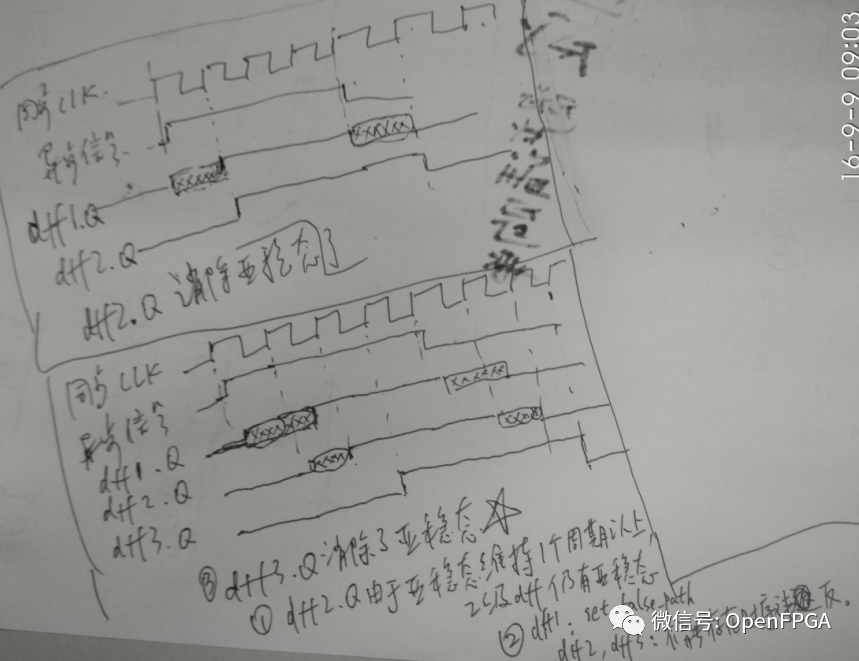

如下圖,單獨(dú)看方框左的復(fù)位策略,是一個(gè)異步復(fù)位電路,即復(fù)位信號(hào)有效時(shí)不管時(shí)鐘信號(hào)是否處于有效沿,輸出都會(huì)被復(fù)位,但是如果復(fù)位信號(hào)在時(shí)鐘信號(hào)的上升沿撤銷(xiāo)時(shí),這時(shí)候的輸出就是亞穩(wěn)態(tài)。

首先看一下怎么實(shí)現(xiàn)異步復(fù)位:當(dāng)rst_async_n有效時(shí),第二個(gè)D觸發(fā)器的輸出rst_sync_n就是低電平,方框左中的異步復(fù)位端口有效,輸出被復(fù)位。

然后是同步釋放:假設(shè)rst_async_n在clk的上升沿時(shí)撤除,那么第一級(jí)觸發(fā)器處于亞穩(wěn)態(tài),但是由于兩級(jí)觸發(fā)器的緩沖作用,第二級(jí)觸發(fā)器的輸入為clk到來(lái)前第一級(jí)觸發(fā)器的輸出,即為低電平。因此,此時(shí)第二級(jí)觸發(fā)器的輸出一定是穩(wěn)定的低電平,方框左中觸發(fā)器仍然處于復(fù)位狀態(tài)。在下一個(gè)clk到來(lái)時(shí),第一級(jí)觸發(fā)器的輸出已經(jīng)是穩(wěn)定的高電平了,故rst_sync_n已經(jīng)是穩(wěn)定的高電平,此時(shí)復(fù)位釋放。也就是同步釋放。公眾號(hào):OpenFPGA

通過(guò)上面分析可知:異步復(fù)位、同步釋放其最顯著特征是既保留了異步復(fù)位的功能,又避免了異步復(fù)位釋放時(shí)所面臨的recovery或者removal違例問(wèn)題。

那異步復(fù)位同步釋放是如何避免recovery和removal違例問(wèn)題的呢?如下代碼所示,是異步復(fù)位同步釋放的RTL code。

always@(posedgeclk,negedgerst_async_n) if(!rst_async_n)begin rst_s1<=?1'b0;?? rst_s2?<=?1'b0;?? end?? else?begin?? rst_s1?<=?1'b1;?? rst_s2?<=?rst_s1;?? end?? ? assign?rst_sync_n?=?rst_s2;??? endmodule?

從上述代碼可以看出,rst_async_n=0時(shí),rst_sync_n會(huì)被立即復(fù)位為0,輸出到后續(xù)電路用于異步復(fù)位;rst_async_n=1時(shí),假設(shè)此時(shí)恰好在時(shí)鐘沿附近,會(huì)造成recovery或者removal的違例,但經(jīng)過(guò)DFF1和DFF2的兩級(jí)同步,rst_sync_n釋放沿與時(shí)鐘沿同步,送入到后續(xù)電路不會(huì)再有recovery和removal違例出現(xiàn)。

問(wèn)題1

如果沒(méi)有前面兩級(jí)觸發(fā)器的處理。異步信號(hào)直接驅(qū)動(dòng)系統(tǒng)的觸發(fā)器。會(huì)出現(xiàn)什么情況?

回答:很多人只知道觸發(fā)器D端口來(lái)源是異步的話,會(huì)因?yàn)榻⒈3謺r(shí)間的時(shí)序違反而在觸發(fā)器Q端口產(chǎn)生亞穩(wěn)態(tài)。但是不清楚,異步復(fù)位信號(hào)為什么會(huì)導(dǎo)致亞穩(wěn)態(tài)的產(chǎn)生。

首先,回顧理論教材里介紹的建立保持時(shí)間違反分析,教材一般都是拿沒(méi)有復(fù)位端口的D觸發(fā)器舉例。

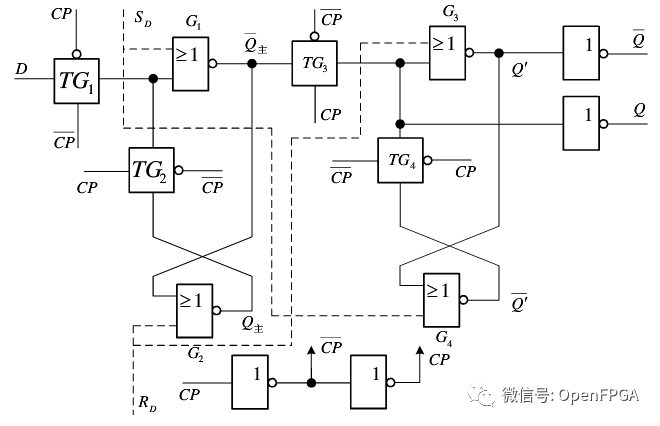

然后,畫(huà)出帶有異步復(fù)位端口的D觸發(fā)器,下圖帶異步復(fù)位Rd,并帶有異步置位端口Sd。公眾號(hào):OpenFPGA

由此得知,異步復(fù)位信號(hào)或者異步置位信號(hào),跟數(shù)據(jù)端口D信號(hào),沒(méi)有什么區(qū)別,都會(huì)存在建立保持時(shí)間的違反,從而時(shí)序沖突,引發(fā)輸出亞穩(wěn)態(tài)。

問(wèn)題2

復(fù)位信號(hào)存在亞穩(wěn)態(tài),有危險(xiǎn)嗎?

回答:

亞穩(wěn)態(tài),出現(xiàn)的問(wèn)題或者麻煩,是在信號(hào)變化的時(shí)候,不能保證第一拍采樣的值是固定的。

如果信號(hào)穩(wěn)定,不會(huì)出現(xiàn)亞穩(wěn)態(tài)的。就是采樣后的跳變,時(shí)刻不確定,也許早,也許晚。

系統(tǒng)不希望這樣的未知狀態(tài)發(fā)生,系統(tǒng)希望知道在某一個(gè)時(shí)刻,后續(xù)邏輯需要的輸入信號(hào),是穩(wěn)定值。公眾號(hào):OpenFPGA

二級(jí)觸發(fā)器同步后,第二季觸發(fā)器的輸出基本上是穩(wěn)定值。后續(xù)邏輯根據(jù)穩(wěn)定值,會(huì)有穩(wěn)定的行為。這就是追求的系統(tǒng)穩(wěn)定性。

最好是系統(tǒng)一起復(fù)位釋放,但是時(shí)鐘域不同,不可能保證系統(tǒng)一起復(fù)位釋放。一般來(lái)說(shuō),系統(tǒng)復(fù)位釋放的順序,是需要保證的。否則系統(tǒng)就是不安全的。公眾號(hào):OpenFPGA

舉個(gè)例子,系統(tǒng)啟動(dòng)時(shí),內(nèi)核讀取啟動(dòng)指令,要powerdown某外設(shè);但是powerdown的邏輯要求外設(shè)和內(nèi)核沒(méi)有通信請(qǐng)求正在發(fā)生。此時(shí),外設(shè)比內(nèi)核先釋放復(fù)位的情況(復(fù)位釋放的時(shí)刻,外設(shè)有可能已經(jīng)開(kāi)始與內(nèi)核發(fā)生請(qǐng)求),與內(nèi)核比外設(shè)先釋放復(fù)位的情況(復(fù)位釋放的時(shí)刻,外設(shè)肯定與內(nèi)核沒(méi)有發(fā)生請(qǐng)求),是不一樣的,powerdown也許不能處理成功。

這也是異步復(fù)位信號(hào)需要同步釋放的原因,目的都是為了避免亞穩(wěn)態(tài)的產(chǎn)生。

問(wèn)題3

如果只做一級(jí)觸發(fā)器同步,如何?

回答:不可以。第一級(jí)觸發(fā)器的輸出,永遠(yuǎn)存在亞穩(wěn)態(tài)的可能。亞穩(wěn)態(tài),導(dǎo)致系統(tǒng)不會(huì)復(fù)位初始化到已知狀態(tài)。

當(dāng)?shù)谝患?jí)觸發(fā)器采樣異步輸入之后,允許輸出出現(xiàn)的亞穩(wěn)態(tài)可以長(zhǎng)達(dá)一個(gè)周期,在這個(gè)周期內(nèi),亞穩(wěn)態(tài)特性減弱。在第二個(gè)時(shí)鐘沿到來(lái)時(shí),第二級(jí)同步器采樣,之后才把該信號(hào)傳遞到內(nèi)部邏輯中去。第二級(jí)輸出是穩(wěn)定且已被同步了的。如果在第二級(jí)采樣時(shí)保持時(shí)間不夠,第一級(jí)的輸出仍然處于很強(qiáng)的亞穩(wěn)態(tài),將會(huì)導(dǎo)致第二級(jí)同步器也進(jìn)入亞穩(wěn)態(tài),但這種故障出現(xiàn)的概率比較小。公眾號(hào):OpenFPGA

一般情況下,兩級(jí)同步器總體的故障概率是一級(jí)同步器故障概率的平方。在大部分的同步化設(shè)計(jì)中,兩級(jí)同步器足以消除所有可能的亞穩(wěn)態(tài)了。

問(wèn)題4

兩級(jí)觸發(fā)器同步,就能消除亞穩(wěn)態(tài)嗎?

回答:不能。大大降低概率,如果幾十年出現(xiàn)一次,也無(wú)所謂了。畢竟芯片不會(huì)用幾十年,早就老化嚴(yán)重淘汰了。

問(wèn)題5

第一級(jí)觸發(fā)器的數(shù)據(jù)端口為什么是1’b1?回答:

如果第一級(jí)觸發(fā)器的數(shù)據(jù)端口,使用rst_async_n。綜合后的第一級(jí)觸發(fā)器電路圖如下

如果第一級(jí)觸發(fā)器的數(shù)據(jù)端口,使用1’b1。綜合后的第一級(jí)觸發(fā)器電路圖如下:

考慮到電路實(shí)現(xiàn)的資源,還是第2種方案最節(jié)省,為最佳設(shè)計(jì)。

https://blog.csdn.net/cainiaoyizhiyang/article/details/98479356https://blog.csdn.net/wordwarwordwar/article/details/79889725

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602997 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13312

原文標(biāo)題:FPGA中異步復(fù)位,同步釋放的理解

文章出處:【微信號(hào):gh_339470469b7d,微信公眾號(hào):FPGA與數(shù)據(jù)通信】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當(dāng)作同步復(fù)位還是異步復(fù)位?

異步復(fù)位同步釋放有多個(gè)時(shí)鐘域時(shí)如何處理 異步復(fù)位同步釋放的策略

異步復(fù)位異步釋放會(huì)有什么問(wèn)題?FPGA異步復(fù)位為什么要同步釋放呢?

verilog 異步復(fù)位同步釋放

同步復(fù)位與異步復(fù)位,同步釋放的對(duì)比疑問(wèn)

關(guān)于異步復(fù)位同步釋放理解與分析

FPGA設(shè)計(jì)中的異步復(fù)位同步釋放問(wèn)題

利用FPGA異步復(fù)位端口實(shí)現(xiàn)同步復(fù)位功能,釋放本性

詳細(xì)講解同步后的復(fù)位是同步復(fù)位還是異步復(fù)位?

同步復(fù)位與異步復(fù)位的區(qū)別

FPGA學(xué)習(xí)-異步復(fù)位,同步釋放

如何理解FPGA中異步復(fù)位和同步釋放

如何理解FPGA中異步復(fù)位和同步釋放

評(píng)論