盡管芯片正變得越來越復雜,但產品仍需更快地推向市場。高性能計算(HPC)、人工智能(AI)、5G、汽車及GPU等應用領域使芯片開發者面臨著巨大壓力,因為他們必須提供能滿足處理性能、帶寬、延遲和功耗要求的十億門級設計,以保證這些應用蓬勃發展。

在這種環境下,開發者希望利用設計和驗證工具在更短時間內完成更多工作。為滿足這些需求,芯片設計自動化(EDA)公司推出了強大的產品,幫助開發者在設計周期中及早發現并解決問題。

如何快速找到故障的根本原因?

硬件和軟件驗證的兩種主要方式各有優點: ●支持全自動流程的硬件仿真系統。速度遠超一般模擬器,并且能提供完全直觀的調試功能 ●原型設計系統通常比仿真器更快,可用于檢查時間更長的應用負載。此項工作往往需要開發者付出更多精力才能完成

在典型的驗證場景中,兩類系統都有用武之地。仿真適合設計不太成熟的情況,而在設計非常成熟時則可進行原型設計,從而快速發現極端情況。然而,業界一直希望仿真系統能夠進一步提升性能,同時保持其在調試和自動化方面的優勢。

調試在驗證過程中最耗費時間。2020年Wilson Research Group的功能驗證研究表明,驗證工程師花在調試工作上的時間大約占41%。然而,這項工作的重要性不容低估。因為越早發現并解決錯誤,設計和整體預算的成本就越低。事實上,在百億億次級調試時代,軟件應用在十億門級設計仿真中需要進行超過10億個周期的測試,這會進一步加劇調試吞吐量方面的挑戰。除了軟件復雜性和SoC規模不斷增大之外,還有其他一些因素,如芯片與芯片之間和外部通信要求不斷增加。而這些需要更快、更強大的仿真系統。

仿真在芯片設計中調試驗證軟硬件正確交互方面發揮著重要作用。通過快速鎖定測試失敗的根本原因,能夠加快芯片設計和驗證過程。

在單個平臺上進行10-MHz SoC仿真

正是在這種高壓環境下,電子器件公司持續投資購置快速仿真和原型驗證設施,為加速軟件啟動、SoC驗證和系統驗證提供基礎。然而,并非所有驗證系統都相同。有些情況下需要為同一個硬件驗證流程購買一套仿真系統,以及一套原型驗證系統,并且在這兩個系統之間來回切換,以完成硬件調試和軟件驗證。盡管這兩套系統可能采用共同的編譯和測試平臺方法,但仍需要為采購和維護兩套系統而支付成本。此外,從工作流程的角度需要管理兩個平臺不同項目同時運行的工作。

除了軟件啟動外,更好的驗證方法是采用運行速度更快的單個仿真系統。利用單一平臺,開發者可以使用一個通用的預約系統運行所有工作,從而更有效地執行調試計劃。還可以靈活地購買所需要的容量,而無需投資購置兩套系統。新思科技的ZeBu EP1 emulation system具有所有這些優勢,這是業界首個10-MHz仿真解決方案,是20億門級SoC設計的理想選擇。該系統基于系統中FPGA之間的直連架構,最大限度減少處理延遲,并提高性能。ZeBu EP1還提供: ●系統級調試,包括快速波形輸出 ●業內最低的總體成本,同時考慮了冷卻和電力等運營費用以及運行單個系統的更低總體開銷 ●高可靠性,這一點已通過新思科技ZeBu仿真系統的成功經驗得到了證明

ZeBu EP1為汽車、5G基礎設施、邊緣AI和HPC等領域的SoC提供了所需的容量和性能(即使完整的HPC SoC對于系統來說規模太大,ZeBu EP1也可以支持其大型IP塊)。ZeBu系列產品是新思科技Verification Continuum解決方案的組成部分,旨在幫助更早更快地發現SoC錯誤,更早啟動軟件并驗證整個系統。

責任編輯:haq

-

芯片

+關注

關注

455文章

50803瀏覽量

423502 -

soc

+關注

關注

38文章

4165瀏覽量

218232 -

新思科技

+關注

關注

5文章

798瀏覽量

50337

原文標題:新思科技Zebu EP1加速SoC驗證應對復雜芯片設計需求

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Minitab Workspace vs. Visio,你是在繪圖還是在解決問題?

探究全電池容量衰減的根本原因

單片機出現故障怎么維修

ESP32-C3因為射頻RF電容,導致無限重啟怎么解決?

電力電容器鼓肚的根本原因是什么

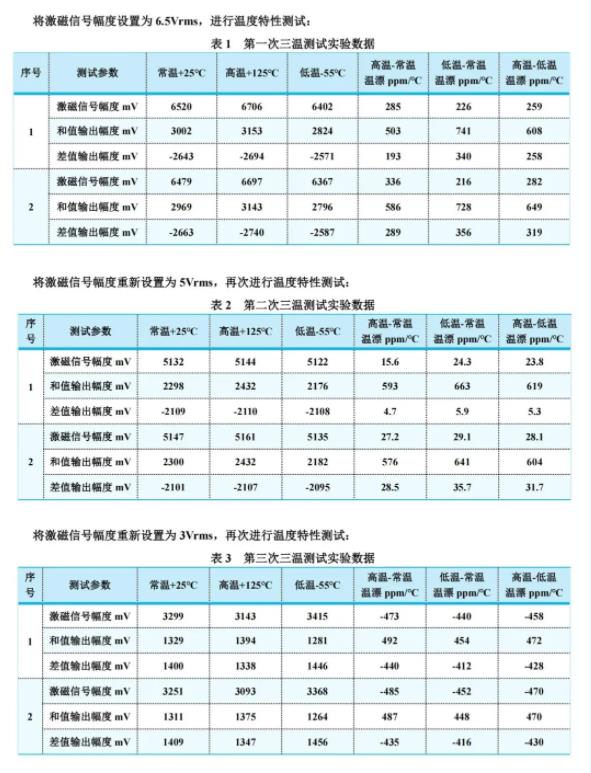

溫漂特性問題分析實驗 改善HJG598的溫漂與輸出噪聲

如何快速找到芯片設計故障的根本原因

如何快速找到芯片設計故障的根本原因

評論