電子發(fā)燒友網報道(文/程文智)不論我們設計的電子產品是應用在云計算、無線LTE、數據中心,還是物聯網、汽車、醫(yī)療保健,或者是航空航天等領域,系統(tǒng)內必然需要時鐘產品的支持,時鐘產品就如人類的脈搏一樣,只有在時鐘的支持下,電子產品才能正常工作。

那么時鐘產品有哪些種類,它們分別有什么特性,工程師在選用的時候需要注意些什么呢,我們今天就來一起聊一聊。

時鐘產品的分類

時鐘產品主要分為兩大類,一類是異步時鐘產品,它的功能是給本地單板提供工作時鐘,包括晶振、時鐘發(fā)生器,及時鐘緩沖器等等;另一類是同步時鐘產品,它的功能是跟蹤上下游時鐘產生同步之后的時鐘給下游使用,它主要包括濾抖芯片、同步以太網(SyncE)和IEEE1588時鐘產品等。

具體一點來分的話,工程師常用的時鐘產品主要是六個大類:

一是振蕩器,包括MEMS振蕩器和石英振蕩器,TCXO、MCXO、OCXO、EMXO、VCXO、VCSO都是石英振蕩器。值得一提的是MEMS振蕩器和石英振蕩器是有本質不同的。

二是時鐘生成器,主要是低抖動、低功耗的時鐘發(fā)生器。

三是時鐘分配器,它實際上是時鐘緩沖器,包括低附加抖動的各種各樣的緩沖器。詳細來看,有扇出緩沖器,零延時緩沖器,分頻器和多路開關等。

四是抖動衰減產品,這類主要用在網絡里,或者是上下游,進行時鐘濾抖的,比如抖動濾波,時鐘轉換等。

五是時鐘同步產品,包括同步以太網時鐘芯片和IEEE1588的時鐘芯片。

六是其他簡單的時鐘器件,包括555定時器,邏輯轉換器,交叉點開關,觸發(fā)器/邏輯門等等。

接下來我們來看一看這些不同類型的時鐘產品都有哪些特點,在選用不同類型的時鐘產品時,有哪些注意事項。

晶體振蕩器和MEMS振蕩器

振蕩器產品分為兩類,一類是傳統(tǒng)的石英晶體振蕩器,第二大類是MEMS振蕩器。

對于傳統(tǒng)的石英晶體振蕩器,它們通常是屬于模塊,而不是傳統(tǒng)意義上基于硅的芯片,MEMS振蕩器則是傳統(tǒng)意義上的芯片。為什么這么說呢?

對于傳統(tǒng)的石英晶體振蕩器,通常有晶體、XO、VCXO、TCXO、OCXO等幾種。

對于晶體而言,雖然它內部有振蕩電路,但是由于晶體是無源的,一般無法進行獨立振蕩,用戶通常需要在外面加上合適的電阻和電容,構成外部諧振電路,才能讓它產生用戶需要的頻率。

XO或時鐘振蕩器是最基礎的振蕩器,由晶體和基本驅動電路組成,內部不但集成了諧振電路,還集成了驅動電路。因此,用戶只需要提供一個穩(wěn)定的電源,就能產生所需要的頻點。但是由于沒有任何形式的補償,頻率穩(wěn)定基本上是依靠晶體本身的特性。

VCXO,即壓控晶體振蕩器,它內部有一個VC的壓控端,用戶可以通過調整VC壓控端的電壓,從而讓VCXO成為了一個頻率可以微調的時鐘輸出。也就是說,它可以依賴石英晶體的特性,通過施加外部電壓來控制振蕩器的輸出頻率變化。

TCXO,即溫補晶體振蕩器,通過附加的溫度補償電路來補償因環(huán)境溫度變化而引起的振蕩器頻率變化。它的內部包含一個溫度補償電路,當外部環(huán)境溫度變化的時候,溫度補償電路會去補償因為溫度的變化造成的晶體頻率的偏差,從而產生一個相對穩(wěn)定的頻率輸出。

但是,對于一些特殊的應用場合,TCXO仍然是不能滿足要求的,因此,另外一種產品應運而生了,那就是OCXO。

OCXO,即恒溫晶體振蕩器,它內部具有一個恒溫槽,恒溫槽會根據晶體不同的加工工藝,使恒溫槽保持在80~90℃的恒定范圍。也就是說諧振電路相當于工作在空調房內一樣,從而保證了諧振電路輸出頻率的相對穩(wěn)定。

不論是無源的晶振還是有源的晶振,除了諧振電路之外,還需要一些輔助的電路,比如說溫度補償電路,恒溫槽的控制電路等等。

也就是說,此類產品中的諧振電路和輔助電路其實是放置在一個類似PCB的基板上,再與晶體封裝起來,形成了一個振蕩器產品。因此,對于傳統(tǒng)的石英晶體振蕩器來說,它是一個模塊,而不是一個基于硅片的IC。

對于MEMS振蕩器而言,是完全不一樣的,它是采用硅晶圓生產工藝制造,并通過電極產生靜電場來激勵諧振器。也就是說,它完全基于硅片,因此,MEMS振蕩器是一個IC產品。

正是因為這樣,石英晶體振蕩器與MEMS振蕩器之間是有一些差異的。由于MEMS振蕩器是基于硅的芯片,因此,它在抗振動、抗沖擊、失效率、封裝和交貨時間,以及靈活性上,是遠遠領先于石英晶體振蕩器的。

但是,對于一些特殊的應用場合,比如頻率穩(wěn)定度要求很高的場合,OCXO的頻率穩(wěn)定度要更高。因此,一些特殊應用場合仍然會使用石英晶體振蕩器。

當然,隨著技術的進步,MEMS振蕩器的頻率穩(wěn)定度也在逐漸提升當中,業(yè)內目前有廠商可以提供與TCXO穩(wěn)定度相當的產品。

圖2:振蕩器的比較(來源:Microchip)

振蕩器產品有MEMS振蕩器、石英晶體振蕩器,以及原子鐘振蕩器。這一系列振蕩器產品中,他們的性能是完全不一樣的,比如說溫度穩(wěn)定性、老化率、24小時保持性能、相位噪聲性能等等,都是不一樣的。此外,功率和成本也完全不同。

工程師可以根據自己的實際情況去選擇合適的振蕩器產品,不管是哪種產品,那么通常需要關注哪些常見的參數呢?

一般來說,工程師在選擇振蕩器產品的時候,需要關注頻率穩(wěn)定性、初始容差、老化率、抖動、相位噪聲和保持性能等等。當然,對于一些特殊的應用場合,和一些特殊的振蕩器產品,還有一些特殊的參數需要去關注。

接下來,我們看一個OCXO的典型應用場景。

OCXO在外部控制器和其他電路的配合下,形成了一個閉環(huán)的模擬鎖相環(huán)(APLL),該APLL可以鎖定GPS提供的1pps的信號輸入,產生1pps的信號輸出和一個10MHz頻率的時鐘輸出,系統(tǒng)可以根據1pps的信號輸出和10MHz時鐘輸出做各種各樣的數據和信號處理。

時鐘發(fā)生器

時鐘發(fā)生器也可以稱為頻率合成器,一般來說需要外加晶體或振蕩器做為參考。時鐘發(fā)生器的主要功能是實現頻率變換,可以對參考源晶體或振蕩器頻率進行倍頻或降頻,從而產生1路或多路輸出。

在時鐘發(fā)生器的內部,實際上是一個模擬鎖相環(huán)(APLL),該APLL可以鎖定來自外部的參考時鐘,這個參考時鐘可以是上游提供的參考時鐘,也可以是振蕩器提供的參考時鐘。APLL可以把時鐘參考時鐘倍頻到高頻,比如將25MHz的信號倍頻到4GHz,然后基于4GHz再做分頻,從而產生各種各樣的頻率。

其實除了上面提到的APLL,還有數字鎖相環(huán)(DPLL),這兩者有何差異呢?對于APLL而言,固有抖動非常好,但它有自己的缺點,比如不夠靈活、帶寬不能做得很低、沒有辦法提供各種各樣的保持功能。

DPLL跟APLL恰好相反,它的固有抖動比較差,但是它非常靈活、帶寬可以做得很低、能提供非常優(yōu)秀的基于算法的保持功能。

但其實,不論是APLL,還是DPLL,他們都兩個共同點,一是他們都是低通濾波器;二是他們都是閉環(huán)的負反饋系統(tǒng)。

復雜的系統(tǒng)中通常有多路時鐘域,每個時鐘由獨立的晶體或振蕩器產生。相比之下,時鐘發(fā)生器具備諸多優(yōu)勢:高度集成、可代替多個晶體或振蕩器、占用電路板的空間少,以及可靠性高等。

那么,在選擇時鐘發(fā)生器時,需要考慮哪些參數呢?一般來說,主要考慮的參數有:輸出時鐘可以支持的頻率范圍、輸出時鐘可以支持的時鐘域、輸出時鐘可以支持的路數、抖動/相位噪聲等。

此外,還可根據需求考慮其他一些參數,比如輸出電平可以支持的類型、是否支持SSC擴頻時鐘、是否支持相位調節(jié)、是否需要零延時功能、是否支持默認加載配置等。

拿Microchip的ZL30267時鐘發(fā)生器來說,它內部有兩個APLL,它們同時鎖定到了同一個XO,然后產生了以太網絡需要的156.25MHz時鐘;PCIe系統(tǒng)所需要的100MHz時鐘;以及USB系統(tǒng)需要的48MHz時鐘。也就是說,通過這樣的時鐘發(fā)生器,可以產生各種各樣的頻點,給單板做工作時鐘。

時鐘緩沖器

當系統(tǒng)中需要多路時鐘信號時,最有效的產生方法是使用時鐘緩沖器。而時鐘緩沖器實際上是一個比較簡單的器件,本質上來說,它實現了時鐘的驅動,比如說前面有一個時鐘進來,可以通過時鐘緩沖器,實現多個相同頻段的輸出。

在選用時鐘緩沖器時,工程師除了關注輸入輸出,以及輸出頻率等常規(guī)參數之外,尤其要注意另外一個參數是附加抖動RMS。為什么關注該參數呢?因為對于時鐘緩沖器產品,是會劣化時鐘的,也就是說,一個好的,低抖動的時鐘輸入進來,經過時鐘緩沖器之后,時鐘的抖動會變大。那么,抖動變大之后的時鐘是否滿足應用的要求,這一點工程師需要多多關注一下。

濾抖芯片

濾抖芯片,顧名思義就是濾除抖動,既然可以濾除抖動,那么芯片內部必然是一個低通的濾波器,濾抖芯片通常會有兩種架構類型,第一種是基于模擬鎖相環(huán)的濾抖芯片,由于模擬鎖相環(huán)的帶寬不能做到非常低,因此基于模擬鎖相環(huán)的濾抖芯片不能實現非常好的濾抖效果。

另一種是基于數字鎖相環(huán)加上模擬鎖相環(huán)的濾抖芯片,這種芯片把DPLL和APLL的優(yōu)點結合在一起。

比如Microchip的ZL30169,其內部就是基于DPLL和APLL架構的濾抖芯片。它前面是輸入的參考時鐘,后面是參考時鐘的監(jiān)視器、DPLL模塊、APLL模塊,分頻器模塊,輸出的驅動電路等。

根據其內部框圖,可以看出,除了模塊之外,對于內部有DPLL模塊的鎖相環(huán)而言,通常還需要外部提供一個工作時鐘,該工作時鐘在給DPLL提供工作時鐘的同時,還會用這個工作時鐘來監(jiān)控輸入參考源的變化。

同步以太網和IEEE1588時鐘產品

同步以太網和IEEE 1588時鐘產品內部基本上采用了DPLL+APLL的架構。為什么采用這類架構呢,因為這樣可以利用APLL抖動性能好,DPLL比較靈活的特點。

同步以太網和IEEE 1588時鐘產品通常要滿足復雜的協(xié)議,比如物理層的7.813,7.862協(xié)議等。對于DPLL而言,它內部是可編程的,因此,我們可以在DPLL上面處理各自的算法,這個算法就可以保證滿足同步以太網和1588的相關協(xié)議。

一般來說,時鐘的同步有三種類型:頻率同步、相位同步,以及時間同步。它們之間是不一樣的。

對于頻率同步,他們之間的相差是固定的,但是沿是無法對齊的;對于相位同步,相差是固定的,沿也是對齊的,但每一個沿產生的時刻可能是不一樣的;而時間同步,每一個沿產生的時刻是一樣的,因此我們稱之為時間同步。

拿電信網絡來說,整個的電信網絡的時鐘頻率精度必須完全相同,才能完成相互通信;而電信網絡實際上是逐級逐跳傳遞同步信號的。具體來說,電信網絡最開始的高精度時鐘信號由原子時鐘產生,一般原子時鐘會作為第一跳的設備,第一級的設備會把同步信號傳遞到第二級,第二級會把同步信號傳遞給第三級、第四級等等。

逐級逐跳傳遞過程中,通過什么來實現的呢,其實就是通過同步以太網和IEEE1588來實現的。

具體來看一下同步以太網時鐘在具體設備和網絡中,是如何傳遞的,首先上游同步以太網會給PHY一個參考的工作時鐘,PHY收到時鐘后,會基于這個時鐘,把數據傳遞給下一級,在接收端,接收端會把時鐘和數據解出來,提取出來的時鐘,會再給鎖相環(huán)芯片,鎖相環(huán)芯片鎖定這個時鐘,產生一個新的時鐘,給PHY的SerDes,它再基于這個時鐘,把數據傳遞出去,從而實現了物理層的逐級逐跳的時鐘傳遞的過程。

設備的內部的同步是怎么樣來傳遞的?電信系統(tǒng)一般是多卡系統(tǒng),主備2個時鐘卡和多個線路卡,輸入同步信號從PHY接收器恢復傳輸到時鐘卡系統(tǒng)時鐘,再由時鐘卡處理后分發(fā)信號傳輸到所有線路卡PHY發(fā)送器。

時鐘卡和線路卡上都會放置鎖相環(huán)芯片,但是它們實現的功能是不一樣的,時鐘卡上的鎖相環(huán)可以濾除時序干擾(漂移),并在外部時序源暫時丟失時提供保持功能,以及滿足各種各樣的復雜協(xié)議;線路卡上的鎖相環(huán)芯片可以濾除抖動和轉換時鐘頻率。

IEEE 1588的傳遞跟同步以太網的傳遞有點不一樣。它是把時間信號放在報文內。逐級逐跳往下傳遞的。對數字鎖相環(huán),或者模擬鎖相環(huán)而言,它是一個低通濾波器,同時也是一個閉環(huán)的負反饋系統(tǒng),對于IEEE 1588而言,它也是是一個閉環(huán)的負反饋系統(tǒng)。但是它的反饋不在芯片內部,而在于板級,或者系統(tǒng)上。

聲明:本文由電子發(fā)燒友原創(chuàng),轉載請注明以上來源。如需入群交流,請?zhí)砑游⑿舉lecfans999,投稿爆料采訪需求,請發(fā)郵箱huangjingjing@elecfans.com。

編輯:jq

-

以太網

+關注

關注

40文章

5432瀏覽量

171897 -

振蕩器

+關注

關注

28文章

3833瀏覽量

139144 -

mems

+關注

關注

129文章

3937瀏覽量

190738 -

時鐘發(fā)生器

+關注

關注

1文章

200瀏覽量

67299

原文標題:不同類型時鐘產品的特性及選擇時的注意事項

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

不同類型時鐘產品的特性及選擇時的注意事項

同類型的RISCV核與ARM的核產品在使用上有那些區(qū)別?

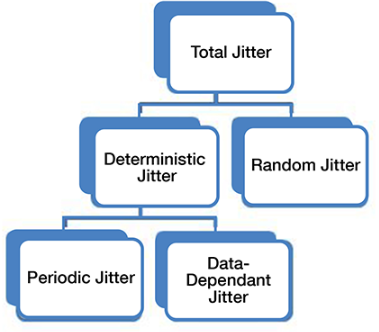

理解不同類型的時鐘抖動

光纖的基本類型如何選擇質量好和實用的光纖產品

不同類型的邊緣計算機應該如何選擇

不同類型的邊緣計算機如何選擇

不同類型電阻的特性資料下載

選擇人員定位系統(tǒng)時應該注意什么

選擇光纖線應該注意哪些問題-clan

如何識別不同類型的抖動

不同類型時鐘產品的特性及選擇時應該注意哪些

不同類型時鐘產品的特性及選擇時應該注意哪些

評論