關于Buck和Boost的,我已經寫了幾篇,不過很少提到PCB Layout,這篇就說說PCB Layout。

很多DCDC芯片的手冊都有對應的PCB Layout設計要求,有些還會提供一些Layout示意圖,都是大同小異的。

比如我隨便列幾點buck的設計要點:

1、輸入電容器和二極管在與IC相同的面,盡可能在IC最近處。

2、電感靠近芯片的SW,輸出電容靠近電感放置。

3、反饋回路遠離電感,SW和二極管等噪聲源。

那你知道這些要點都是怎么來的嗎?

如果拿到一個具體的芯片,因為芯片管腳分布的問題,可能這些條件不能同時滿足,那什么辦?到底孰輕孰重?

舉個Buck的例子

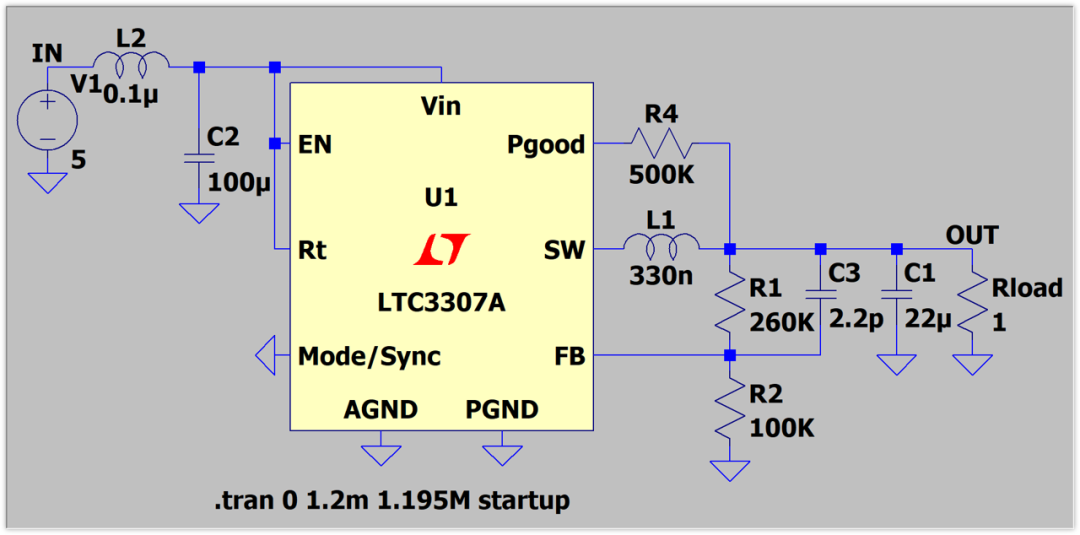

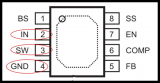

比如下面這個buck,它的管腳分布就不好。

SW在IN和GND之間,如果按照要點,直接將輸入濾波電容放到IN和GND旁邊,那么SW的信號就出不來,而電感也要求放在芯片旁邊,這就矛盾了。

芯片手冊推薦的layout倒是都就近放置了,但是它的方法是SW在輸入濾波電容底下走線,這是逗我嗎?這在現實中能做到?

我們不能采用芯片手冊推薦的這種方式,但事實是這種管腳分布的芯片多得是,那我們的Layout如何布局布線呢?

這個問題先不回答,我給大家說一個最根本的方法:

DCDC的Layout終極奧義——心中有環

心中有環

“環”,指的是有大電流流過的閉合回路。我們只要控制好這個環,Layout基本就成功一大半了。

下面來看為什么

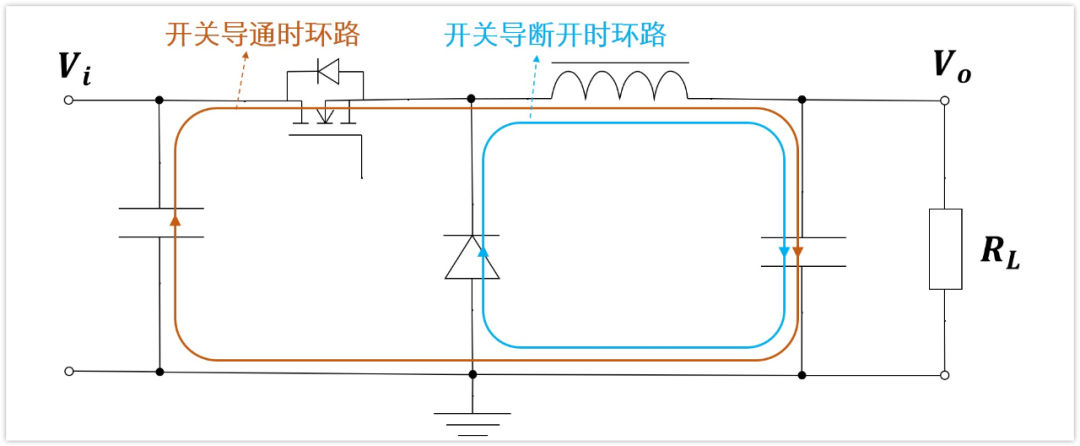

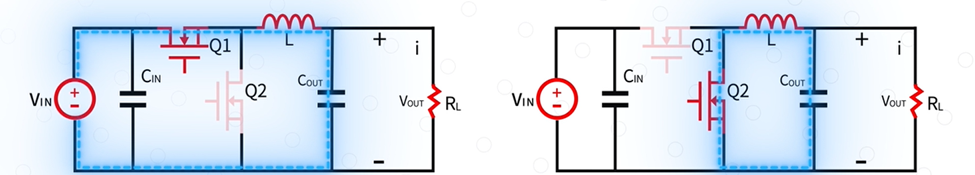

以BUCK為例,BUCK電路存在兩個狀態,上管導通和下管(或者是二極管)導通,因此存在兩個大的電流環路。

知道這兩個環路有什么用呢?

我們要讓這兩個環路的面積越小越好,因為每一個電流環都可以看成是一個環路天線,會產生輻射,會引起EMI問題,也會干擾板上其它的電路,而輻射的大小與環路面積呈正比。

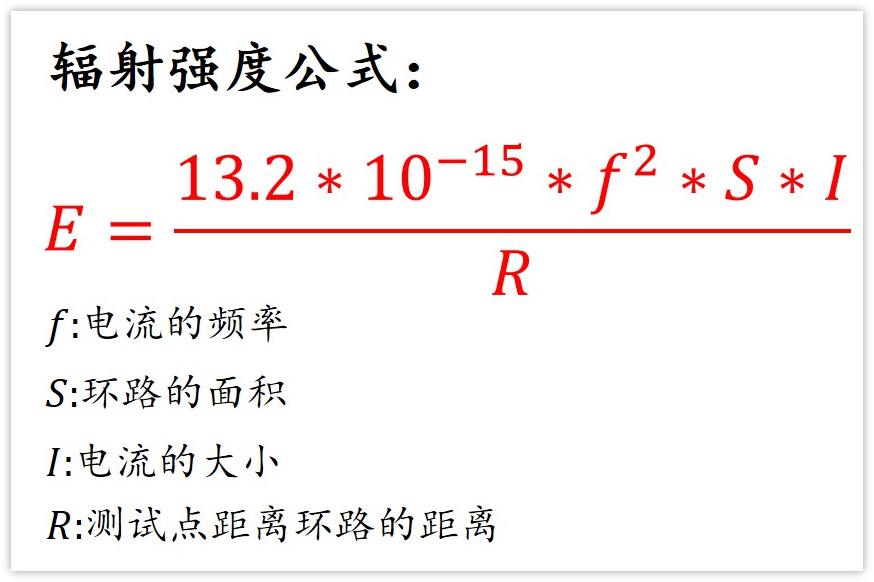

電流環所生成的高頻磁場會在離開環路大約 0.16λ 以后逐漸轉換為電磁場,由此形成的場強大約為:

可以看到,輻射的大小與環路的面積,頻率的平方,電流的大小呈正比。

那我們是不是讓這兩個環路面積最小就可以了呢?

確實是的,不過我認為了解這點還不夠,突出不了重點。

從拓撲圖可以看出,這兩個環路有公共的部分,一個環路包含另外一個環路,這導致那個大的環路的電流各個器件節點可能不一樣,所以不好用那個公式計算。

所以,我們需要變通下,怎么變通呢?

輻射產生的原因,就是因為電流產生了磁場,電流是變化的,所以磁場也是變化的。電流環圍繞的面積里面的磁通量會隨電流動態變化而變化,磁場生電場,電場生磁場形成了電磁波。

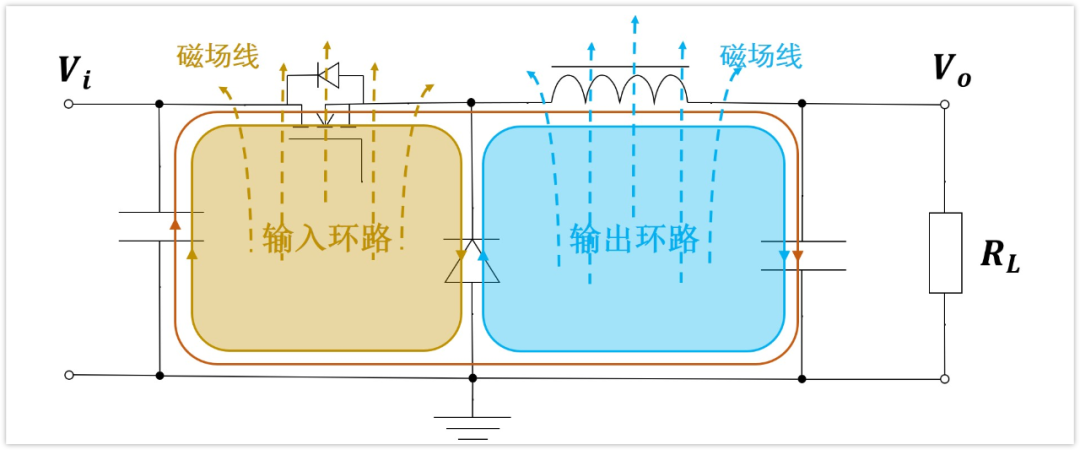

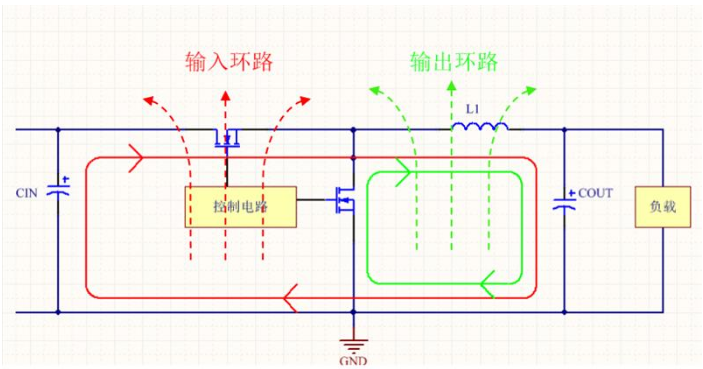

我們把那個大的電流環拆解為2個部分,如下圖:

整個大的環可以看成由輸入環路和輸出環路疊加。

可能有點難以理解,因為輸入環路根本就不是個實際的電流回路,它是本身存在的兩個電流環路的差值。

這其實只是個等效的方法而已,我們的目標是要知道總的大的回路里面的磁通量變化情況,這樣等效之后就可以求了,我們可以分別求得輸入環路和輸出環路的磁通量情況。

輸入環路的等效電流就是輸入電容Cin的電流

輸出環路的電路等效電流就是電感的電流

它們都是只看交流,直流分量不管,直流的頻率看成是0Hz,不會輻射電磁波。

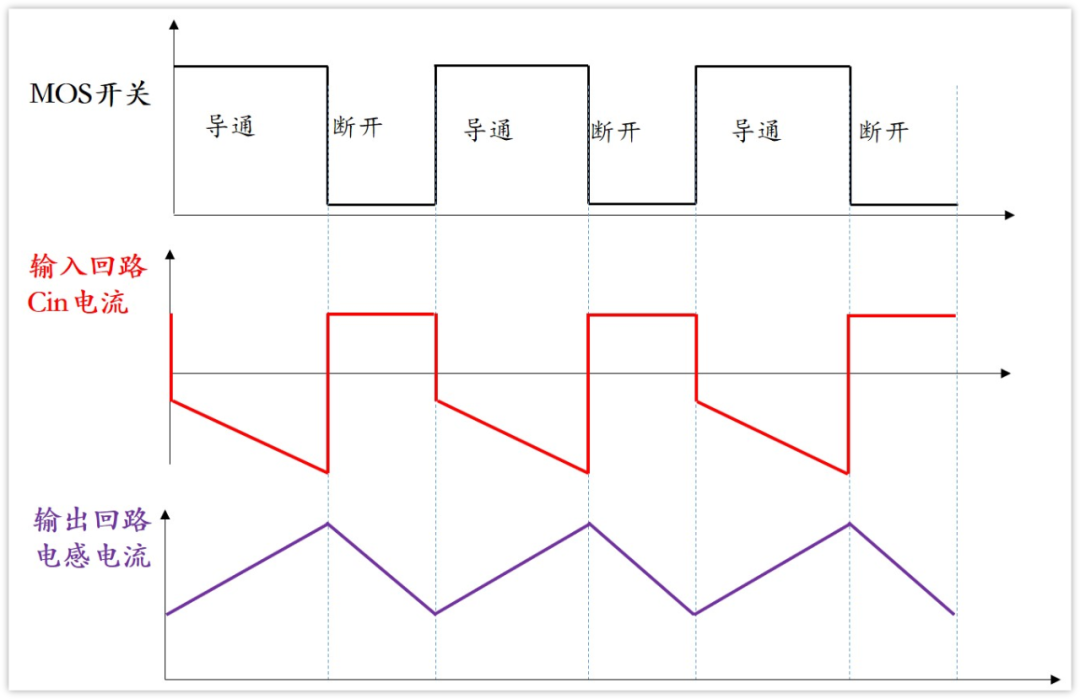

之前我們的《手撕Buck!Buck公式推導過程》已經分析了,輸入環路電流(Cin)和輸出環路電流(電感)分別如下:

可以看到,在開關切換的時候,輸入環路的電流是會突變的,也就是會有很大的di/dt,那么輸入環路的磁通量也是突變的(準確的說是變化速度很快),存在很多的高次諧波。

從前面的公式我們知道,輻射強度與頻率成正比,因此這些高次諧波更容易被輻射出去。

輸出環路的電流是三角波,是沒有突變的,所以高次諧波輻射強度要小些。

信號強度對比

這里可能有人會說了,三角波的頻譜理論不也是無限的嗎?也有很多高頻分量啊,怎么輻射就小一些。

確實,三角波的頻譜是無限的,不過頻率越高,幅度會越低的,也就是說高頻分量能量少,那么輻射也就少了。

關于這一點呢,我們簡單做個仿真,看下電流的傅里葉變換fft就知道了。

使用LTspice軟件仿真,5V轉1.8V的buck電路圖如下:

輸入環路電流(輸入電容電流)和輸出環路電流(電感電流波形)

有了波形,我們看下fft(仿真軟件很容易做到)

可以看到,基頻就是BUCK芯片LTC3307A的開關頻率2Mhz,2Mhz兩者的強度相差不是很大,就2-3個db左右,但是在10Mhz的時候,就已經相差20db了,頻率越高,差得越多。

也就是說,輸入環路的高頻諧波能量要比輸出環路大得多,如果有經驗的話,應該會知道,引起EMI超標的一般也就是高頻超標,所以因為輸入環路造成EMI的可能性更高。

我這里費了一些功夫,其實就是為了說明:

BUCK的輸入環路非常非常重要,環路面積一定一定要小。

另外一點需要注意,是環路面積小,不是走線短,這兩者還是有區別的。有時走線短并不一定環路就小,我們的目標是環路的面積,而不是長度。

我們布局走線盡量走成扁的那種形狀。

我們回到開頭的那個DCDC芯片,輸入環路指的什么呢?

顯然,這個芯片的開關管在芯片內部,所以輸入環路就是芯片的IN管腳,與GND管腳,以及輸入濾波電容形成的環路,那么除了芯片之外,器件就只有輸入濾波電容了。

所以最理想的layout就直接將輸入濾波電容跨接到芯片的IN腳和GND管腳,從這一點上看,芯片手冊推薦的layout與這一點是符合的,只是這樣做了之后,SW出不來而已。

這顆dcdc芯片給出的推薦layout確實是保證了輸入環路最小。只不過它將SW信號走在了輸入濾波電容下面,這個實際電路通常是行不通的,因為電容下面根本就走不了比較寬的線的。

那咋辦呢?

我估計會有人認為將輸入濾波電容放置到PCB的背面,在Vin和GND管腳正下方放置濾波電容,通過過孔接過去,這樣看起來環路也比較小。

我的看法是,如果有其它更好的方式,那就不要這么做。

因為過孔會存在寄生電感,加了過孔會增加這個環路的電感,導致發生LC振蕩。直接的現象就是在SW處產生高振鈴,這個高振鈴意味著這個環路中,諧振頻率的信號分量很強。

也就是說盡管環路面積不大,天線效應不強,但是我的信號強度變大了呀,輻射不一定差。

關于振鈴,以前專門寫過《BUCK的振鈴實驗與分析》,可以去看一看。

曾經的教訓

多年前,我曾經就遇到一個電源芯片的輸入濾波電容放背面,通過過孔連接,結果搞得整個板子的噪聲很大,而將濾波電容直接手動跨到Vin和GND上面,立馬問題就沒了。

當時我還不懂,覺得不可思議,打孔的數量并不少,濾波電容也是在底部就近放置的,居然還有問題,幾個孔威力這么大?

后來還專門改板解決,直接將輸入濾波電容與芯片同層,并在表層連接,問題就解決了。

上面說了這么多,其實主要說的就是,BUCK電路,輸入濾波電容的布局布線非常重要,是重中之重,是第一要考慮的。

如果是異步Buck,那么就有一個外置的二極管,這個二極管構成了輸入回路的一部分,那么它的位置,與輸入濾波電容的重要性是同級別的,要放得離芯片的SW比較近,具體怎么擺,咱們看回路面積怎么小就知道了。

輸出環路

前面寫了一堆,一直在強調輸入環路,那輸出環路不重要嗎?

當然不是,其實從前面的fft也能看到,輸出環路也有高頻分量,所以輸出環路也要越小越好,只是它相對輸入環路來說高頻分量強度不高,在二者布局有矛盾的時候,當然是優先考慮輸入環路。

我怎么畫

總而言之,如果是我,我會將開頭提到的BUCK這樣Layout:

Boost情況如何?

上面這是buck的一個情況,那么boost是怎么樣的呢?

輸入回路是最重要的嗎?優先需要考慮的是輸入濾波電容嗎?

答案是NO

Boost也有兩個環,是下圖這樣的

跟buck一樣,我們把它們分為兩個部分,輸入環路和輸出環路,可以看到,輸出環路是上面兩個環路的差值。

與buck不同的是,電感在輸入環路,其電流波形是三腳波,而輸出環路的電流就是二極管的電流,是有突變的。

之前《手撕Boost!Boost公式推導及實驗驗證》也已經全面分析了這兩個電流,波形如下:

也就是說,boost最重要的是輸出回路,類似于Buck的輸入回路。我們需要首先保障的是boost的輸出環路盡量小。

具體實例就不舉了。

Layout其它方面注意事項

除了大的電流回路,還有FB,補償電路這些,是小信號電路,所以他們要盡量遠離前面大的電流回路,遠離電感等。

比如下面,就是左邊比右邊的好:

另外需要注意,關于大的電流回路,我們要把GND地看進去,不要用這些走線分割了大電流的回流地GND路徑。

所以,你有的時候會看到,底層FB走線并不是最短的,而是繞了一下。

小結

總的來說,DCDC的layout,我們要做到心中要有電流環。

畫板的時候,心里念叨一下,開關斷開,電流咋咋咋流,開關導通,電流咋咋咋流。然后找到電流突變的那個環,那就是最重要的,得優先處理。

這個原則,其實不僅僅適用于dcdc,其它類型的電源,或者是大功率電路,都是如此的。

了解了這個原則,其實很多電路,都不用去細看芯片手冊的pcb layout的注意事項了,它說的也就是這些東西,只不過是具體的措施而已。

這種將關鍵環路做到最小,算是從根源上杜絕問題的產生,遠比后期想不改板,然后七搞八搞要強。

責任編輯:haq

-

電源

+關注

關注

184文章

17704瀏覽量

249965 -

芯片

+關注

關注

455文章

50715瀏覽量

423164 -

二極管

+關注

關注

147文章

9628瀏覽量

166311

原文標題:DCDC的Layout終極奧義

文章出處:【微信號:gh_3a15b8772f73,微信公眾號:硬件工程師煉成之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

pcb設計中布局的要點是什么

Buck電路中PCB layout布局設計和注意事項

PCB電路板設計與制作的步驟和要點

芯片中的存儲器有哪些

PCB Layout 的 9 個套路

PMP30784.1-2MHz 汽車類 SEPIC PCB layout 設計

PMP20587.1-反相降壓/升壓 PCB layout 設計

TIDA-010052-用于電機驅動的安全電源 PCB layout 設計

PMP31194.1-使用集成 FET 的汽車 SEPIC PCB layout 設計

PCB layout在布線上的設計規范有哪些?

5條DC-DC PCB layout建議

DCDC芯片中PCB Layout的設計要點

DCDC芯片中PCB Layout的設計要點

評論