《pg150-ultrascale-memory-ip》

以該手冊的脈絡(luò)為主線,對DDR3/4控制器進行探討。

1.IP核結(jié)構(gòu)

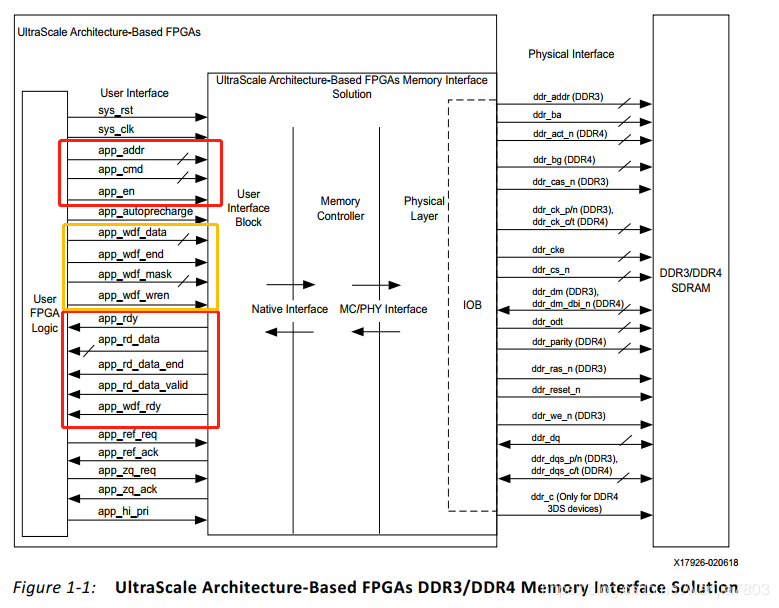

根據(jù)官方提供的資料,IP核主要劃分為三個部分,分別是用戶接口,內(nèi)存控制器以及物理層接口。對于用戶來說,我們需要研究清楚的是用戶接口部分內(nèi)容,其余兩部分只需了解即可,這里就不展開論述。

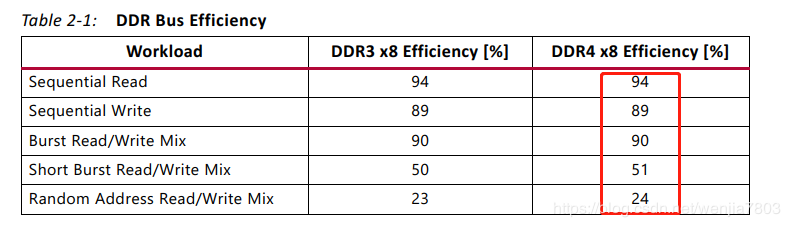

讀寫效率

X8是表示,該內(nèi)存顆粒的數(shù)據(jù)總線為8bit。常見的還有x4/x16。

整個DDR的IP核應(yīng)用,主要都是圍繞這以下幾個路徑進行,開發(fā)者直接打交道的是IP_core的userinterface。其他物理底層的內(nèi)容,由IP自行完成。主要指令路徑包括:Command Path、write_Path、read_Path以及維護指令(Maintenance Commands)。

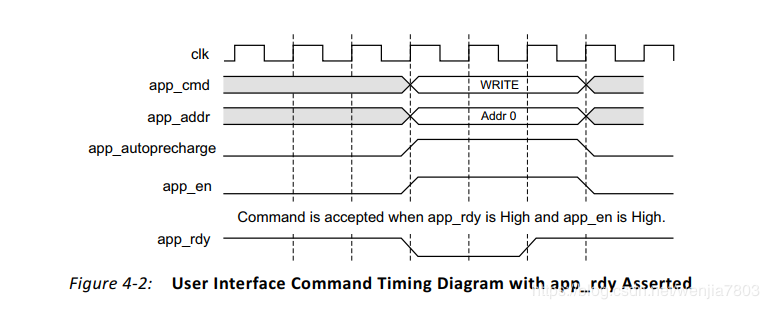

Command Path

顧名思義,就是讀寫操作指令寫入的路徑。當(dāng)app_rdy與app_en都有效的時候,新的指令才能寫入命令FIFO里,并被執(zhí)行。

Write Path

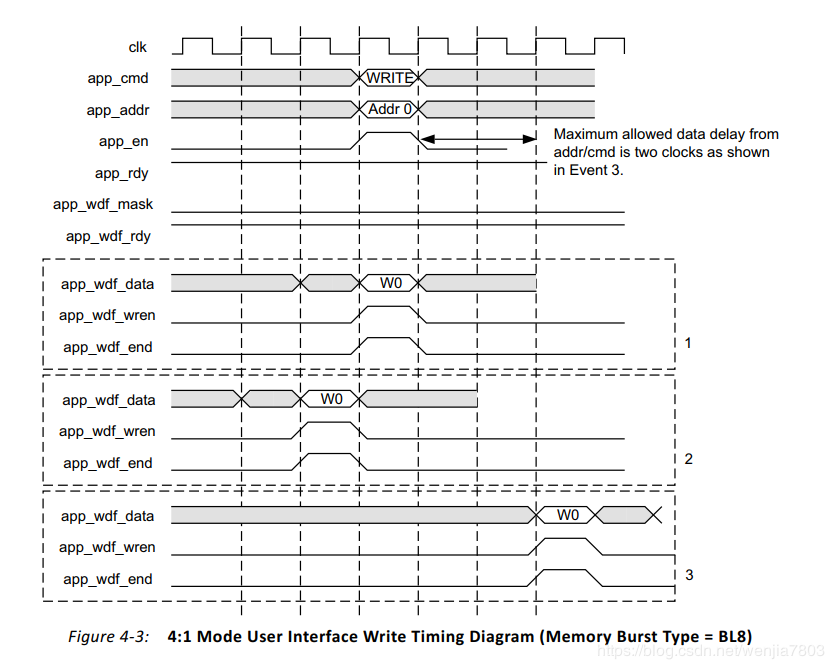

數(shù)據(jù)內(nèi)容寫入IP核的路徑。

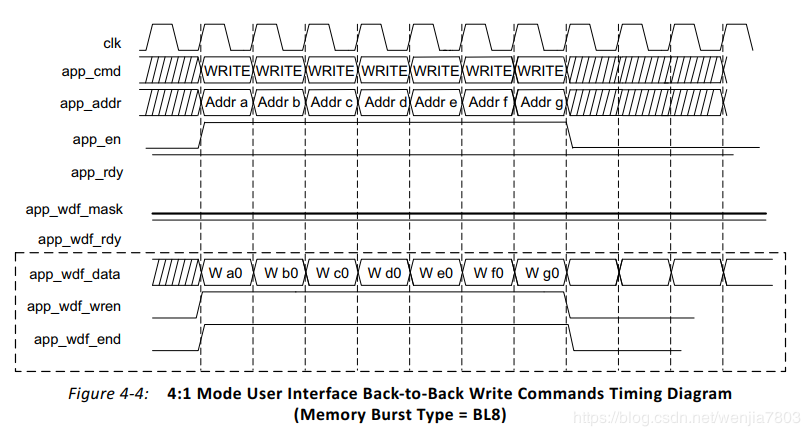

從上述的時序圖看來,與寫入路徑相關(guān)的信號有app_adf_data、app_wdf_wren以及app_wdf_end。雖然說,寫入的數(shù)據(jù)路徑與指令路徑可以不對齊,但實際應(yīng)用過程中,建議還是對齊操作,要不然容易出問題(后續(xù)調(diào)試測試的內(nèi)容有提到)。

pp_wdf_end為高,表示該數(shù)據(jù)這次寫入請求的最后一個數(shù)。以上圖為例,4:1mode是指用戶接口時鐘與物理層驅(qū)動DDR的時鐘之比為1:4。比如用戶接口的數(shù)據(jù)總線為64bit,物理層驅(qū)動DDR芯片位寬為8bit ,BL=8, 在4:1mode下,那么正好一個用戶clk可以執(zhí)行完一次突發(fā)傳輸(DDR是在時鐘上升沿和下降沿都傳輸數(shù)據(jù))。所以在執(zhí)行傳輸?shù)倪^程中,app_wdf_end為高。

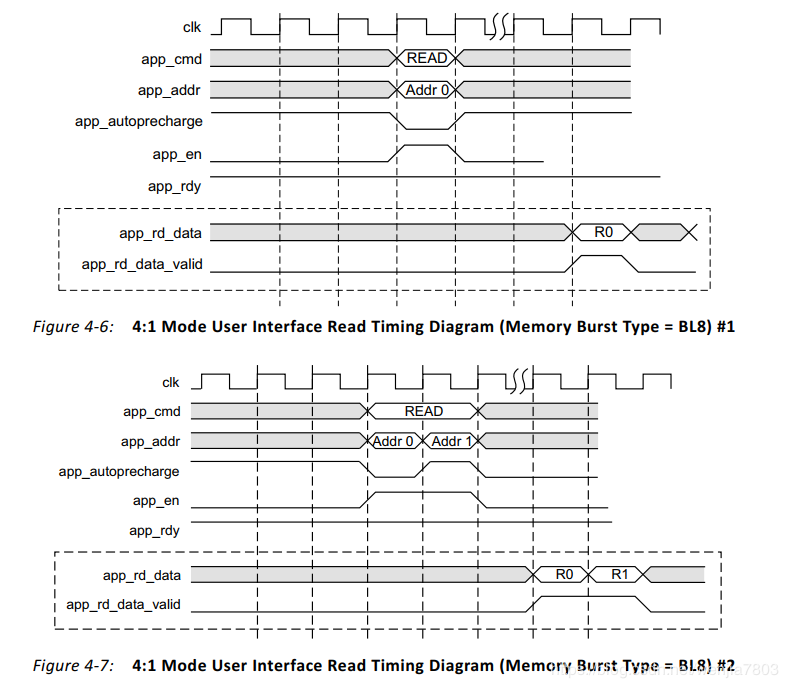

Read Path

數(shù)據(jù)從IP核中讀出來的路徑。

Maintenance Commands(維護指令)

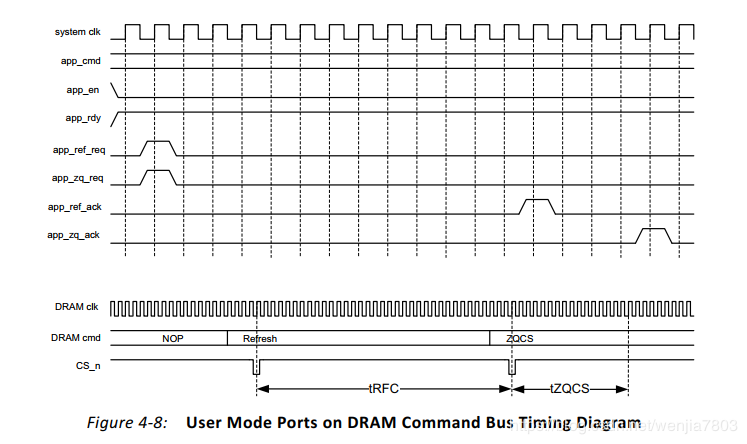

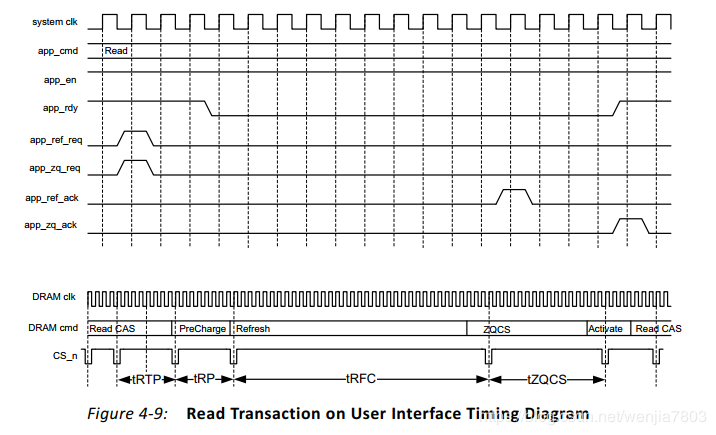

這里可以解析為什么讀寫效率不能夠達到百分百,由于ddr需要刷新等導(dǎo)致。其中啟動刷新有兩種模式,一種是自動刷新,即IP核自己產(chǎn)生滿足時序的刷新請求,另外一種是通過選中“啟用用戶刷新和ZQCS輸入”選項來啟用用戶模式。在此模式下,當(dāng)init_calib_complete有效之后,由用戶負責(zé)發(fā)出Refresh和ZQCS命令以滿足DRAM組件規(guī)范所要求的速率。ZQCS是用于ZQ 校準,這個與ODT相關(guān)。

擴展一下:

ODT(On-Die Termination),是從DDR2 SDRAM時代開始新增的功能。其允許用戶通過讀寫MR1寄存器,來控制DDR3 SDRAM中內(nèi)部的終端電阻的連接或者斷開。

為什么要用ODT?一個DDR通道,通常會掛接多個Rank,這些Rank的數(shù)據(jù)線、地址線等等都是共用;數(shù)據(jù)信號也就依次傳遞到每個Rank,到達線路末端的時候,波形會有反射,從而影響到原始信號;因此需要加上終端電阻,吸收余波。之前的DDR,終端電阻做在板子上,但是因為種種原因,效果不是太好,到了DDR2,把終端電阻做到了DDR顆粒內(nèi)部,也就稱為On Die Termination,Die上的終端電阻,Die是硅片的意思,這里也就是DDR顆粒。

所以,使用ODT的目的很簡單,是為了讓DQS、RDQS、DQ和DM信號在終結(jié)電阻處消耗完,防止這些信號在電路上形成反射,進而增強信號完整性。

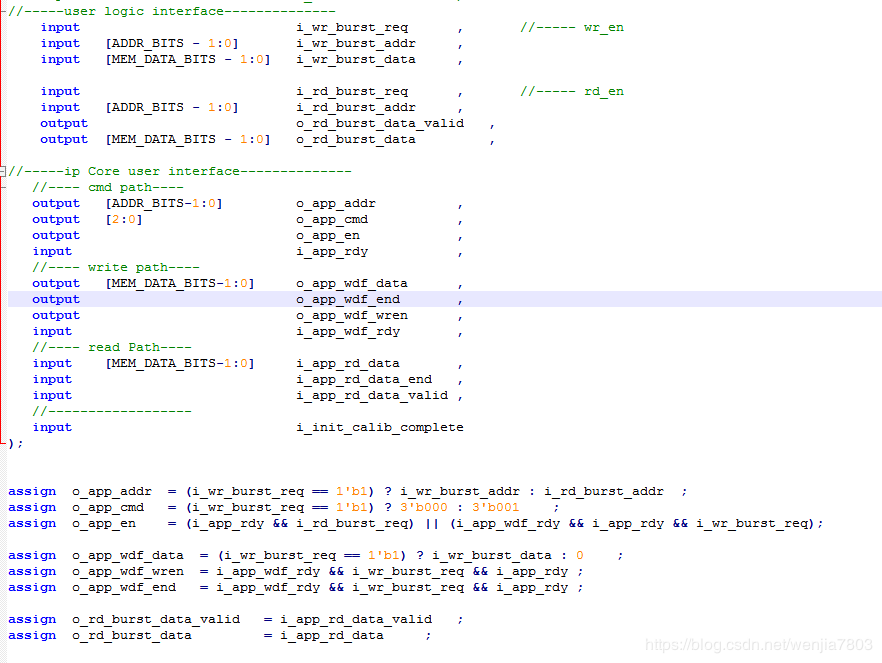

3.對IP核進行二次封裝

建議對IP核的User_interface再封裝一層,對外只需預(yù)留例如wr_en/wr_data以及rd_en/rd_data等信號,類似于讀寫FIFO的端口,提高模塊的后期復(fù)用。

4.調(diào)試與測試記錄

手冊梳理得差不多了,寫個簡單的程序仿真測試。期間碰到了些問題,分享出來記錄一下。

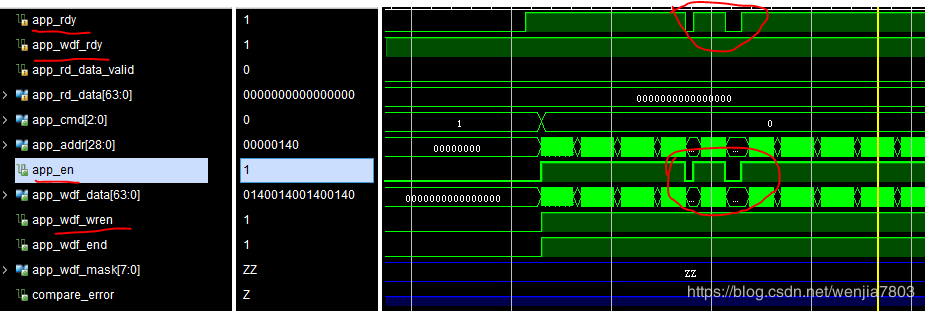

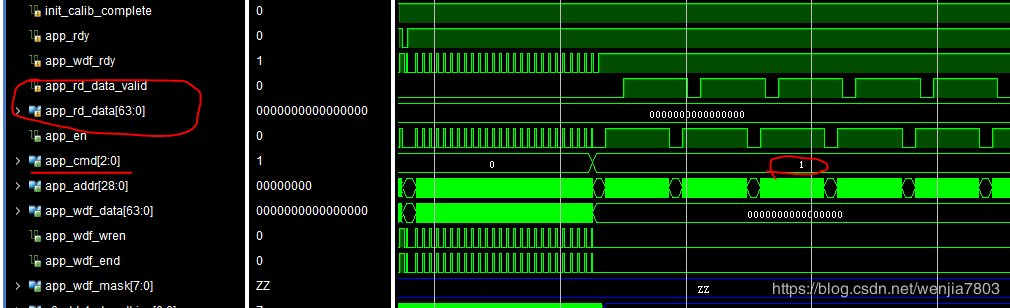

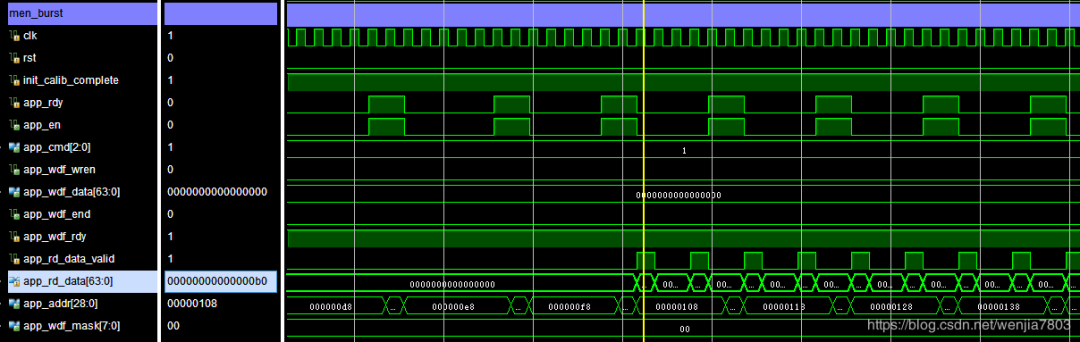

cmd_path與write_path沒對齊。

圖中所示,app_rdy為低,但是wdf_wren仍然為高,短期的話應(yīng)該沒有什么問題,但是如果持續(xù)一段時間,必然會導(dǎo)致IP核中fifo被寫滿,導(dǎo)致異常。

解決辦法:

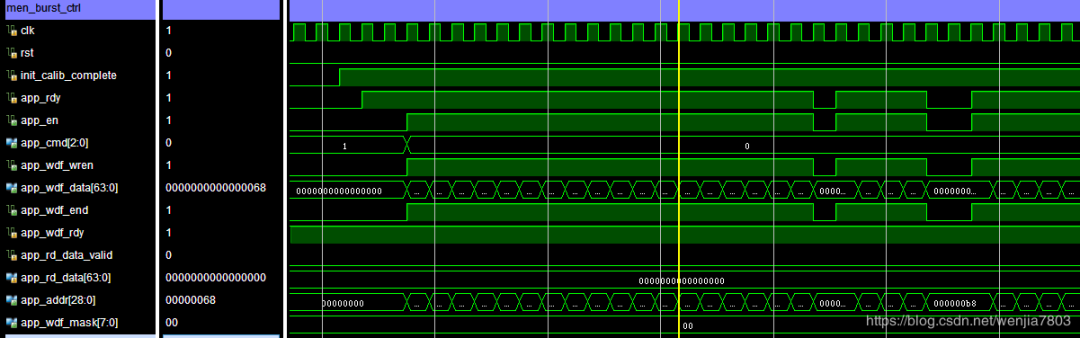

令指令與數(shù)據(jù)路徑命令對齊。在寫入的時候,當(dāng)app_rdy與app_wdf_rdy都有效的時候,才觸發(fā)相應(yīng)的動作。

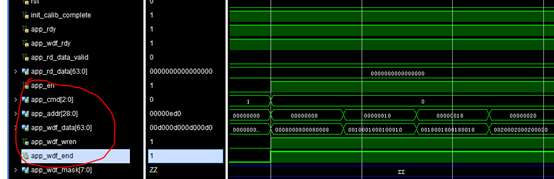

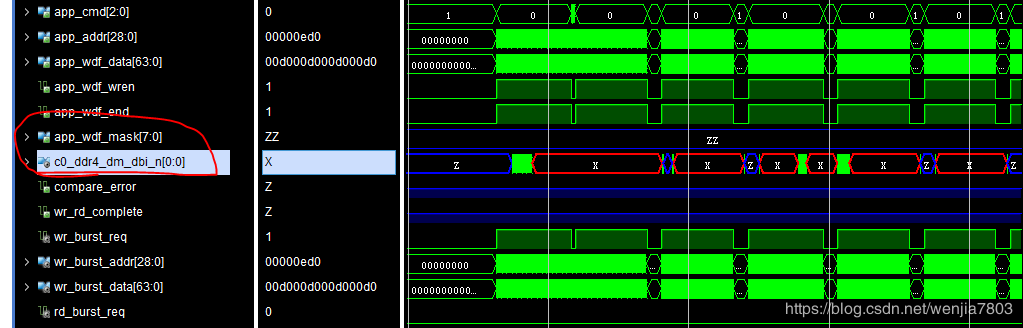

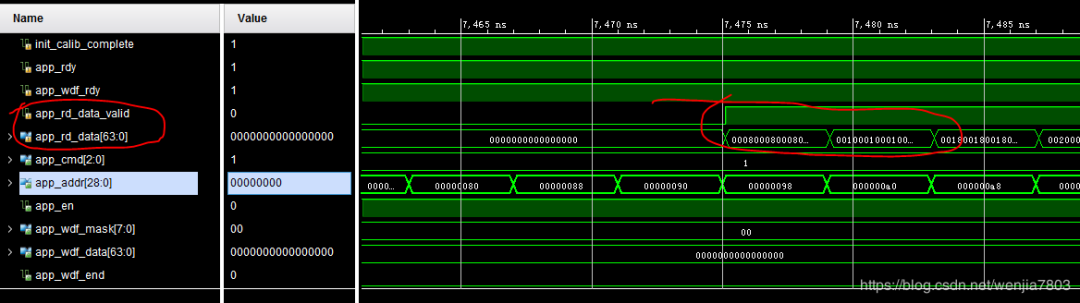

數(shù)據(jù)沒有寫入,導(dǎo)致回讀出來的數(shù)據(jù)不對。

從時序上來看,寫入沒有問題。但是我當(dāng)初忽略了app_wdf_mask,這個沒有賦值(正常應(yīng)該賦0),導(dǎo)致仿真的時候,該信號一致顯示高阻態(tài)。然后發(fā)現(xiàn)ddr4_dm_dbi_n(雙向信號)信號異常。

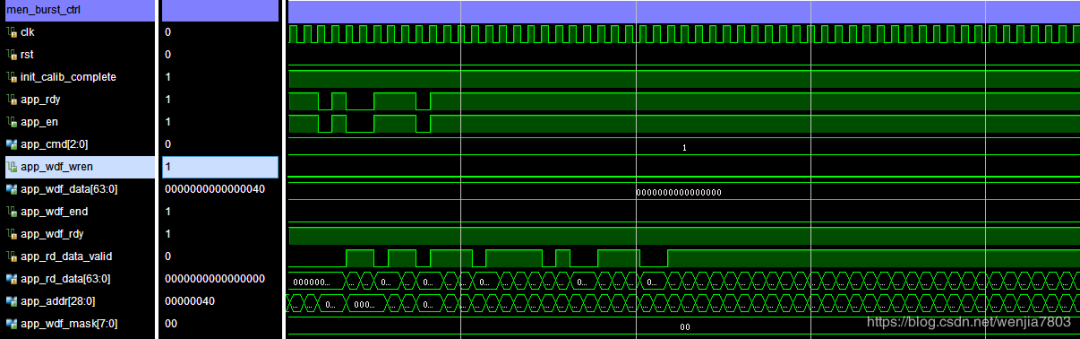

讀出來的數(shù)據(jù)一直是0.

修改過來后,問題解決。

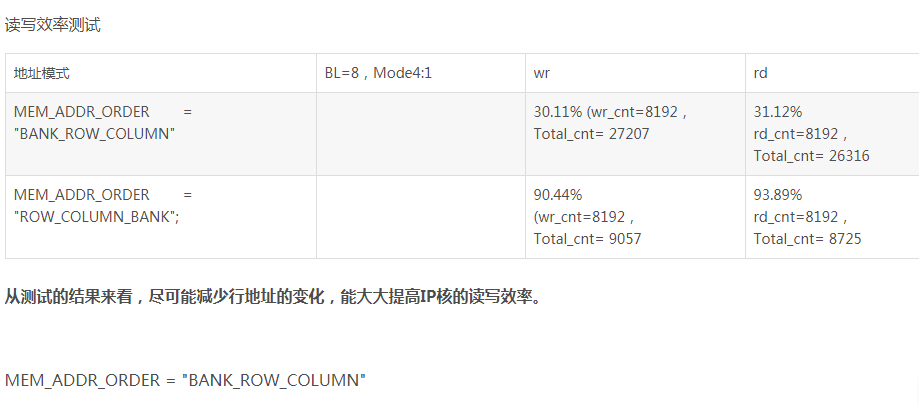

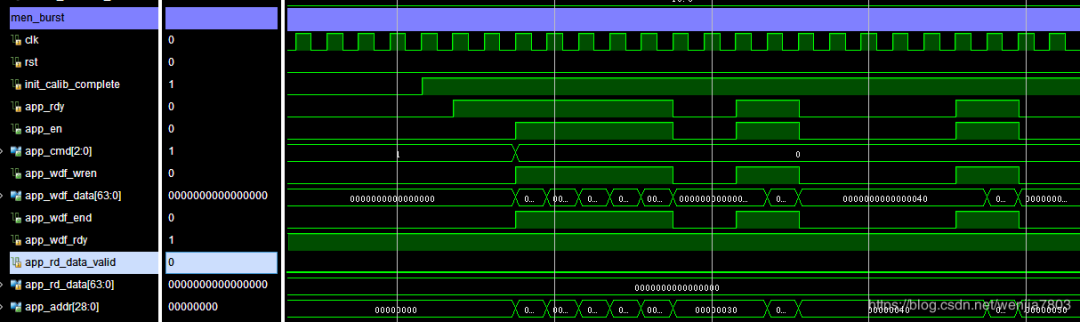

讀寫效率測試

Wr:

Rd:

MEM_ADDR_ORDER = "ROW_COLUMN_BANK";

Wr:

Rd:

仔細的話,可以觀察clk與app_rdy之間的關(guān)系,不難發(fā)現(xiàn)為什么兩者的讀寫效率會相差這么大。不同的地址排列,在每次讀寫過程中,IP的效率有很大的關(guān)系,這個與DDR的實現(xiàn)機制有關(guān)。詳細情況在PG150里有相關(guān)說明。

編輯:jq

-

控制器

+關(guān)注

關(guān)注

112文章

16347瀏覽量

177906 -

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42256

原文標題:DDR3/4_IP核應(yīng)用--vivado

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

DDR3、DDR4、DDR5的性能對比

如何選擇DDR內(nèi)存條 DDR3與DDR4內(nèi)存區(qū)別

DDR4 SDRAM控制器的主要特點

DDR4的主要參數(shù)

DDR3寄存器和PLL數(shù)據(jù)表

基于FPGA的DDR3多端口讀寫存儲管理設(shè)計

華邦傾力挺進DDR3市場,抓住轉(zhuǎn)單商機

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)表

完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數(shù)據(jù)表

具有同步降壓控制器、2A LDO和緩沖基準的完整DDR2、DDR3和DDR3L存儲器電源解決方案TPS51216-EP數(shù)據(jù)表

完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表

適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩(wěn)壓器數(shù)據(jù)表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數(shù)據(jù)表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內(nèi)存電源解決方案數(shù)據(jù)表

完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表

對DDR3/4控制器進行探討

對DDR3/4控制器進行探討

評論