當今的設計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現嵌入式設計。在嵌入式系統中,通常是由相對數量較少的算法決定最大的運算需求。使用設計自動化工具可以將這些算法快速轉換到硬件協處理器中。然后,協處理器可以有效地連接到處理器,產生“GHz”級的性能。

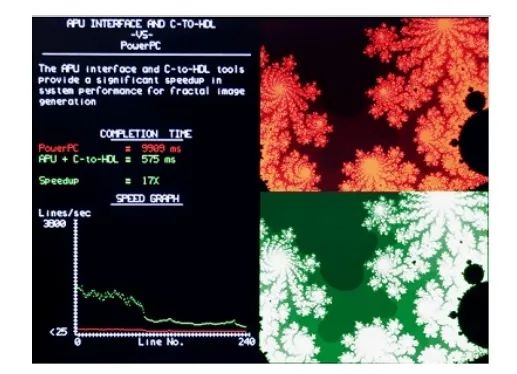

本文主要研究了代碼加速和代碼轉換到硬件協處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準數據均衡決策的過程。該設計使用了在一個平臺FPGA中實現的一個嵌入式PowerPC。

協處理器的意義

協處理器是一個處理單元,該處理單元與一個主處理單元一起使用來承擔通常由主處理單元執行的運算。通常,協處理器功能在硬件中實現以替代幾種軟件指令。通過減少多種代碼指令為單一指令,以及在硬件中直接實現指令的方式,從而實現代碼加速。

最常用的協處理器是浮點單元(FPU),這是與CPU緊密結合的唯一普通協處理器。沒有通用的協處理器庫,即使是存在這樣的庫,將依然難以簡單地將協處理器與一個CPU(例如Pentium 4)連接。Xilinx Virtex-4 FX FPGA擁有一個或兩個PowerPC,每個都有一個APU接口。通過在FPGA中嵌入一個處理器,現在就有機會在單芯片上實現完整的處理系統。

帶APU接口的PowerPC使得在FPGA中得以實現一個緊密結合的協處理器。因為頻率的需求以及管腳數量的限制,采用外部協處理器不大可行。因此可以創建一個直接連接到PowerPC的專用應用協處理器,大大地提高了軟件速度。因為FPGA是可編程的,你可以快速地開發和測試連接到CPU的協處理器解決方案。

協處理器連接模型

協處理器有三種基本的形式:與CPU總線連接的、與I/O連接的和指令流水線連接(Instruction Pipeline Connection)。此外,還存在一些這些形式的混合形式。

1. CPU總線連接

處理器總線連接加速器需要CPU在總線上移動數據以及發送命令。通常,單個數據處理就需要很多的處理器時鐘周期。因為總線仲裁以及總線驅動的時鐘是處理器時鐘的分頻,所以會降低數據處理速度。一個與總線連接的加速器可以包含一個存儲器存取(DMA)引擎。在增加額外的邏輯情況下,DMA引擎允許協處理器工作在位于連接到總線的存儲器上的數據塊,獨立于CPU。

2. I/O連接

與I/O連接的加速器直接連接到一個專用的I/O端口。通常通過GET或PUT函數提供數據和控制。因為缺少了仲裁、控制復雜度降低以及連接器件較少,因此這些接口的驅動時鐘通常比處理器總線更快。這種接口的一個較好的例子如Xilinx Fast Simplex Link(FSL)。FSL是一種簡單的FIFO接口,可以連接到Xilinx MicroBlaze軟核處理器或Virtex-4 FX PowerPC。與處理器總線接口中的數據移動相比,通過FSL移動的數據具有較低的延時和更高的數據速率。

3. 指令流水線連接

指令流水線連接加速器直接連接到CPU的計算內核。通過與指令流水線連接,CPU不能識別的指令可以由協處理器執行。操作數、結果以及狀態直接從數據執行流水線向外傳遞,或接收。單個運算可以實現兩個操作數的處理,同時返回一個結果和狀態。

作為一個直接連接的接口,連接道指令流水線的加速器可以用比處理器總線更快的時鐘驅動。Xilinx通過APU接口實現這種協處理器連接模型,對于典型的雙操作數指令,在數據控制和數據傳輸上可以縮減10倍的時鐘周期。APU控制器還連接到數據緩存控制器,通過它可以執行數據加載/存儲操作。因此,APU接口能在每秒內移動數百兆字節,接近DMA速度。

I/O連接加速器或指令流水線連接加速器可以與總線連接加速器結合起來。在增加額外的邏輯條件下,可以創建一個加速器,這個加速器運行在一個位于總線連接存儲器上的數據塊上,通過一個快速、低延時的接口接收命令并返回狀態。

在本文中介紹的C-HDL工具組可以實現總線連接和I/O連接加速器,它還能實現連接到PowerPC的APU接口的加速器。盡管APU連接是基于指令流水線的,C-HDL工具組實現了一種I/O流水線接口,該接口具有I/O連接加速器的典型性能。

FPGA/PowerPC/APU接口

FPGA允許硬件設計工程師利用單芯片上的處理器、解碼邏輯、外設和協處理器實現一個完整的計算系統。FPGA可以包含數千到數十萬的邏輯單元,可以從這些邏輯單元實現一個處理器,如Xilinx PicoBlaze或MicroBlaze處理器,或者可以是一個或者更多的硬邏輯單元(如Virtex-4 FX PowerPC)。大量的邏輯單元使你可以實現數據處理單元,這些單元與處理器系統一起工作,由處理器對其進行控制或監控。

FPGA作為一種可重復編程的單元,允許你在設計過程中進行編程并對其進行測試。如果你發現了一個設計缺陷,你可以立即對其進行重新編程設計。FPGA還允許你實現硬件運算功能,而這在以前的實現成本是很高的。CPU流水線與FPGA邏輯之間緊密結合,這樣就可以創建高性能軟件加速器。

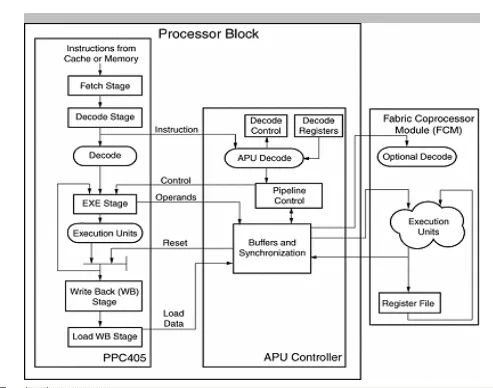

圖1的模塊框圖顯示了PowerPC、集成的APU控制器以及一個與之相連的協處理器。來自高速緩存或存儲器中的指令可以立即出現在CPU解碼器和APU控制器上,如果CPU能識別指令,則運行這些指令。

否則,APU控制器或用戶創建的協處理器可以對指令做出應答并執行指令。一個或者兩個操作數被傳遞到協處理器,并返回一個結果或狀態。APU接口還支持用一個指令發送一個數據單元。數據單元的大小范圍從一個字節到4個32位的字。

圖1:PowerPC、集成的APU控制器和協處理器

通過一個結構協處理器總線(FCB),可以將一個或多個協處理器連接到APU接口。連接到總線的協處理器范圍包括現存的內核(例如FPU)到用戶創建的協處理器。一個協處理器可以連接到FCB用于控制和狀態運算,并連接到一個處理器總線,實現直接存儲器數據塊訪問以及DMA數據傳遞。一種簡化的連接方案,例如FSL,也可以在FCB和協處理器之間使用,在犧牲一定性能的條件下實現FIFO數據和控制通信。

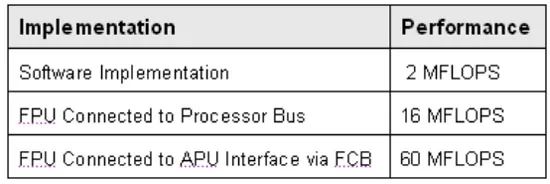

為展示指令流水線連接加速器的性能優勢,我們采用一個處理器總線連接FPU首先實現了一個設計,然后采用APU/FCB連接的FPU實現設計。表1總結了兩種實現方式下有限脈沖響應(FIR)濾波器的性能。如表1中所反映的一樣,連接到一個指令流水線的FPU使軟件浮點運算速度增加30倍,而APU接口相比于總線連接FPU來說改善了近4倍。

表1:未加速與加速的浮點性能

C代碼轉換到HDL

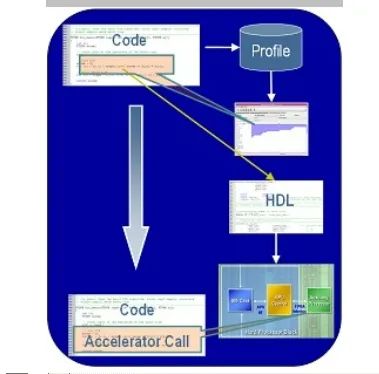

采用C到HDL的轉換工具將C代碼轉換到HDL加速器是一種創建硬件協處理器的高效方法。圖2所示以及下面詳述的步驟總結了C到HDL轉換的過程:

圖2:C-HDL設計流程

使用標準C工具實現應用程序或算法。開發一種軟件測試向量(test bench)用于基線性能和正確性(主機或臺式電腦仿真)測試。使用一種編譯器(例如gprof)來開始確定關鍵的函數。

確定是否浮點到定點轉換適當。使用庫或宏來輔助這種轉換,使用一個基線測試向量來分析性能和準確性。使用編譯器來重新評估關鍵函數。

使用C到HDL轉換工具(如Impulse C),在每個關鍵功能上重復,以實現:將算法分割成并行的進程;創建硬件/軟件進程接口(流、共享存儲器、信號);對關鍵的代碼段(例如內部代碼循環)進行自動優化和并行化;使用桌面電腦仿真、周期準確的C仿真以及實際的在系統測試對得到的并行算法進行測試和驗證。

使用C到HDL轉換工具將關鍵的代碼段轉換到HDL協處理器。

將協處理器連接到APU接口用于最終的測試。

Impulse:C到HDL轉換工具

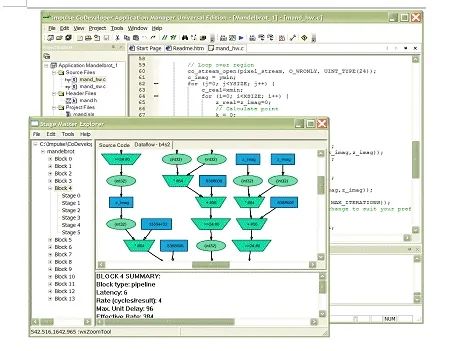

如圖3所示的Impulse C通過結合使用C兼容庫函數與Impulse CoDeveloper C代碼到硬件的編譯器,使嵌入式系統設計工程師能創建高度并行的、FPGA加速的應用。Impulse C通過使用定義完好的數據通信、消息傳遞和同步處理機制,簡化了硬件/軟件混合應用設計。Impulse C提供了C代碼(例如循環流水線處理、展開和運算符調度)的自動優化以及交互式工具,允許你對每個周期的硬件行為進行分析。

圖3. Impulse C

Impulse C設計用于面向數據流的應用,但是它也具有足夠的靈活性來支持其他的編程模型,包括使用共享存儲器。這一點很重要,因為基于FPGA不同的應用具有不同的性能和數據要求。在一些應用中,通過塊存儲器讀和寫在嵌入式處理器和FPGA之間轉移數據是有意義的;在其它的情況下,流傳數通信信道可能提供更高的性能。可以快速建模、編譯和評估可選的算法的能力對于實現某個應用最佳的結果來說,非常重要。

到目前為止,Impulse C庫包含以新數據類型和預定義的函數調用形式的最少C語言擴展。使用Impulse C函數調用,你可以定義多個并行程序段(調用進程),并使用流、信號和其他機制描述它們的互連。Impulse C編譯器將這些C語言進程轉換并優化成:可以綜合到FPGA的較低級HDL,或可以通過廣泛存在的C交叉編譯器編譯到支持的微處理器上標準C(帶相關的庫調用)。

完整的CoDeveloper開發環境包括與標準C編譯器和調試器(包括微軟公司的Visual Studio和GCC/GDB)兼容的臺式電腦仿真庫。使用這些庫,Impulse C程序設計工程師能編譯和執行他們用于算法驗證和調試目的的應用程序。C程序設計工程師還能檢驗并行進程,分析數據移動,并利用CoDeveloper Application Monitor解決進程到進程的通信問題。

在編譯時,Impulse C應用的輸出是一組硬件和軟件源文件,用于輸入到FPGA綜合工具。這些文件包括:

用于描述編譯硬件進程的自動產生的HDL文件;

用于描述連接硬件進程到系統總線所需的流、信號和存儲器組件的自動產生的HDL文件;

自動產生的軟件組件(包括運行時間庫)用于建立任何硬件/軟件流連接的軟件端;

附加文件,包括腳本文件,用于輸入產生的應用程序到目標FPGA布局布線環境。這種編譯進程的結果是一個完整的應用,包括需要的硬件/軟件接口,用于在基于FPGA的編程平臺上實現。

設計實例

圖4所示的Mandelbrot圖是一種經典的不規則幾何圖形,該圖形廣泛用在科學和工程學界用于仿真無序事件,例如天氣。不規則圖形也用于產生紋理和在視頻顯示應用上成像。Mandelbrot圖像描述為自相似性。放大圖形的局部,可以獲得類似于整個圖形的另外一個圖形。

Mandelbrot圖形是硬件/軟件協同設計的理想選擇,因為它具有單個運算密集的函數。通過將關鍵的函數轉移到硬件實現將大大地增加整個系統的速度,使這個關鍵函數更快。Mandelbrot應用還能清楚地區分硬件和軟件進程,使用C-HDL工具很容易實現。

本文使用CoDeveloper工具組作為C-HDL工具組用于該設計實例,而且只修改了軟件Mandelbrot C程序以使其與C-HDL工具兼容。其中的改變包括:將軟件項目分割成不同的進程(順序執行的獨立單元);函數接口轉換(硬件到軟件)到流;增加編譯器指令來對產生的硬件進行優化。我們隨后使用CoDeveloper工具組來創建Pcore協處理器,將該協處理器輸入到Xilinx Platform Studio(XPS

)。利用XPS,我們將PC連接到PowerPC APU控制器接口,并測試系統。

Xilinx公司的應用說明資料XAPP901中提供了該設計的全面描述和設計文件,并提供下載。同時,用戶指南UG096提供一種實現設計實例的逐步設計指導。

我們對Mandelbrot圖像紋理問題、圖像濾波應用和三倍DES加密的性能改善進行了測量。

本文小結

受功率、尺寸和成本的約束,你可能需要做出一個并非理想的處理器選擇,通常所選擇處理器性能比期望的性能低。當軟件代碼不能運行足夠快時,協處理器代碼加速器成為一種很有吸引力的解決方案。你可以在HDL中手動設計加速器或使用C-HDL工具自動將C代碼轉換成HDL。

使用Impulse C這樣的C-HDL工具能使加速器運行更快且更簡單。Virtex-4 FX FPGA具有兩個嵌入式PowerPC,能實現處理器指令流水線到軟件加速器之間緊密的連接。如上所述,關鍵的軟件程序增加速度10倍到30倍,使300MHz的PowerPC提供等于或高于高性能GHz級處理器的性能。上面的實例每個只需要幾天的時間來產生,顯示了采用C-HDL流程的快速設計、實現和測試

編輯:jq

-

FPGA

+關注

關注

1645文章

22034瀏覽量

617938 -

cpu

+關注

關注

68文章

11074瀏覽量

216906 -

數據

+關注

關注

8文章

7254瀏覽量

91788 -

fifo

+關注

關注

3文章

400瀏覽量

44784 -

APU

+關注

關注

0文章

143瀏覽量

24097

原文標題:如何采用FPGA協處理器實現算法加速

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

請問NICE協處理器與傳統ocb外設相比的優勢有什么?

NICE協處理器與傳統ocb外設相比的優勢有什么?

Cadence推出Tensilica NeuroEdge 130 AI協處理器

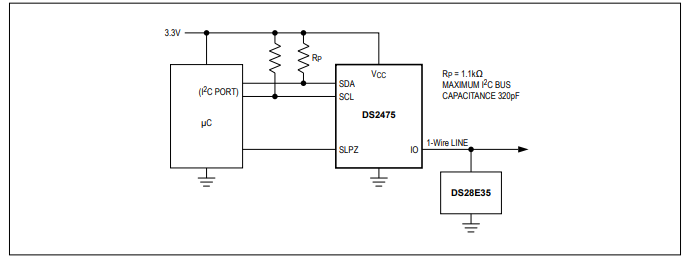

DS2475帶1-Wire主機的DeepCover ECDSA協處理器技術手冊

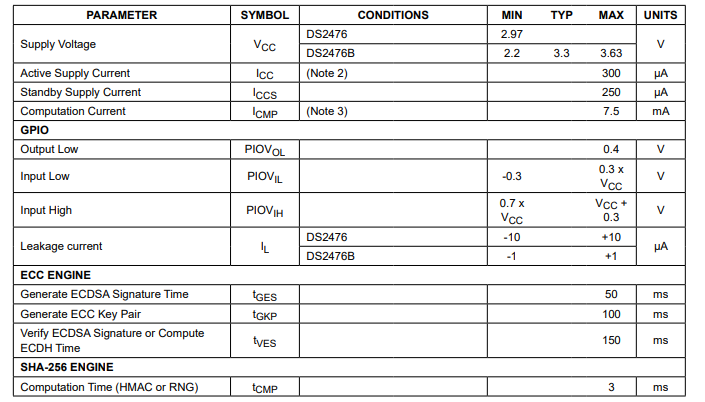

DS2476 DeepCover安全協處理器技術手冊

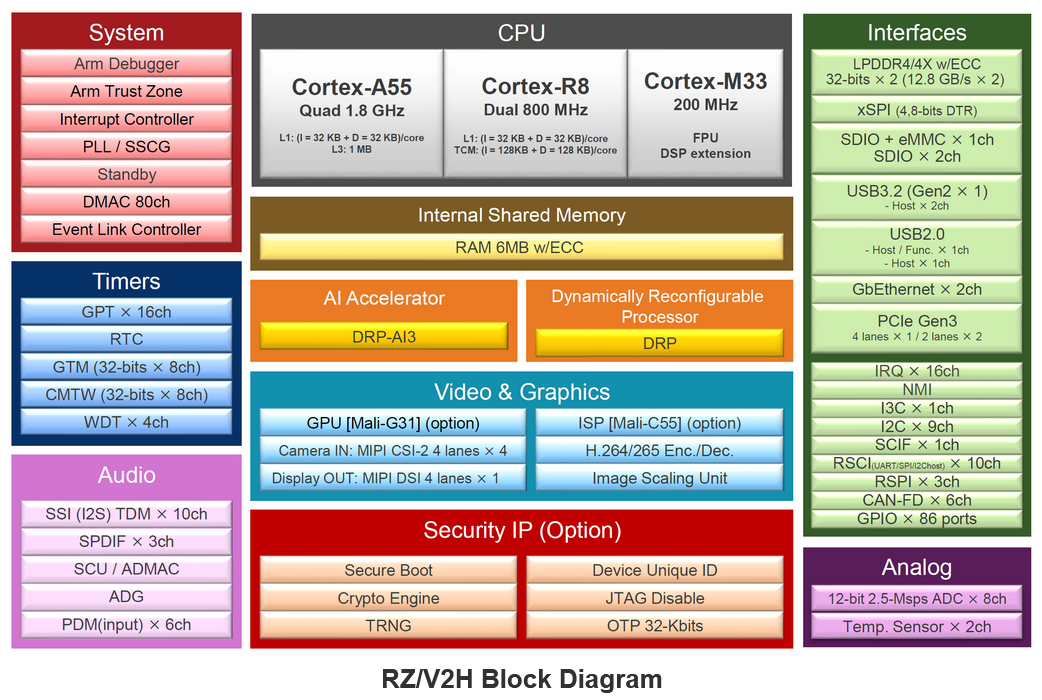

AI MPU# 瑞薩RZ/V2H 四核視覺 ,采用 DRP-AI3 加速器和高性能實時處理器

FPGA加速深度學習模型的案例

使用TMS320C6416協處理器:Turbo協處理器(TCP)

使用TMS320C6416協處理器:Viterbi協處理器(VCP)

盛顯科技:投影融合處理器如何實現圖像的處理和融合?

實現下一代具有電壓電平轉換功能的處理器、FPGA 和ASSP

評論