嵌入式FPGA (eFPGA)由于可為人工智能(AI)工作負(fù)載提供支持與靈活度,這項(xiàng)業(yè)務(wù)正開始掀起波瀾。如今,在將FPGA功能整合至SoC設(shè)計(jì)時(shí),eFPGA讓設(shè)計(jì)人員能夠定義FPGA邏輯的數(shù)量、內(nèi)存以及DSP的處理能力。

根據(jù)來(lái)自業(yè)界的兩項(xiàng)最新消息顯示,eFPGA能夠添加新的產(chǎn)品功能,并針對(duì)特定的子市場(chǎng)或相鄰市場(chǎng)量身打造SoC,這使其成為離散式FPGA的可行替代品。首先,QuickLogic宣布贏得了一份價(jià)值200萬(wàn)美元的合約,將為一家不具名的客戶提供eFPGA IP。

幾乎就在同一天,即 2021年9月1日,eFPGA IP供貨商Achronix Semiconductor宣布與Signoff Semiconductors建立合作伙伴關(guān)系。Signoff Semiconductors 是一家位于印度班加羅爾的FPGA和ASIC設(shè)計(jì)服務(wù)供貨商,可提供從規(guī)格、設(shè)計(jì)、驗(yàn)證、試產(chǎn)到量產(chǎn)(Spec. to Silicon)的FPGA和ASIC完整解決方案。因此,Signoff未來(lái)將可以直接使用Achronix的芯片、IP和支持服務(wù)。該設(shè)計(jì)服務(wù)公司并計(jì)劃使用Achronix的FPGA和eFPGA IP技術(shù),開發(fā)AI和深度學(xué)習(xí)加速器、推論解決方案以及邊緣物聯(lián)網(wǎng)(IoT)處理器。

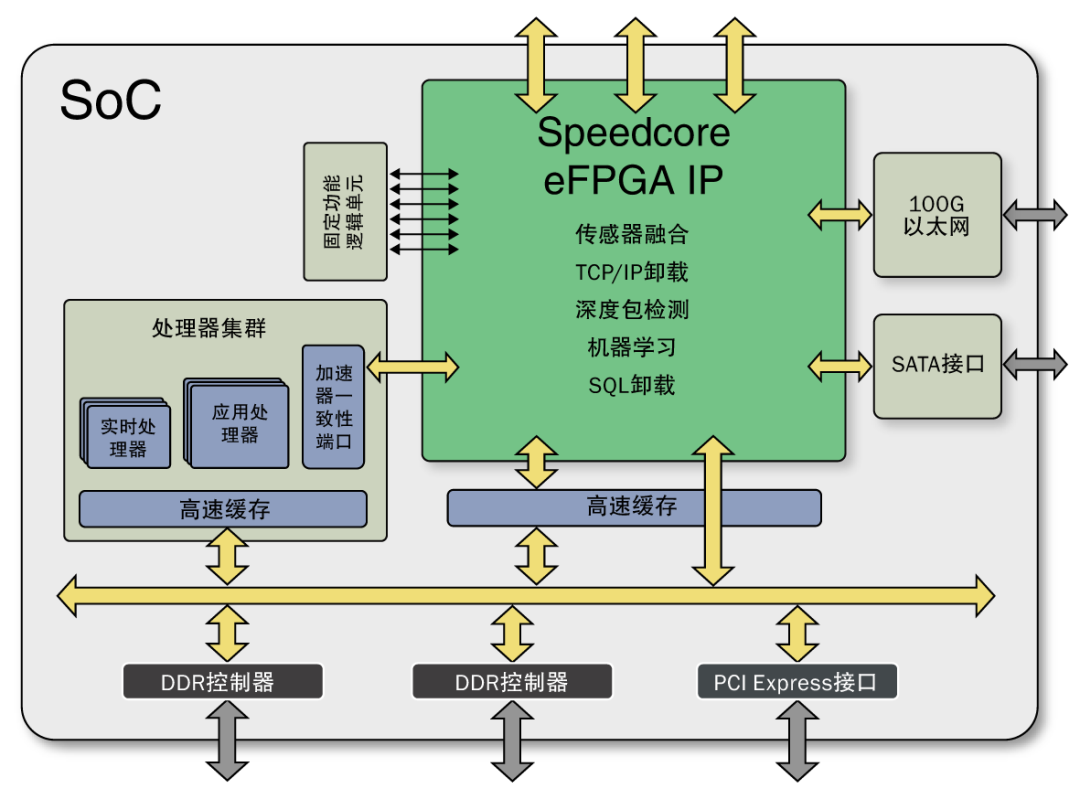

早在今年3月,Achronix即宣布累積銷售1,000萬(wàn)個(gè)采用客制ASIC出貨的Speedcore eFPGA IP核心。Speedcore eFPGA IP使用類似于標(biāo)準(zhǔn)ASIC IP模塊的設(shè)計(jì)流程,并針對(duì)5G無(wú)線基礎(chǔ)設(shè)施、網(wǎng)絡(luò)、運(yùn)算儲(chǔ)存以及先進(jìn)駕駛輔助系統(tǒng)(ADAS)芯片進(jìn)行了優(yōu)化。

正如 QuickLogic執(zhí)行長(zhǎng)Brian Faith所說(shuō)的,實(shí)施eFPGA對(duì)于SoC設(shè)計(jì)來(lái)說(shuō)風(fēng)險(xiǎn)非常低。其eFPGA IP已導(dǎo)入眾多的SoC、MCU和離散式FPGA了。現(xiàn)在,當(dāng)可編程邏輯固有的靈活性被視為極其適于加速 AI 應(yīng)用時(shí),離散式FPGA對(duì)于大量應(yīng)用來(lái)說(shuō)通常仍過(guò)于昂貴。因此,將eFPGA整合到SoC中可以節(jié)省BOM成本和功耗。

eFPGA固有的低功耗使其適用于廣泛應(yīng)用,包括手持和穿戴式裝置以及IoT端點(diǎn)。對(duì)于以AI為中心的設(shè)計(jì),eFPGA IP提供了整合固定功能區(qū)塊(例如嵌入式RAM和可分解乘法累加(MAC)的選項(xiàng),以便能有效地為神經(jīng)網(wǎng)絡(luò)和其他運(yùn)算密集型AI與機(jī)器學(xué)習(xí)(Machine Learning;ML)應(yīng)用實(shí)現(xiàn)硬件加速器。

為了確保芯片制造商能夠?qū)FPGA IP無(wú)縫地整合于其SoC設(shè)計(jì),QuickLogic已在格芯科技(Globalfoundries;GF)的22FDX平臺(tái)上對(duì)其ArcticPro 2 eFPGA IP進(jìn)行了驗(yàn)證。接下來(lái),該公司將在三星(Samsung)的28nm FD-SOI制程上提供其ArcticPro 3 eFPGA IP。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52319瀏覽量

438181 -

嵌入式

+關(guān)注

關(guān)注

5144文章

19582瀏覽量

315925 -

人工智能

+關(guān)注

關(guān)注

1805文章

48861瀏覽量

247613

原文標(biāo)題:嵌入式FPGA IP時(shí)代終于來(lái)了?

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

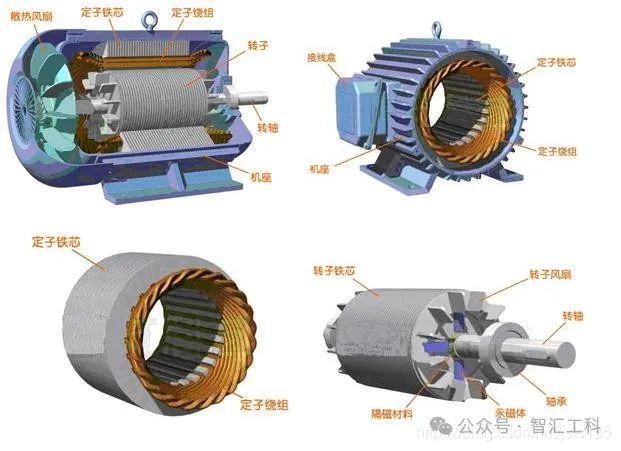

什么是電動(dòng)機(jī)定子和轉(zhuǎn)子?定子和轉(zhuǎn)子有什么作用?

Microchip發(fā)布PolarFire Core FPGA和SoC產(chǎn)品

如何將CYUSB3014-BZXI的特定GPIO引腳切換為高電平或低電平?

FPGA+AI王炸組合如何重塑未來(lái)世界:看看DeepSeek東方神秘力量如何預(yù)測(cè)......

博通涉嫌壟斷韓國(guó)機(jī)頂盒SoC市場(chǎng),達(dá)成和解

解鎖SAA認(rèn)證:通往澳大利亞市場(chǎng)的黃金鑰匙

蘋果可折疊iPhone或成市場(chǎng)轉(zhuǎn)折點(diǎn)

Achronix Speedcore eFPGA的特性和功能

SoC芯片,市場(chǎng)規(guī)模大漲

評(píng)論