Zynq&ZU+ Mpsoc的以太網(wǎng)使用普遍,從功能大致分為2類(lèi)應(yīng)用:調(diào)試管理、數(shù)據(jù)傳輸。本文主要集中在PS端的Ethernet RGMII外接phy設(shè)計(jì)和調(diào)試,該部分客戶用的最多也最容易出問(wèn)題,希望通過(guò)本文對(duì)基于RGMII+phy的典型應(yīng)用快速入門(mén),解決問(wèn)題。

1. 以太網(wǎng)接口介紹

以太網(wǎng)接口包含管理、數(shù)據(jù)通信接口,管理接口也就是我們常說(shuō)的MDC/MDIO,用來(lái)訪問(wèn)phy寄存器,配置工作模式、檢測(cè)工作狀態(tài)。數(shù)據(jù)接口:常見(jiàn)的有MII, GMII, RGMII,SGMII, QSGMII等,我們本次專(zhuān)注在RGMII。

2. MDC/MDIO接口

幀格式: CL22(GE), CL45(XE); Phy地址: 訪問(wèn)外部哪顆phy; MDC clock頻率: 不超過(guò)2.5 MHz (defined by the IEEE802.3);

|

Preamble (32bits) |

Start (2bits) |

OP Code (2bits) |

PHYAD (5bits) |

REGAD (5bits) |

Turn Around (2bits) |

Data (16bits) |

Idle | |

| Read | 1.......1 | 01 | 10 | A4A3A2A1A0 | R4R3R2R1R0 | Z0 | D15.......D0 | Z* |

| Write | 1.......1 | 01 | 01 | A4A3A2A1A0 | R4R3R2R1R0 | 10 | D15.......D0 | Z* |

硬件設(shè)計(jì)Tips:MDIO為OD門(mén),需1.5K電阻上拉。

3. RGMII接口

硬件設(shè)計(jì)Tips:RGMII規(guī)范中約定data和clock之間需要有2ns延遲,實(shí)現(xiàn)方式:

A. PCB板上繞線實(shí)現(xiàn) (不推薦);

B. PCB(data/clock等長(zhǎng)處理)+PHY芯片上分別設(shè)置TX/RX delay(現(xiàn)在phy基本上均支持,使用前請(qǐng)查看phy手冊(cè)確認(rèn));

4. 軟件開(kāi)發(fā)Tips

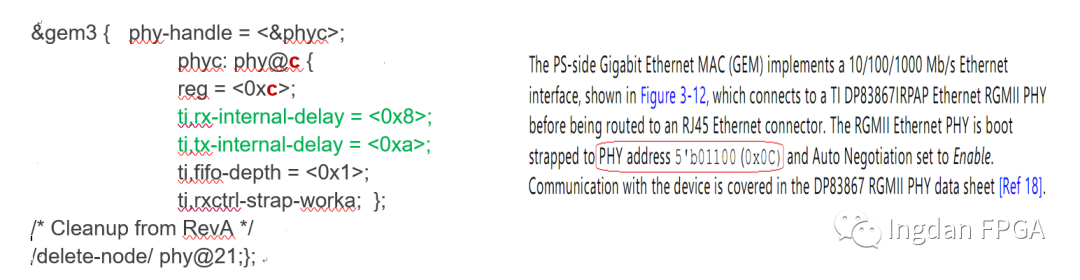

Linux如何配置phy地址&phy delay,以ZCU102為例,GEM3 phy address=0xC,采用phy internal tx/rx delay,在設(shè)備樹(shù)system-usr.dsti中添加phy地址和delay(有的phy硬件配置好,無(wú)需額外添加)。

5. 調(diào)試Tips

在uboot下通過(guò)mii命令查看phy的link/AN/Speed狀態(tài),或者配置loopback測(cè)試。

常用命令有mii info、mii dump、miiwrite等等。

通過(guò)mii info可以查看MDC/MDIO總線下掛載了哪些phy address。ZynqMP> mii infoPHY0x07: OUI = 0x5043, Model = 0x21, Rev = 0x00, 1000baseX, FDX PHY0x0C: OUI = 0x5043, Model = 0x21, Rev = 0x00, 1000baseX, FDX ZynqMP> ZynqMP>mii device MIIdevices: 'eth0' Currentdevice: 'eth0' 通過(guò)mii dump可以查看phy的狀態(tài),可讀性好。ZynqMP>mii dump 7 0 0. (1140) -- PHY control register --

(8000:0000) 0.15 =0 reset

(4000:0000) 0.14 =0 loopback (2040:0040) 0. 6,13 = b10speed selection = 1000 Mbps (1000:1000) 0.12 =1 A/N enable (0800:0000) 0.11 =0 power-down (0400:0000) 0.10 =0 isolate (0200:0000) 0. 9 =0 restart A/N (0100:0100) 0. 8 =1 duplex = full (0080:0000) 0. 7 =0 collision test enable (003f:0000) 0. 5- 0 = 0(reserved)

6. 常見(jiàn)問(wèn)題及解決方法

Q1:PHY無(wú)法訪問(wèn)? A1:查看原理圖MDIO是否有上拉、phy address是否正確、降低MDC clock測(cè)試。 Q2:能link但是ping不通? A2:PC防火墻是否關(guān)閉,包含windows自帶的防火墻?設(shè)備ip和pcip地址是否配置正確?如果以上均已操作正確,重點(diǎn)檢查RGMII PHY的TX/RX delay配置。 責(zé)任編輯:haq

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5419瀏覽量

171624 -

Zynq

+關(guān)注

關(guān)注

10文章

609瀏覽量

47176

原文標(biāo)題:Zynq & Zynq UltraScale+ MPSoC 以太網(wǎng)接口調(diào)試

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

ADS62PxxEVM快速入門(mén)指南

請(qǐng)問(wèn)DP83822IRHB該PHY要配成RGMII時(shí),到底還需要哪些配置?

TVP5154EVM快速入門(mén)指南

TVP5146:VBI快速入門(mén)

TVP5150A:快速入門(mén)指南

TVP5160 EVM快速入門(mén)指南

TVP5160 VBI快速入門(mén)

TVP5150A VBI快速入門(mén)

TVP5154A VBI快速入門(mén)

解決以太網(wǎng)RGMII通信的電源時(shí)序難題

具有SGMII和RGMII的DP83TG720S-Q1 1000base-T1汽車(chē)以太網(wǎng)PHY數(shù)據(jù)表

如何快速理解PHY芯片

allegro快速入門(mén)教程

通過(guò)磁珠解決RGMII延時(shí)不夠案例

基于RGMII+phy的典型應(yīng)用快速入門(mén)

基于RGMII+phy的典型應(yīng)用快速入門(mén)

評(píng)論