電子發(fā)燒友報(bào)道(文/吳子鵬)Chiplet,小芯片,也被譯為芯粒,其核心思想是通過預(yù)先開發(fā)設(shè)計(jì)好的die直接集成到IC封裝中,以此來降低芯片開發(fā)的時(shí)間和成本。

目前主流的做法是,如果要打造一顆高性能的芯片,需要開發(fā)一個(gè)片上系統(tǒng)(SoC),然后借助晶圓代工廠的先進(jìn)工藝將里面的功能單元微縮,在相同面積或者更小面積的裸片上實(shí)現(xiàn)更高的性能。很明顯,隨著特征尺寸逐漸逼近物理極限,且工藝復(fù)雜度越來越高,這條路越走下去難度會(huì)越大。

通俗地講,小芯片的方式就是像搭積木一樣制造芯片,AMD、英特爾、臺(tái)積電、Marvell、Cadence等產(chǎn)業(yè)巨頭對(duì)其都頗為關(guān)注,將其視為延續(xù)摩爾定律的選擇之一。在這里,我們看一下AMD在小芯片方面的布局。

可以說,業(yè)界如今對(duì)于小芯片的關(guān)注,AMD在其中起到了重要作用。小芯片概念最早可以追溯到上世紀(jì)七十年代的多芯片模組——將原來制造好的芯片再加以組裝。2014 年,芯片設(shè)計(jì)公司開始關(guān)注到這項(xiàng)技術(shù)。2016年,美國國防部高級(jí)研究計(jì)劃局Darpa 啟動(dòng)Chips 項(xiàng)目,里面提到了chiplet Reuse的想法。但小芯片真正聲名鵲起還是因?yàn)锳MD EYPC系列CPU的成功。

2017年,AMD 在其“Zen 2”架構(gòu)中使用小芯片來開發(fā)EYPC 服務(wù)器處理器“Naples”,根據(jù)當(dāng)時(shí)的AMD工程師表述,采用這樣的創(chuàng)新方式,比片上系統(tǒng)設(shè)計(jì)減少了一半的成本,并大幅降低了設(shè)計(jì)時(shí)間。隨后,AMD在消費(fèi)級(jí) CPU和企業(yè)級(jí)EPYC 處理器中都部署了“Zen 2”小芯片技術(shù)。

AMD在官網(wǎng)中提到,“Zen 2”核心在“Zen”架構(gòu)之上進(jìn)行了重大更新。主要優(yōu)勢如下:

·時(shí)鐘周期指令數(shù)提升高達(dá) 15%

·3 級(jí)高速緩存容量翻倍(高達(dá)32MB)

·浮點(diǎn)吞吐能力翻倍(256位)

·OpCache 容量翻倍(4K)

·Infinity Fabric 帶寬翻倍(512位)

·全新的 TAGE 分支預(yù)測器

我們以Ryzen 3000為例來看一下這項(xiàng)技術(shù)的創(chuàng)新點(diǎn)。在之前片上系統(tǒng)的AMD CPU中,會(huì)使用四個(gè)Zen CPU 模塊,而在Ryzen 3000中,AMD采用了Zen 2核心,也就是8個(gè)小CPU核心,采用臺(tái)積電7nm工藝,并搭載了采用格芯14nm工藝的I/O 芯片,既保證了性能,又降低了成本。

通過采用7nm工藝的小CPU核心,AMD EPYC Rome 處理器擁有多達(dá) 8 個(gè)芯片,從而使平臺(tái)能夠支持多達(dá) 64 個(gè)內(nèi)核。目前,小芯片技術(shù)已經(jīng)廣泛大量應(yīng)用于AMD的EPYC服務(wù)器CPU和線程撕裂者桌面CPU產(chǎn)品中。

在CPU取得成功之后,AMD又計(jì)劃將小芯片技術(shù)引入到了GPU領(lǐng)域。半導(dǎo)體制造設(shè)備也有光罩尺寸限制,這實(shí)質(zhì)上造成了一個(gè)障礙,無法制造更大的 GPU,這讓后續(xù)單顆GPU芯片的性能提升非常困難。在專利中AMD提到,由于多數(shù)應(yīng)用是以單個(gè)GPU為前提打造的,所以為了保留現(xiàn)有的應(yīng)用編程模型,將小芯片設(shè)計(jì)實(shí)現(xiàn)在GPU上向來都是一大挑戰(zhàn)。

為了解決這一挑戰(zhàn),AMD使用高帶寬互連來促進(jìn)小芯片之間的通信,AMD將這種交聯(lián)稱為 HBX。該方法具體的實(shí)現(xiàn)方式是將CPU連接到第一個(gè)GPU小芯片,并且用一個(gè)無源互連將L3緩存和小芯片之間的其他通道連接在一起。這意味著就 CPU而言,它與一個(gè)大GPU而不是一堆小GPU進(jìn)行通信。從開發(fā)人員的角度來看,GPU模型不會(huì)發(fā)生變化。

在 COMPUTEX 2021 上,AMD 總裁兼首席執(zhí)行官 Lisa Su分享了AMD在3D小芯片方面的最新進(jìn)展。她表示,AMD 將繼續(xù)利用 AMD 3D 小芯片技術(shù)鞏固其領(lǐng)先的 IP 和對(duì)領(lǐng)先制造和封裝技術(shù)的投資,這是一項(xiàng)封裝突破,使用行業(yè)領(lǐng)先的混合鍵合方法將 AMD 的創(chuàng)新小芯片架構(gòu)與3D堆疊相結(jié)合,提供超過200倍的互連密度,2D小芯片的數(shù)量和密度是現(xiàn)有 3D封裝解決方案的15倍以上。與臺(tái)積電密切合作率先推出的行業(yè)領(lǐng)先技術(shù),其能耗也低于當(dāng)前的3D解決方案,是世界上最靈活的主動(dòng)對(duì)主動(dòng)硅堆疊技術(shù)。

目前主流的做法是,如果要打造一顆高性能的芯片,需要開發(fā)一個(gè)片上系統(tǒng)(SoC),然后借助晶圓代工廠的先進(jìn)工藝將里面的功能單元微縮,在相同面積或者更小面積的裸片上實(shí)現(xiàn)更高的性能。很明顯,隨著特征尺寸逐漸逼近物理極限,且工藝復(fù)雜度越來越高,這條路越走下去難度會(huì)越大。

通俗地講,小芯片的方式就是像搭積木一樣制造芯片,AMD、英特爾、臺(tái)積電、Marvell、Cadence等產(chǎn)業(yè)巨頭對(duì)其都頗為關(guān)注,將其視為延續(xù)摩爾定律的選擇之一。在這里,我們看一下AMD在小芯片方面的布局。

可以說,業(yè)界如今對(duì)于小芯片的關(guān)注,AMD在其中起到了重要作用。小芯片概念最早可以追溯到上世紀(jì)七十年代的多芯片模組——將原來制造好的芯片再加以組裝。2014 年,芯片設(shè)計(jì)公司開始關(guān)注到這項(xiàng)技術(shù)。2016年,美國國防部高級(jí)研究計(jì)劃局Darpa 啟動(dòng)Chips 項(xiàng)目,里面提到了chiplet Reuse的想法。但小芯片真正聲名鵲起還是因?yàn)锳MD EYPC系列CPU的成功。

2017年,AMD 在其“Zen 2”架構(gòu)中使用小芯片來開發(fā)EYPC 服務(wù)器處理器“Naples”,根據(jù)當(dāng)時(shí)的AMD工程師表述,采用這樣的創(chuàng)新方式,比片上系統(tǒng)設(shè)計(jì)減少了一半的成本,并大幅降低了設(shè)計(jì)時(shí)間。隨后,AMD在消費(fèi)級(jí) CPU和企業(yè)級(jí)EPYC 處理器中都部署了“Zen 2”小芯片技術(shù)。

AMD在官網(wǎng)中提到,“Zen 2”核心在“Zen”架構(gòu)之上進(jìn)行了重大更新。主要優(yōu)勢如下:

·時(shí)鐘周期指令數(shù)提升高達(dá) 15%

·3 級(jí)高速緩存容量翻倍(高達(dá)32MB)

·浮點(diǎn)吞吐能力翻倍(256位)

·OpCache 容量翻倍(4K)

·Infinity Fabric 帶寬翻倍(512位)

·全新的 TAGE 分支預(yù)測器

我們以Ryzen 3000為例來看一下這項(xiàng)技術(shù)的創(chuàng)新點(diǎn)。在之前片上系統(tǒng)的AMD CPU中,會(huì)使用四個(gè)Zen CPU 模塊,而在Ryzen 3000中,AMD采用了Zen 2核心,也就是8個(gè)小CPU核心,采用臺(tái)積電7nm工藝,并搭載了采用格芯14nm工藝的I/O 芯片,既保證了性能,又降低了成本。

通過采用7nm工藝的小CPU核心,AMD EPYC Rome 處理器擁有多達(dá) 8 個(gè)芯片,從而使平臺(tái)能夠支持多達(dá) 64 個(gè)內(nèi)核。目前,小芯片技術(shù)已經(jīng)廣泛大量應(yīng)用于AMD的EPYC服務(wù)器CPU和線程撕裂者桌面CPU產(chǎn)品中。

在CPU取得成功之后,AMD又計(jì)劃將小芯片技術(shù)引入到了GPU領(lǐng)域。半導(dǎo)體制造設(shè)備也有光罩尺寸限制,這實(shí)質(zhì)上造成了一個(gè)障礙,無法制造更大的 GPU,這讓后續(xù)單顆GPU芯片的性能提升非常困難。在專利中AMD提到,由于多數(shù)應(yīng)用是以單個(gè)GPU為前提打造的,所以為了保留現(xiàn)有的應(yīng)用編程模型,將小芯片設(shè)計(jì)實(shí)現(xiàn)在GPU上向來都是一大挑戰(zhàn)。

為了解決這一挑戰(zhàn),AMD使用高帶寬互連來促進(jìn)小芯片之間的通信,AMD將這種交聯(lián)稱為 HBX。該方法具體的實(shí)現(xiàn)方式是將CPU連接到第一個(gè)GPU小芯片,并且用一個(gè)無源互連將L3緩存和小芯片之間的其他通道連接在一起。這意味著就 CPU而言,它與一個(gè)大GPU而不是一堆小GPU進(jìn)行通信。從開發(fā)人員的角度來看,GPU模型不會(huì)發(fā)生變化。

在 COMPUTEX 2021 上,AMD 總裁兼首席執(zhí)行官 Lisa Su分享了AMD在3D小芯片方面的最新進(jìn)展。她表示,AMD 將繼續(xù)利用 AMD 3D 小芯片技術(shù)鞏固其領(lǐng)先的 IP 和對(duì)領(lǐng)先制造和封裝技術(shù)的投資,這是一項(xiàng)封裝突破,使用行業(yè)領(lǐng)先的混合鍵合方法將 AMD 的創(chuàng)新小芯片架構(gòu)與3D堆疊相結(jié)合,提供超過200倍的互連密度,2D小芯片的數(shù)量和密度是現(xiàn)有 3D封裝解決方案的15倍以上。與臺(tái)積電密切合作率先推出的行業(yè)領(lǐng)先技術(shù),其能耗也低于當(dāng)前的3D解決方案,是世界上最靈活的主動(dòng)對(duì)主動(dòng)硅堆疊技術(shù)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

從 Arm 行業(yè)報(bào)告看芯片產(chǎn)業(yè)應(yīng)如何構(gòu)建面向未來十年的技術(shù)基石

半導(dǎo)體產(chǎn)業(yè)正經(jīng)歷一場由人工智能 (AI) 崛起以及傳統(tǒng)摩爾定律放緩所驅(qū)動(dòng)的關(guān)鍵轉(zhuǎn)型。在此背景下,Arm于近日發(fā)布了《芯片新思維:人工智能時(shí)代的新根基》行業(yè)報(bào)告。在報(bào)告中,來自 Arm 與業(yè)界的專家

面向未來量子通信與大物理研究線上研討會(huì)QA筆記請(qǐng)查收!

4月8日及10日,《面向未來量子通信與大物理研究》線上研討會(huì)圓滿結(jié)束。感謝大家的觀看與支持!請(qǐng)查收研討會(huì)筆記!

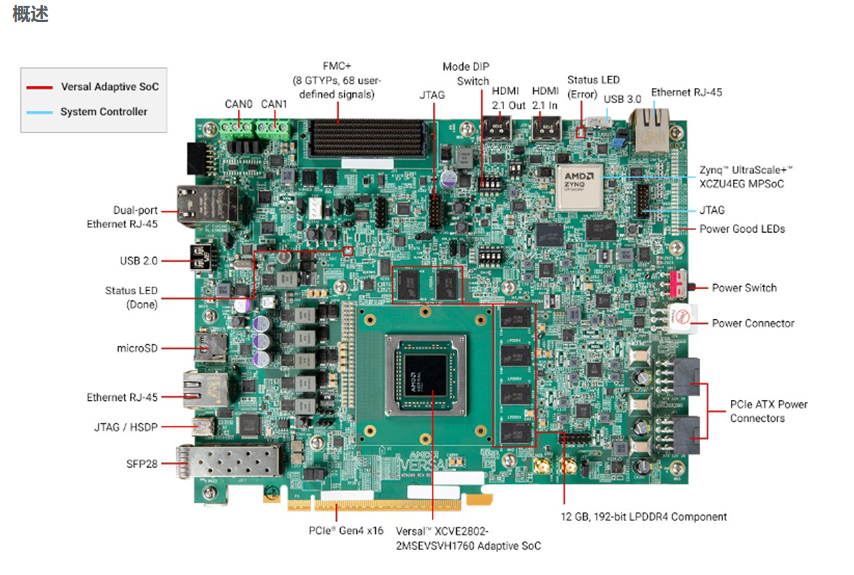

面向AI與機(jī)器學(xué)習(xí)應(yīng)用的開發(fā)平臺(tái) AMD/Xilinx Versal? AI Edge VEK280

AMD/Xilinx Versal? AI Edge VEK280評(píng)估套件是一款面向AI與機(jī)器學(xué)習(xí)應(yīng)用的開發(fā)平臺(tái),專為邊緣計(jì)算場景優(yōu)化設(shè)計(jì)。以下從核心配置、技術(shù)特性、應(yīng)用場景及開發(fā)支持等方面進(jìn)行詳細(xì)

面向未來 三星構(gòu)建移動(dòng)安全防護(hù)體系

近期,三星全新上市的Galaxy S25系列,在數(shù)據(jù)安全與隱私保護(hù)領(lǐng)域進(jìn)行了深入的創(chuàng)新實(shí)踐。通過硬件級(jí)安全架構(gòu)與創(chuàng)新加密技術(shù)的深度融合,三星構(gòu)建了面向未來的移動(dòng)安全防護(hù)體系,不僅重新定義了智能手機(jī)

案例之靈活且面向未來的ATE系統(tǒng)

得益于Intepro和Pickering公司在開放架構(gòu)硬件領(lǐng)域的緊密協(xié)作及共同愿景,雙方成功開發(fā)出一系列及時(shí)交付、量身定制、適應(yīng)性高且可擴(kuò)展的ATE(自動(dòng)化測試設(shè)備)系統(tǒng),為終端客戶帶來了顯著效益。 自1981年成立以來,Intepro公司一直專注于為電力電子組件制造商提供ATE解決方案,在航空航天、國防、汽車、醫(yī)療、電信以及可再生能源等多個(gè)關(guān)鍵領(lǐng)域積累了豐富的經(jīng)驗(yàn)。 盡管公司規(guī)模相對(duì)較小,僅在愛爾蘭、英國和美國設(shè)有辦事處并擁有25名員工,但其業(yè)務(wù)

AMD芯片首次進(jìn)入戴爾企業(yè)PC,戴爾品牌簡化新策略

近日,據(jù)彭博社報(bào)道,AMD公司在CES 2025展會(huì)上宣布了一項(xiàng)重要進(jìn)展:其芯片將首次被戴爾科技公司采用,用于面向企業(yè)客戶的個(gè)人電腦(PC)產(chǎn)品。 AMD高管在展會(huì)發(fā)言中透露,戴爾已決

AMD獲得玻璃核心基板技術(shù)專利

AMD?最近獲得了一項(xiàng)關(guān)于玻璃核心基板技術(shù)的專利,預(yù)示著在未來幾年內(nèi),玻璃基板有望取代傳統(tǒng)的多芯片處理器有機(jī)基板。這項(xiàng)專利不僅體現(xiàn)了AMD在相關(guān)技術(shù)領(lǐng)域的深厚研究,還使公司在

使用 AMD Versal AI 引擎釋放 DSP 計(jì)算的潛力

的 DSP 應(yīng)用。 AMD Versal AI 引擎使您能夠擴(kuò)展數(shù)字信號(hào)處理 (DSP) 計(jì)算和面向未來的設(shè)計(jì),以適應(yīng)當(dāng)前和下一代計(jì)算密集型 DSP 應(yīng)用。借助 Versal AI 引擎,客戶可以期望以

AMD加入玻璃基板戰(zhàn)局

AMD已獲得一項(xiàng)專利,該專利涵蓋玻璃核心基板技術(shù)。未來幾年,玻璃基板將取代多芯片處理器的傳統(tǒng)有機(jī)基板。這項(xiàng)專利不僅意味著AMD已廣泛研究了相關(guān)技術(shù),還將使該公司

AMD或涉足手機(jī)芯片市場

近日,據(jù)行業(yè)內(nèi)部知情人士透露,全球知名的半導(dǎo)體巨頭AMD正計(jì)劃進(jìn)軍移動(dòng)設(shè)備芯片市場,此舉或?qū)橐苿?dòng)計(jì)算領(lǐng)域帶來一場新的變革。 據(jù)悉,AMD擬推出的新產(chǎn)品將采用臺(tái)積電先進(jìn)的3納米工藝制造,這一決策不僅

使用AMD Versal AI引擎加速高性能DSP應(yīng)用

AMD Versal AI 引擎使您能夠擴(kuò)展數(shù)字信號(hào)處理( DSP )算力與面向未來的設(shè)計(jì),從而適應(yīng)當(dāng)前和下一代計(jì)算密集型 DSP 應(yīng)用。借助 Versal AI 引擎,客戶能以更低的功耗1和更少的可編程邏輯資源2獲得高性能 DSP。

AMD發(fā)布新一代AI芯片MI325X

在舊金山舉辦的Advancing AI 2024大會(huì)上,AMD正式推出了其新一代AI芯片——GPU AMD Instinct MI325X。這款芯片的發(fā)布標(biāo)志著

AMD AI芯片需求井噴,業(yè)績預(yù)估再獲提升

全球芯片巨頭AMD近期發(fā)布的財(cái)報(bào)與未來財(cái)測數(shù)據(jù)令人矚目,尤其是其在數(shù)據(jù)中心領(lǐng)域的強(qiáng)勁表現(xiàn),再次引發(fā)了市場的熱烈反響。AMD的執(zhí)行長蘇姿豐更是直接表示,AI

面向手機(jī)直連的星載相控陣:關(guān)鍵技術(shù)與未來展望

電子發(fā)燒友網(wǎng)站提供《面向手機(jī)直連的星載相控陣:關(guān)鍵技術(shù)與未來展望.pdf》資料免費(fèi)下載

發(fā)表于 07-23 12:39

?0次下載

使用STM32F407ZGT6的設(shè)備無法連接到AMD處理器的電腦上,怎么處理?

使用貴公司的STM32芯片,型號(hào):STM32F407ZGT6。CAN總線轉(zhuǎn)串口,可以正常連接到英特爾處理器的電腦上;但是無法連接到AMD處理器的電腦上。請(qǐng)問怎么處理?

連接到AMD處理器的電腦上,串口顯示如下:

發(fā)表于 07-23 07:58

解密AMD面向未來的小芯片設(shè)計(jì)

解密AMD面向未來的小芯片設(shè)計(jì)

評(píng)論