在數字電路教程的組合邏輯部分,最經典的示例除了加法器以外就是:

Encoder - 編碼器

Decoder - 譯碼器

Multiplexer - 簡寫Mux,多路復用器,也叫數據選擇器

Demultiplexer - 簡寫Demux,解復用器,也叫數據分配器

其實是兩對概念:Encoder/Decoder是跟code(碼)相關的正反兩個操作,Mux/Demux是跟數據流相關的正反兩個操作。

翻看各種教科書,我們很難理清楚它們之間的功能差異以及相互之間的關系,只是有一些點滴應用在書本上提及。

這兩組概念其實是非常重要的,是構成我們信息組織和信息傳輸的重要基礎,并且在我們的生活中處處都能夠找到與之對應的應用:

比如我們看諜戰片中神秘的電報編碼(要用密碼本來翻譯);我們用的鍵盤上面有100多個按鍵、而幾根線就可以將它跟計算機連接;我們使用的旋轉撥碼開關、模數轉換器中通過比較器輸出的比較結果到最終用于表征模擬信號大小的數據,這些都被稱為Encode - 編碼。

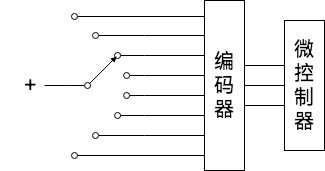

單刀八擲的旋轉開關可以用3根二進制數據線來表征其狀態

簡而言之,編碼器是一種把熟悉的數字、字符或符號轉換成二進制代碼的裝置,它將給定的信息編碼成更緊湊的形式,主要用于減少表示給定信息所需的比特數。在數字系統中,編碼器用來傳輸或存儲信息,通過編碼傳輸鏈路可以使用更少的線路來傳輸或更少的空間來存儲。將量化的音樂通過編碼器轉換為MP3格式,將采集到的視頻流通過編碼器轉換為MP4的數據格式,這些過程都統稱為“編碼” ,當然在我們的數字電路教程中,只是通過最簡單的示例來講述其原理。

就像電報中的編碼有很多中一樣,用二進制來表征數字、字符或符號也有多種不同的方式,比如BCD、5421碼、2421碼、余3碼、格雷碼等,每種編碼方式都有其優缺點,因此有用于不同的場景。

譯碼器(Decoder)是編碼器的逆過程,它是把二進制表征的信息給翻譯過來,或者說映射過來,我們生活中的門牌號、車牌號、郵箱、組合開關對多個燈的控制、嵌入式系統中的存儲器/外設尋址,這些都是譯碼的過程,通過代碼中的數字,找到其對應的對象。在數字計算中,代碼中的數字都是用二進制(擴展為8進制、16進制等,本質上也是2進制)。數字電路教程中,在譯碼器部分最常用到的例子就是3:8譯碼器,這是因為74HC138就是這么一個IC,比較適合做各種實驗,當然7段數碼管的控制也是非常重要的實驗項目讓同學們來體會譯碼的過程,通過幾根控制線的電平組合,可以點亮數碼管上7個LED燈中的若干個,從而組合出我們需要顯示的數字。

我們硬禾學堂也專門針對譯碼部分制作了兩個視頻案例,一個是2:4譯碼,一個是3:8譯碼,雖然看起來沒啥大的區別,但我們還是通過這兩個實例來讓大家體會Verilog代碼實現的不同方式,希望對學習Verilog的同學有幫助。

FPGA中的邏輯單元的基本構成就是LUT - 查找表,其理論基礎就是譯碼,比如我們小腳丫FPGA中采用的是4輸入LUTS,通過查找表的方式代替邏輯門的構成,4個輸入作為RAM的地址,可以尋址16個不同的地址空間內存儲的信息。

是不是感覺編碼器/譯碼器用途很廣?

那Mux/Demux呢?想象一下從四條不同路徑過來的車輛要并線到一條路上,由紅綠燈控制,控制部分就相當于一個分時切換的開關,根據開關的控制碼來決定哪一路的車輛通行,Mux又稱為多路數據選擇器,Demux又被稱為數據分配器。

其實MUX不僅用于數字器件中,模擬電路中也有這個概念,我們所說的模擬開關,可以切換不同的輸入與輸出的連接,在模擬電路中Mux和Demux是一體的,同一個電路即是Mux又是Demux。而數字的Mux和Demux需要使用不同的器件。

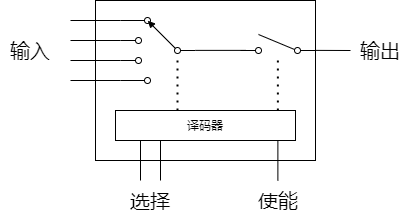

復用器的構成

從上面的圖中可以看出譯碼器是復用器構成的重要部分。復用器的控制信號就是通過譯碼以后,對應到相應的控制端點,從而實現對輸入信號的選擇通過的。

復用器/解復用器的Verilog邏輯異常簡單,有一點程序基礎的同學一看就懂,比如下面的4選1多路選擇器,一個case語句搞定,case的條件是2個選擇數據為sel1、sel0,sel1和sel0的4種組合決定了一個LED同4個不同輸入信號的連接。

很容易看懂,是因為我們任何一門編程語言中的if else、case本質上都是Mux的功能,只是我們太習以為常了而已。

module mult4 ( input wire a, //定義四位輸入 input wire b, input wire c, input wire d, input wire [1:0] sel, //定義輸出的選擇變量 output reg led //定義選擇器輸出結果對應的led ); always@(sel) //根據sel結果選擇輸出,當sel變化時執行 begin case(sel) 2‘b00: led = a; 2’b01: led = b; 2‘b10: led = c; 2’b11: led = d; endcase end endmodule

從這幾行代碼看,FPGA的使用非常簡單,不需要你畫門與門之間的邏輯關系圖,只需要用Verilog這種硬件描述語言來描述一下其因果關系就可以了。

與Encoder、Decoder、Mux、Demux相關的案例及其FPGA實現都匯總在www.stepfpga.com的網站百科中,如果您使用我們的Web IDE(不需要下載安裝FPGA工具),也可以找到相關的參考案例,自己去發掘嘍。

責任編輯:haq

-

電路

+關注

關注

173文章

6028瀏覽量

175152 -

復用器

+關注

關注

1文章

766瀏覽量

29065

原文標題:淺談“數字電路”的學習(8)- 編碼器、譯碼器、多路復用器、解復用器的關系和應用

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論