1. 簡介

Jlink 想必大家都用過,相信登錄過 segger 官方網站,下載最新的 jlink 驅動程序的時候,都會看到這樣的圖片:

在興嘆它那離譜的價格的同時,也會好奇這個東西比手里的x版貨都有哪些優勢和提升。

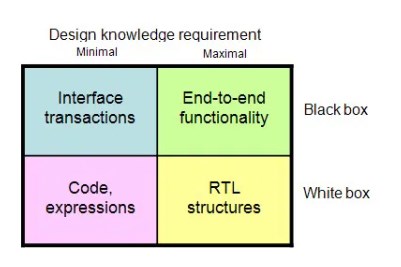

以上圖片是 segger 官方對 J-Trace 的定位:

使用基于 segger 領先的 trace 方案 J-Trace PRO 實現對代碼的收集、驗證、分析功能。利用 Arm Cortex 內核的 trace 功能,在無限時長內,實現對所有指令的跟蹤,實現對偶然出現的、難以被復現的 bug 追蹤記錄。

在完整的 System Clock 內實時流式傳輸 trace。

使用在線代碼分析功能來精細優化代碼。

指令級別的代碼覆蓋率檢測,為滿足安全性規約約束的需求。

無限制的 trace 追蹤,實現隔離和識別潛在的代碼缺陷。

完整的 J-Link 調試功能

可以看出它最大的賣點就在 arm trace 的信號流捕捉和分析,實現代碼的精確流程跟蹤,有了精確的代碼跟蹤,就可以借助 Ozone 工具提供實時分析代碼覆蓋率、指令回溯、CPU 資源監控等功能。

這么多優點,配合強大的 Ozone 調試平臺,code coverage 實時統計,一鍵生成報表,boom。仿佛那最后的 bug 就可以用它來反復蹂躪、踩在腳底。..感動人心!直到看到售價:

Price: €1,980 EUR

這個價格可以買一臺高配的 MacBook 了,但對比其他支持trace接口的調試器來說,性價比出眾,例如 trace32。

2. 物理連接

如圖所示 segger 的 19 pin trace 接口(1.27mm 牛角),在 JTAG 基礎上增加了 5 條 trace 線(4 條數據線 + 1 條時鐘線,雙邊沿模式(DDR))。

有一點要注意一下,不要把兩個接口都接到板子上:

Note: Never connect trace cable and JTAG cable at the same time because this may lead tounstable debug and trace connections.

注意:不要同時使用 trace 連接線和 JTAG 連接線,這將導致 debug 和 trace 的不穩定現象。

參考:《UM08001: J-Link / J-Trace User Guide》

3. 打錢

既然本篇目主要介紹 J-Trace 的入門教程,自然就需要有這么一臺設備支持一下了。

三句話,讓老板為我花了1W8,終于拿到它:

你要問盒子里有沒有跳線帽,這個真沒有:

可以看見這個板子使用了 ARM cortex A9 + FPGA 的 Zynq-7010 作為主控,通過 Zynq 專有總線與賽普拉斯 CYUSB3011 USB3.1 控制器連接,CYUSB3011 內部也具備一顆 ARM926 200MHz 的控制核心,用于協調 USB3.1 高速傳輸協議。

周邊還有美滿的千兆 phy 收發器,芯成的LPDDR2 128MBytes 533Mhz,用于高速收發和緩沖 trace packet,對于電腦主機來說盡量配備大內存和獨立的 USB3.0 接口。

外圍就是一些電平轉換電路和電源了,都是 TI 的一些常見型號,總的來看 JTAG 和 trace port 的邏輯由 FPGA 硬件邏輯實現,當作 J-Link 可以用 zui 高速調試,下載效果要好很多。

4. 什么是 Trace

在上一節我們簡單介紹了 J-Trace ,至于為什么三句話說服了老板,我們還是要以專業視角看 trace 的引入能夠解決哪些實際的問題。

J-Trace 的標準包裝很“貼心”地贈送了一張 STM32F407 核心板,它用的不是標準 Jtag 接口,而是支持 Trace 的接口,我們可以像官網那樣去連接和測試 Trace 功能:

翻看 STM32F407 的 RM(RM0090.pdf) 手冊,找到 Debug support 章節,可以看見 芯片內部負責 Debug 的系統框圖:

可以看見我們主要關注且日常見到的一些片上調試模塊:

SWJ-DP: Serial wire / JTAG debug port

AHP-AP: AHB access port

ITM: Instrumentation trace macrocell

FPB: Flash patch breakpoint

DWT: Data watchpoint trigger

TPUI: Trace port unit interface

ETM: Embedded Trace Macrocell

以及文中提及到,STM32F4xx 系列支持的擴展功能:

Flexible debug pinout assignment

MCU debug box (support for low-power modes, control over peripheral clocks, etc.)

歸納一下就是:

SWJ-DP 這個大家都熟悉,不必介紹,其他的也許使用過,但多數情況下我們不會在意它們的存在。

ITM 可以支持 SWO 輸出調試,挖個坑下回填。

很多定位中低端的MCU就直接丟棄掉 Trace Port 相關電路單元了,加上對外接調試設備的高要求(貴)以至于很多工程師并不知道 ARM Cortex 上其實還有 JTAG/SWD 之外的調試端口。

本文重心圍繞指令追蹤,我們重點來看 ETM:

對于ETM,需要了解:

ETM 的主要任務是幫助開發者重建程序執行序列,CPU 上所有指令的執行都可以被 ETM 追蹤到。

數據可由 DWT 或者 ITM 單元追蹤到。

Embedded Trace Macrocell (ETM) 提供結合了 ARM 的調試和追蹤機制,它可以做到在不干擾 CPU 的情況下獲取 CPU 的運行狀態,一旦捕捉到,便實時通過特定的 Trace 端口向外輸出。

具備 ETM 模塊的 MCU 可以實現詳盡的指令執行歷史記錄,這些記錄可以作為重現代碼流程和執行時間的依據,使用分析軟件實現代碼分析,借此找到難以復現的bug。最難能可貴的是,它可以幫助我們找到失控的代碼的根源所在。

此外,ETM還有更多特性有待進一步了解,比如常見的 ETB、Filter & Package Formatter 等細節屬性,有待進一步啃手冊了。

更多有關 ETM 資料,請翻閱《Embedded Trace Macrocell Architecture Specification》 、《ARM CoreSight Architecture Specification》 、《ARMv7-M Architecture Reference Manual》

綜上,ETM 并不是對外輸出的最終形式,在 STM32F4xx RM0090.pdf 中有如下結構:

可見 ETM 和 ITM 生成 CPU 運行的追蹤信息后,由 TPIU 模塊執行封包,并使用對外已經連接的序列器輸出,由這張圖片可以得出以下結論:

終于涉及到物理層連接了,自然就會引出物理連接概念:Trace signal timing (追蹤信號時序)

上一章節我們知道 ETM 信息是可以和 CPU 同頻的,以達到最佳的指令追蹤覆蓋效果,對于 Cortex-M 架構,ARM 有如下定義:

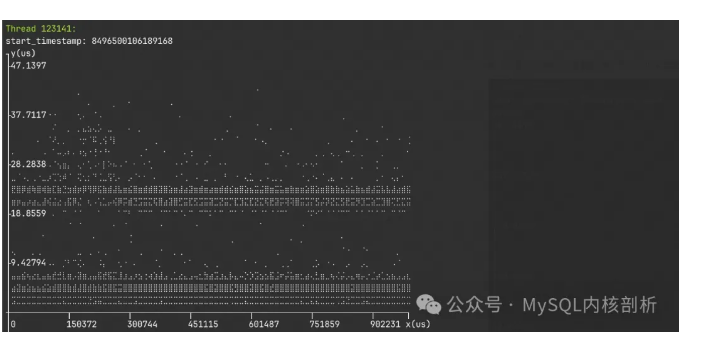

trace 時鐘往往是 1/2 的 CPU 時鐘,但是 trace data 線路可以是 DDR (雙倍速率-亦稱上升下降沿)方式通信,通常 data 線有4條,意味著一個 trace 時鐘周期可以輸出1個字節的 trace 數據。

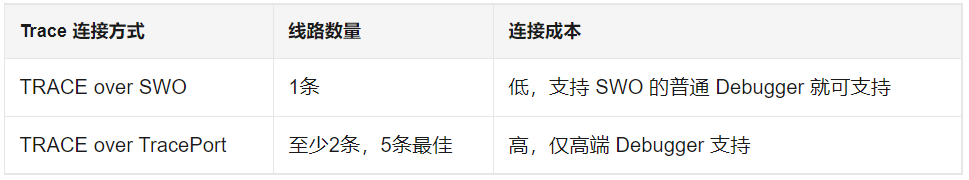

trace 硬件接入,筆者經驗總結:

如今 MCU 主頻也在不斷遞進,為了保持高速的 trace 也必然對線路阻抗與信號輸出能力提出了更苛刻的要求。由于是 DDR 方式地獲取追蹤數據,所以在 Layout 上就需要做好等長,為了保證良好的 trace 穩定性,也應當從 MCU IO 翻轉輸出能力和CPU主頻兩個角度的上限妥協一個較為穩定的時鐘速率。

由于是高速 DDR 信號,時序上要盡量滿足以下要求:

Trace CLK 作為時鐘基準,如上圖所示 Trace Data 被時鐘上升或下降沿一分為二(50%占空比)是最佳的信號效果,如果 Trace Data 出現了較多的超前或者滯后,也可以在 Ozone 中設置延遲補償,這里不過多介紹了。

5. 總結

Trace 能夠幫助解決面向過程測試中,以不干擾CPU正常運行為前提,揭示程序運行蹤跡,解決最麻煩的bug。

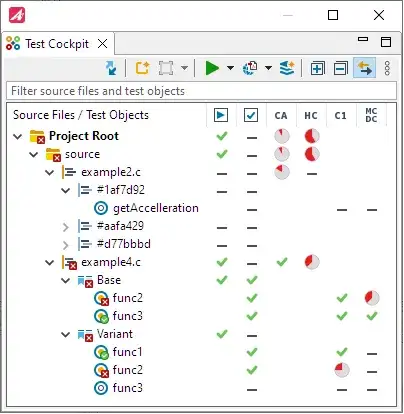

Trace 輔助工具可以實現代碼分析與實時覆蓋率統計,幫助我們以直觀運行視角,揭示代碼優化方向。

這套工具除了貴沒別的不好,Ozone 調試功能強大且好用,它是免費的,只需要有 J-Link 就行。

責任編輯:haq

-

驅動

+關注

關注

12文章

1844瀏覽量

85367 -

DDR

+關注

關注

11文章

712瀏覽量

65405

原文標題:J-Trace入門系列1:感動人心的功能與更感動人心的售價

文章出處:【微信號:RTThread,微信公眾號:RTThread物聯網操作系統】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

TSP工具包軟件的應用說明

synopsys 的design ware:DW_fpv_div,浮點數除法器,默認32位下,想提升覆蓋率(TMAX),如果用功能case去提升覆蓋率呢?

利用靜態檢查工具完善功能安全中測試覆蓋率

如何使用Intel Processor Trace工具查看任意函數執行時間

QE for Cap Touch工具使用問題總結

單元測試工具TESSY 新版本亮點速覽:提供測試駕駛艙視圖、超級覆蓋率、代碼訪問分析、增強覆蓋率審查

頻譜分析設備是入侵報警前端設備嗎

OpenAI推出GPT-4o助力用戶普及AI工具應用

谷歌將優化安卓系統的實時字幕功能,用戶可更改字幕行數

如何將SystemVerilog斷言屬性和覆蓋屬性置于在設計上?

什么是工業軟件 工業軟件分類及代表廠商

QE for Motor V1.3.0:汽車開發輔助工具解決方案工具包

代碼靜態測試工具Helix QAC 2023.4新發布

Trace輔助工具實現代碼分析與實時覆蓋率統計

Trace輔助工具實現代碼分析與實時覆蓋率統計

評論