優秀的 Verilog/FPGA開源項目介紹(五)- USB通信

USB是我們生活中非常非常常見的接口,鼠標、鍵盤以及常見的U 盤等,可以說現在的USB設備已經滲透到生活中的方方面面,下面就介紹幾個開源的USB IP,供大家學習。

0-官方網站

https://www.usb.org/?

很多人花各種XX幣下載各種標準,其實太浪費時間和精力了,這里介紹一個網站--usb.org。

USB Implementers Forum, Inc. 是一家非營利性公司,由開發通用串行總線規范的公司集團創立。USB-IF 的成立是為了為通用串行總線技術的進步和采用提供支持組織和論壇。該論壇促進了高質量兼容 USB 外圍設備(設備)的開發,并促進了 USB 的優勢和通過一致性測試的產品質量。

1-usbcorev

項目地址

https://github.com/avakar/usbcorev?

項目簡介

該IP可以將全速 (12Mbps) USB 2.0 設備內核嵌入到 FPGA 設計中。

接口部分

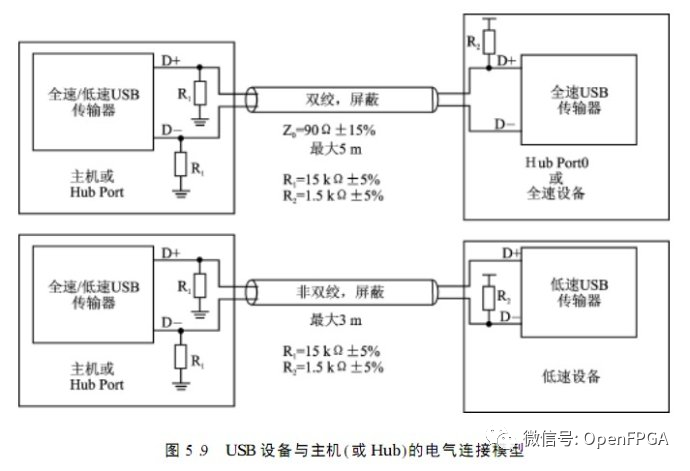

我們知道USB接口使用了差分結構,所以接口部分還是很復雜的。

由于 USB 在其半雙工差分線上使用了一些奇怪的信號,因此需要做一些工作才能將其連接到核心。以下五個信號連接到USB 信號的 D+ 和 D- 。

-

input rx_j -- D+/D-線上的微分值

-

input rx_se0 -- 單端零檢測:應在 D+ 和 D- 線均為零時設置

-

output tx_se0-- 在兩條 USB 線上傳輸零;優先于tx_j

-

output tx_j-- 傳輸tx_j到 D+ 和~tx_jD-

-

output tx_en -- 啟用發射器

如果使用的 FPGA 沒有差分接收器,那么可以簡單地使用兩個引腳并按如下方式連接它們。但是,如果沒有差分接收器,這將超出 USB 規范。

inoutusb_dp;

inoutusb_dn;

//...

wireusb_tx_se0,usb_tx_j,usb_tx_en;

usbusb0(

.rx_j(usb_dp),

.rx_se0(!usb_dp&&!usb_dn),

.tx_se0(usb_tx_se0),

.tx_j(usb_tx_j),

.tx_en(usb_tx_en));

assignusb_dp=usb_tx_en?(usb_tx_se0?1'b0:usb_tx_j):1'bz;

assignusb_dn=usb_tx_en?(usb_tx_se0?1'b0:!usb_tx_j):1'bz;

對于 Xilinx Spartan 6 系列,使用四個物理引腳如下。

//Thesepinsareconfiguredasdifferentialinputs.Unfortunately,

//youcan'tusesingle-endedreceiversnortransmittersonthesepins.

inputusb_sp;

inputusb_sn;

//Thesepinsaresingle-endedinouts.

inoutusb_dp;

inoutusb_dn'

//...

IBUFDSusb_j_buf(.I(usb_sp),.IB(usb_sn),.O(usb_rx_j_presync));

synchusb_j_synch(clk_48,usb_rx_j_presync,usb_rx_j);

synchusb_se0_synch(clk_48,!usb_dp&&!usb_dn,usb_rx_se0);

wireusb_tx_se0,usb_tx_j,usb_tx_en;

usbusb0(

.rx_j(usb_rx_j),

.rx_se0(usb_rx_se0),

.tx_se0(usb_tx_se0),

.tx_j(usb_tx_j),

.tx_en(usb_tx_en));

assignusb_dp=usb_tx_en?(usb_tx_se0?1'b0:usb_tx_j):1'bz;

assignusb_dn=usb_tx_en?(usb_tx_se0?1'b0:!usb_tx_j):1'bz;

注意接收器之后的同步。

無論在哪個引腳上傳輸,都需要在線路上增加串阻,通常大約 27 歐姆就可以了。

還需要將 D+ 線增加1.5K的 3.3V 上拉。如果您想動態連接/分離到總線,可以直接或通過 FPGA 上的引腳拉動它。確保永遠不要下拉線路,上拉引腳的唯一有效輸出是1'b1和1'bz。

2-no2usb

https://github.com/no2fpga/no2usb?

該項目是Lattice眾多擁簇的一員的項目,平臺也是運行在ice40中,之前我也做了一個開發板(),奈何國內對這個感興趣的不過,也就沒怎么推廣。

下面簡單介紹一下這個項目。

概述

該 fpga 內核僅使用普通 FPGA CMOS IO 實現 USB 全速 SIU(Server Interface Unit)。

- 小巧高效(最初針對 ice40)

- 靈活,動態 EP 配置

- 單時鐘域

該項目目前只運行在ice40芯片(Apple曾使用的)上,目前在適配ecp5(lattice)。

說明

?https://github.com/smunaut/ice40-playground/tree/master/cores

?

3-tinyfpga_bx_usbserial(USB轉串口 SPI)

?https://github.com/davidthings/tinyfpga_bx_usbserial

?

這個項目的起源也很有意思,ice40系列FPGA是使用SPI接口燒寫程序的(類似JTAG),使用時需要一個USB轉SPI芯片作為“JTAG”,常用的就是FT232/FT2232等,但是FTDI的芯片價格普遍比較貴(差不多和ICE40一樣價格甚至更貴),本項目的起源就是為了節省這一芯片,使用FPGA本身實現USB-SPI。

項目起源地址

?https://github.com/tinyfpga/TinyFPGA-Bootloader

?

簡介

Lawrie Griffiths 深入研究了這段代碼的"暗盒",并做了大量工作將其更改為 USB - SERIAL 橋接器,將用戶視為串行端口,而不是 SPI 主機。他還創造了一些很好的例子,他的工作在這里:

?https://github.com/lawrie/tiny_usb_examples

?

本項目針對以上兩個項目做了一些改善。并且做了很多改善,不僅使用ICE40系列FPGA還適配了XIlinx A7 FPGA,同時ECP5(Lattice)也可以使用。

項目資源使用如下:

Info:Deviceutilisation:

Info:ICESTORM_LC:1093/768014%

Info:ICESTORM_RAM:2/326%

Info:SB_IO:9/2563%

Info:SB_GB:8/8100%

Info:ICESTORM_PLL:1/250%

Info:SB_WARMBOOT:0/10%

項目的README中有詳細的介紹及使用教程,這里就介紹的這里,畢竟不是完整的USB通信。

4-眾多IP核

?https://github.com/ultraembedded/cores

?

這個項目不僅不包括了USB(主要是USB1.1),還包括很多常見的低速接口-SPI UART I2S等等

每個IP都有完整的說明,自己去看吧,非常適合新手調試接口。

5-usb_cdc(設備類)

?https://github.com/ultraembedded/core_usb_cdc

?

USB的CDC類是USB通信設備類 (Communication Device Class)的簡稱。CDC類是USB組織定義的一類專門給各種通信設備(電信通信設備和中速網絡通信設備)使用的USB子類。

簡介

該項目是一個簡單的 USB 外設接口(設備)實現,可枚舉為高速 (480Mbit/s) 或全速 (12Mbit/s) CDC-ACM 設備。

該 IP 具有用于輸入和輸出數據的簡單 FIFO 接口(有效、數據、接受),以及用于連接到 USB PHY 的 UTMI 接口。

特征

- 高速或全速 USB CDC 設備。

- 硬件枚舉 - 無需軟件干預。

- UTMI PHY 接口

- 具有握手功能的簡單 8 位數據輸入/輸出接口(符合 8 位寬 AXI4-Stream 接口)。

- 配置/要求(全速(12Mbit/s))

文件說明

Configuration/Requirements(FullSpeed(12Mbit/s))

Top:usb_cdc_core

Clock:clk_i-48MHzor60MHz

Reset:rst_i-Asynchronous,activehigh

VID/PIDcanbechangedinusb_desc_rom.v

Param:USB_SPEED_HS="False"

Configuration/Requirements(HighSpeed(480Mbit/s))

Top:usb_cdc_core

Clock:clk_i-60MHz

Reset:rst_i-Asynchronous,activehigh

VID/PIDcanbechangedinusb_desc_rom.v

Param:USB_SPEED_HS="True"

該項目在仿真下驗證,在 FPGA 上針對 Linux、Windows 和 MAC OS-X 進行了測試。

6-www-asics-ws的項目

?https://github.com/www-asics-ws

?

www-asics-ws項目中包含了USB1.1和USB2.0設備類USB IP。

usb1_device

usb2_dev

這是一個符合 USB 2.0 標準的內核。由于接口速度高,此內核需要外部 PHY。已開發出用于 USB 的行業標準 PHY 接口。該接口稱為USB Transceiver Macrocell Interface或簡稱UTMI。USB 內核的主機接口符合 WISHBONE SoC 標準。有關 USB 標準和完整規范的更多信息,請訪問www.usb.org。有關 WISHBONE SoC 的更多信息和完整規范,請訪問www.opencores.org。UTMI 規范(以及其他各種有用的 USB 文件)可以從這里下載:https : //www.intel.com/content/www/us/en/io/universal-serial-bus/universal-serial-bus-specifications .html

參考意義不大,不能直接在FPGA中使用,需要搭配PHY使用。

7-usbhostslave

?https://github.com/freecores/usbhostslave

?

該項目已使用 Quartus 6.0 成功編譯并且USBHostSlave 已經在 SystemC 和 Altera Nios 開發套件 Cyclone 版中進行了測試。

整個項目文檔說明很少,但是看提交記錄該項目完成度很高,還是適合入坑。

優秀的 Verilog/FPGA開源項目介紹(四)- Ethernet

9-core_usb_sniffer

?https://github.com/ultraembedded/core_usb_sniffer

?

這個內核是一個 HS/FS USB2.0 分析器(USB 總線嗅探器)。

內核監控 UTMI 接口,并通過 AXI-4 總線主接口將看到的流量記錄到內存緩沖區。

可以連續提取日志格式(連續捕獲模式),也可以在內存緩沖區已滿時內核停止捕獲(一次性模式)。

IP 的配置是使用 AXI4-Lite 從接口執行的。

該內核已用于生產USB 2.0 捕獲設備(https://github.com/ultraembedded/usb2sniffer)這是實現的案例。

10-商業IP

?https://www.synopsys.com/designware-ip/interface-ip/usb.html

?

商業IP肯定首推來自老牌大廠新思,新思科技在2018年推出基于HAPS-80 FPGA的硬件原型驗證平臺上部署了USB 3.2設備IP和主機IP。這些FPGA硬件原型驗證平臺在FinFET工藝節點的FPGA中使用了USB PHY。解決方案如下:

有需要的可以去上面的網站了解,需要money的IP,所以我就不過多介紹了,個人也不會選用,大公司自然有銷售對接。

以上就是今天推薦的項目,這里建議第一個和第五個項目可以入坑,其他看自己需求。

最后,還是感謝各個大佬開源的項目,讓我們受益匪淺。后面有什么感興趣方面的項目,大家可以在后臺留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604382 -

USB 2.0

+關注

關注

1文章

23瀏覽量

17423 -

IP

+關注

關注

5文章

1712瀏覽量

149676 -

PHY

+關注

關注

2文章

305瀏覽量

51788

原文標題:優秀的 Verilog/FPGA開源項目介紹(五)- USB通信

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

利用FPGA實現USB 2.0通信接口

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog vhdl fpga

FPGA加速深度學習模型的案例

怎么樣提高verilog代碼編寫水平?

FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

如何用FPGA實現一個通信系統的發射端接收機?

【招聘】verilog vhdl FPGA

8月全志芯片開源項目分享合集

FPGA開源項目:Verilog常用可綜合IP模塊庫

優秀的 Verilog/FPGA開源項目之 USB通信

優秀的 Verilog/FPGA開源項目之 USB通信

評論