《UltraFast 設計方法時序收斂快捷參考指南》提供了以下分步驟流程, 用于根據《UltraFast設計方法指南》( UG949 )中的建議快速完成時序收斂:

1初始設計檢查:在實現設計前審核資源利用率、邏輯層次和時序約束。

2時序基線設定:在每個實現步驟后檢查并解決時序違例,從而幫助布線后收斂時序。

3時序違例解決:識別建立時間違例或保持時間違例的根源,并解決時序違例。

01

初始設計檢查詳細介紹

在賽靈思器件上實現設計,是一個自動化程度相當高的任務。但是,要實現更高的性能、解決時序或布線違例帶來的編譯問題,則是一項復雜且耗時的工作。僅根據簡單的日志消息或由工具生成的實現后時序報告,可能難以明確失敗原因。因此,按步驟進行設計開發和編譯非常必要,其中就包括復查中間結果,以確保設計能繼續執行下一個實現步驟。

第一步是確保所有的初始設計檢查都已經完成。在下列層次復查檢查結果:

由定制 RTL 構成或者由 Vivado HLS 生成的每個內核。注意:檢查目標時鐘頻率約束是否現實。

與子系統逐一對應的每個主要層級,例如有多個內核、IP 塊和連接邏輯的 Vivado IP integrator 模塊框圖。

包括所有主要功能和層級、I/O 接口、完整時鐘電路、物理約束和時序約束的完整設計。

如果設計使用布局規劃約束, 如超級邏輯區域( SLR )分配或分配給 Pblock 的邏輯,請復查每項物理約束的估算的資源利用率,確保符合資源利用率準則。

02

時序基線設定示例

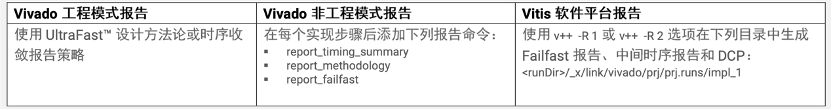

時序基線設定的目的是,通過在每個實現步驟后分析和解決時序問題,確保設計滿足時序要求。在編譯流程中,盡早糾正設計問題和約束問題能實現更高性能,并帶來更廣泛的影響。通過創建如下中間報告,在進入下一步前復查并解決時序違例:

03

分析建立時間違例流程

設計性能主要由三個因素決定:一、時鐘偏差與時鐘不確定性,主要包括時鐘如何高效實現;二、邏輯延遲所涉及到每個時鐘周期內遍歷的邏輯量;三、信號線延遲或布線延遲,如Vivado 如何高效實現設計的布局布線。

使用時序路徑或設計分析報告內的信息,有助于識別時序違例主要由哪些因素引發,以及確定如何迭代提升 QoR。

(提示:如果需要,可在每個步驟后打開 DCP 以生成更多報告,詳細流程請查看完整版指南。)

04

解決保持時間違例的方法

避免保持時間要求為正值

在使用多周期路徑約束放寬建立時間檢查時,需做到:

調整同一路徑上的保持時間檢查,以便在保持時間分析中使用相同的發送沿和捕獲沿。否則會導致保持時間要求(一個或多個時鐘周期)為正值,無法實序收斂。

指定端點管腳, 而不僅僅是單元或時鐘。例如, 端點單元REGB有三個輸入管腳:C、EN 和 D。只有 REGB/D 管腳需交由多周期路徑例外來約束(時鐘使能(EN)管腳不用),因為 EN 管腳在每個時鐘周期都會發生改變。如果將約束連接至單元而不是管腳,那么所有有效的端點管腳(包括 EN 管腳)都在約束的考慮范圍內。

在布線前降低 WHS 和 THS

嚴重的估算保持時間違例會增大布線難度, 且并非總能通過route_design解決。布局后phys_opt_design 命令提供多種保持時間修復選項:

在時序元件之間插入反向邊緣觸發寄存器會將時序路徑分為兩條半周期路徑,從而顯著減少保持時間違例。這種最優化只能在不劣化建立時序的情況下執行。

插入 LUT 1 緩沖器會導致數據路徑延遲, 這樣即可減少保持時間違例,而不會造成建立時間違例。

責任編輯:haq

-

Xilinx

+關注

關注

71文章

2167瀏覽量

121305 -

時序設計

+關注

關注

0文章

21瀏覽量

43927

原文標題:UltraFast 設計方法時序收斂參考指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用于Vivado設計套件的 UltraFast設計方法指南

了解最新的UltraFast設計方法竅門與技巧

全新嵌入式教程、更新的 UltraFast 方法指南,現已上線!

基于MCMM技術IC時序收斂的快速實現

一文知道UltraFast嵌入式設計方法指南

Vivado Design Suite設計套件的UltraFast設計方法的介紹

UltraFAST設計方法指南(適用于Vivado Design Suite)

UltraFast設計方法時序收斂快捷參考指南(UG1292)

UltraFAST設計方法指南(適用于Vivado Design Suite)

UltraFast設計方法時序收斂快捷參考指南

UltraFast設計方法時序收斂快捷參考指南

評論