Other Parts Discussed in Post:LMK03328, CDCM6208, CDCE949

在當(dāng)今世界上,大多數(shù)高度集成系統(tǒng)所執(zhí)行的功能均不止一項(xiàng),而且專為與其他系統(tǒng)和外設(shè)對接而設(shè)計(jì)。此外,還常常對同一個(gè)硬件進(jìn)行再配置以滿足不同地區(qū)或最終用戶的需要,從而減少設(shè)備制造商的庫存開銷金額。普通的最終用戶并不知道此類系統(tǒng)核心部分所發(fā)生的變化,包括負(fù)責(zé)控制終端設(shè)備功能的集成電路 (IC) 的操作模式。在本篇博客中,我將討論時(shí)鐘和定時(shí) IC 的一項(xiàng)重要特性,就是為高度集成系統(tǒng)提供“心跳”或基準(zhǔn)頻率。我喜歡把這項(xiàng)特性稱為“引腳可選的特質(zhì)”(pin selectable personality)。簡而言之,引腳可選的特質(zhì)是器件根據(jù)其外部控制引腳的狀態(tài)接納不同配置(特質(zhì))的能力。

在探究針對這些引腳可選特質(zhì)的潛在情形之前,我們來回顧一下能夠在計(jì)時(shí)器件中存儲(chǔ)上電復(fù)位 (POR) 配置的不同方法。采用外部控制引腳選擇的器件配置通常存儲(chǔ)在非易失性存儲(chǔ)器 (NVM) 中。最簡單的存儲(chǔ)器選項(xiàng)是掩模只讀存儲(chǔ)器 (ROM),它是一種其存儲(chǔ)內(nèi)容在集成電路 (IC) 制造過程中進(jìn)行硬編碼的 ROM。雖然掩模 ROM 的主要優(yōu)點(diǎn)是其可實(shí)現(xiàn)低成本的單位存儲(chǔ),但其一次性掩模成本卻很高。生成用以支持一種新配置的掩模 ROM 需要進(jìn)行 IC 再設(shè)計(jì)、制造、裝配和測試,而且常常不是一個(gè)快速過程。面對不斷發(fā)展變化的系統(tǒng)要求,產(chǎn)品設(shè)計(jì)周期必需加快。

第二種選項(xiàng)是一次性可編程 (OTP) NVM,其在 IC 制造之后僅進(jìn)行一次編程(通過在每個(gè)比特?zé)龜嗳劢z來完成)。與前文討論的掩模 ROM NVM 相比,配置這種形式的 NVM 常常較快。顧名思義,OTP NVM 只能進(jìn)行一次寫操作。系統(tǒng)原型設(shè)計(jì)期間的這一局限性有可能對項(xiàng)目進(jìn)度產(chǎn)生負(fù)面影響。

針對這些問題的一種精致解決方案以非易失性電可擦可編程 ROM (EEPROM) 的形式存在,它為在設(shè)計(jì)周期的原型設(shè)計(jì)階段快速試用不同配置提供了靈活性。EEPROM NVM 使計(jì)時(shí)器件能夠靈活地接納不同的引腳可選特質(zhì)。

圖 1 突出顯示了采用具集成型 EEPROM NVM 之計(jì)時(shí)解決方案的五項(xiàng)最重要的系統(tǒng)級優(yōu)勢。

圖1:具集成型EEPROM NVM之計(jì)時(shí)解決方案的系統(tǒng)級優(yōu)勢

下面,我將一一闡述圖 1 中所示的這五項(xiàng)優(yōu)勢:

1.利用多種時(shí)鐘方案以最大限度地縮減系統(tǒng)物料清單(BOM):在我和硬件設(shè)計(jì)人員的幾次交談中,他們表達(dá)了這樣一個(gè)愿望,即盡量減少從計(jì)時(shí)器件供應(yīng)商那里索取的 IC(供他們進(jìn)行選擇以證實(shí)具備在其系統(tǒng)中使用的品質(zhì))數(shù)量。

除此之外,他們各自公司內(nèi)部的不同產(chǎn)品線還具有各種各樣的計(jì)時(shí)要求(取決于終端設(shè)備)。計(jì)時(shí)器件提供了多個(gè)集成的 EEPROM NVM 頁面,這些頁面存儲(chǔ)了可容易地通過控制引腳搭接進(jìn)行訪問的獨(dú)特配置,有助于極大地削減系統(tǒng) BOM 并最大限度地縮短 IC 鑒定時(shí)間。

管理針對產(chǎn)品變種的要求:您的系統(tǒng)可能具有不同的操作模式。例如:在一種模式中,也許必需啟用通常被停用的處理器組以應(yīng)對激增的數(shù)據(jù)處理需求。在另一種模式中,或許需要關(guān)斷邏輯電路以盡量降低總體系統(tǒng)功耗。計(jì)時(shí)器件必須適應(yīng)這些操作模式及其配置(它們是不同 EEPROM 頁面能夠存儲(chǔ)的)。

滿足多種協(xié)議/平臺的需要:在廣播和專業(yè)視頻應(yīng)用中,針對諸如串行數(shù)字接口 (SDI)、高分辨率多媒體接口 (HDMI) 和 DisplayPort 等各種不同視頻標(biāo)準(zhǔn)的計(jì)時(shí)要求會(huì)有明顯的差別。地區(qū)標(biāo)準(zhǔn)規(guī)定了視頻基準(zhǔn)時(shí)鐘的頻率(對于基于逐行倒相 [PAL] 或美國國家電視系統(tǒng)委員會(huì) [NTSC] 制式的系統(tǒng)分別為 148.5 MHz 或 148.5/1.001 MHz)。特定于地區(qū)的頻率計(jì)劃可存儲(chǔ)在獨(dú)特的 EEPROM 頁面中,從而使得一款計(jì)時(shí) IC 能夠同時(shí)滿足多種平臺及協(xié)議的需要。

簡化系統(tǒng)原型設(shè)計(jì):頻率和 / 或抖動(dòng)裕度調(diào)節(jié)是在系統(tǒng)開發(fā)周期的工程驗(yàn)證測試 / 設(shè)計(jì)驗(yàn)證測試 (EVT/DVT) 階段中測試系統(tǒng)堅(jiān)固性和相符性的常用方法。在頻率裕度調(diào)節(jié)的場合中,采用一種迭代過程對系統(tǒng)開始發(fā)生故障時(shí)的頻率進(jìn)行測量。計(jì)時(shí)器件上的 EEPROM 頁面能夠存儲(chǔ)標(biāo)稱頻率的頻率變種(偏離標(biāo)稱值的范圍從幾 Hz 至幾 MHz),其可通過控制引腳來選擇。擁有必要的連接程序以在計(jì)時(shí)器件中執(zhí)行頻率裕度調(diào)節(jié)測試,可幫助簡化原型設(shè)計(jì)和驗(yàn)證。

確保您的系統(tǒng)適用于未來:未用的 EEPROM 頁面可用作未來配置的預(yù)留位置。當(dāng)該是升級系統(tǒng)的時(shí)候,您不必為鑒定一款新的計(jì)時(shí)器件而犯愁。

現(xiàn)在,我們來考察一種實(shí)際應(yīng)用情形,一款具集成型 EEPROM NVM 的時(shí)鐘發(fā)生器 IC 可在此場合中提供上文著重闡述的系統(tǒng)優(yōu)勢:

表 1 列出了針對 LMK03328 超高性能時(shí)鐘發(fā)生器的一種 EEPROM 配置方案。如該表所示,計(jì)時(shí)器件上的引腳搭接 GPIO2 和 GPIO3 引腳能夠選擇特定于地區(qū)的視頻頻率、中央處理單元 (CPU) 和以太網(wǎng)時(shí)鐘。另外,該表還突出顯示了可對 CPU 時(shí)鐘頻率進(jìn)行 ±5% 裕度調(diào)節(jié)的配置。

| EEPROM 頁面 | 頁面 0 | 頁面 1 | 頁面 2 | 頁面 3 | 頁面 4 | 頁面 5 |

| GPIO3 | 低 | 低 | 低 | 高 | 高 | 高 |

| GPIO2 | 低 | 中等 | 高 | 低 | 中等 | 高 |

| PLL1 VCO | 5 GHz | 5 GHz | 5 GHz | 5 GHz | 5 GHz | 5.346/1.001 GHz |

| PLL2 VCO | 5.346 GHz | 5.346 GHz | 5.346/1.001 GHz | 5.346 GHz | 5.346 GHz | 5.346 GHz |

| OUT0 | 297 MHz | 297 MHz | 297/1.001 MHz | 148.5 MHz | 297 MHz | 297 MHz |

| OUT3 | 125 MHz | 125 MHz | 125 MHz | 125 MHz | 125 MHz | 停用 |

| OUT4 | 156.25 MHz | 156.25 MHz | 156.25 MHz | 156.25 MHz | 156.25 MHz | 297/1.001 MHz |

| OUT7 | 100 MHz | 100 MHz | 100 MHz | 100 MHz | 100 MHz | 停用 |

| OUT1、2、5、6 | 停用 | 停用 | 停用 | 停用 | 停用 | 停用 |

| STAT0/CLK | 66.6 MHz |

69.4 MHz (+5% 裕度調(diào)節(jié)) |

66.6 MHz | 66.6 MHz |

62.5 MHz (-5% 裕度調(diào)節(jié)) |

停用 |

表1:采用LMK03328的引腳可選時(shí)鐘配置

我希望自己激發(fā)了大家對于具有掩模 ROM 和集成型 EEPROM NVM、并提供了成本效益和靈活性的計(jì)時(shí)器件的一些好奇心。我最喜歡的高性能時(shí)鐘發(fā)生器是 LMK03328。其他受歡迎的選擇是 CDCM6208 和 CDCE949。

審核編輯:何安

-

模擬

+關(guān)注

關(guān)注

7文章

1438瀏覽量

84568

發(fā)布評論請先 登錄

蔚來榮獲五項(xiàng)國際權(quán)威大獎(jiǎng)

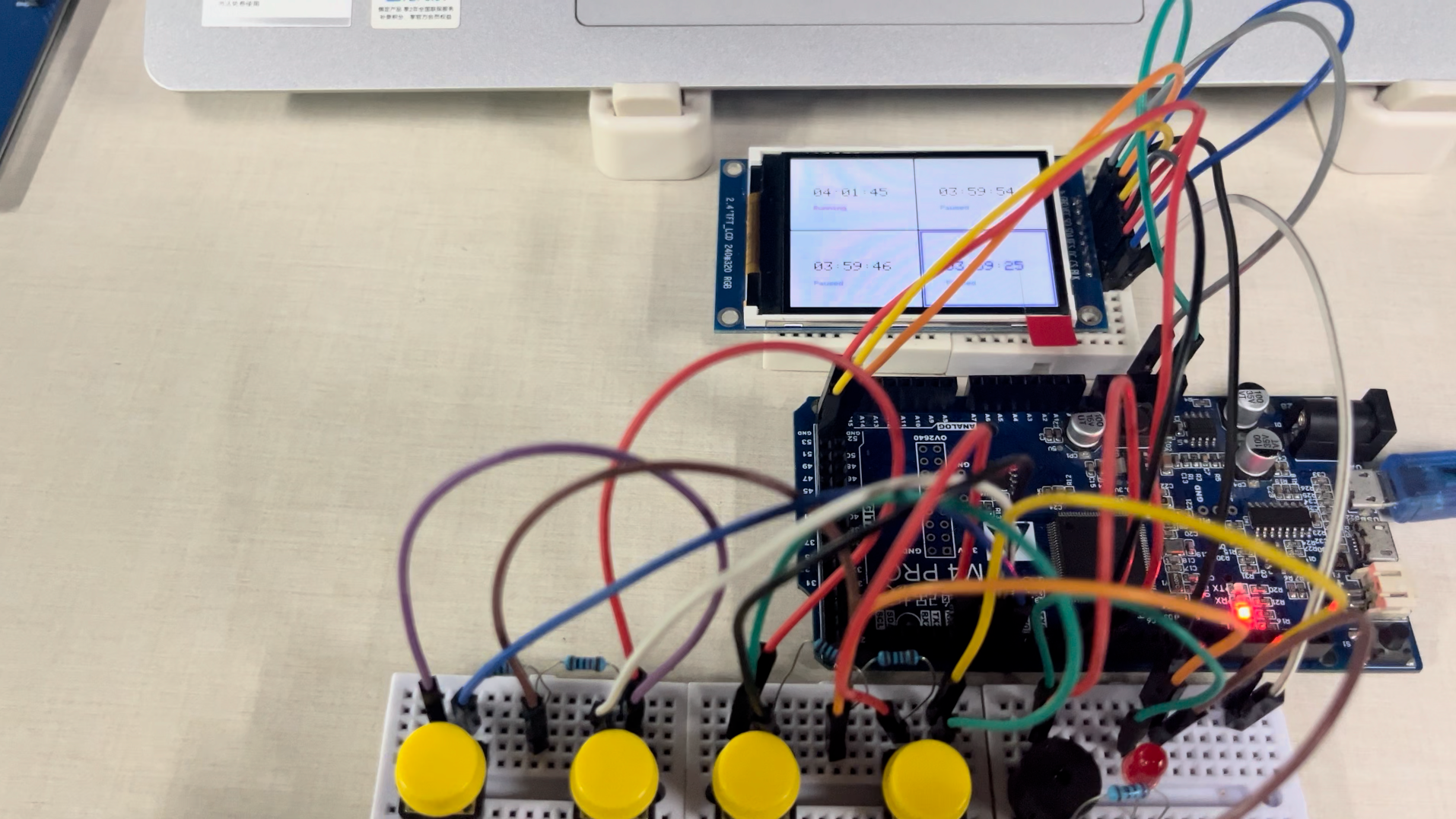

零知開源——基于STM32F407VET6零知增強(qiáng)板的四路獨(dú)立計(jì)時(shí)器

基于STM32F407VET6零知增強(qiáng)板的四路獨(dú)立計(jì)時(shí)器

華為榮獲GTI Awards 2025五項(xiàng)大獎(jiǎng)

喜報(bào)!經(jīng)緯恒潤五項(xiàng)產(chǎn)品榮獲國家級認(rèn)證

喜報(bào)!經(jīng)緯恒潤五項(xiàng)產(chǎn)品榮獲國家級認(rèn)證

EE-109:ADSP2106x:使用2106x SPORT作為計(jì)時(shí)器

浪潮信息AS13000G7榮獲MLPerf? AI存儲(chǔ)基準(zhǔn)測試五項(xiàng)性能全球第一

單個(gè) MSP430? 計(jì)時(shí)器模塊的多時(shí)基應(yīng)用說明

MSPM0-高級控制計(jì)時(shí)器有助于實(shí)現(xiàn)更好的控制和更好的數(shù)字輸出

用于電源門控的TPL5110毫微功耗系統(tǒng)計(jì)時(shí)器數(shù)據(jù)表

TLC555-Q1 LinCMOS?計(jì)時(shí)器數(shù)據(jù)表

TLC555 LinCMOS?技術(shù)計(jì)時(shí)器數(shù)據(jù)表

LMC555 CMOS計(jì)時(shí)器數(shù)據(jù)表

評論