在為下一代服務器和交換機實現從10G到25G系統的轉換時,硬件設計工程師們必須滿足以下這些互相抵觸和矛盾的目標:盡可能降低數據延遲、保持或減小功耗、以及盡可能地降低成本。為了用具有競爭力的成本優勢為數據中心用戶提供世界一流的產品,從根本上來說,你必須少花錢多辦事。

以下是5個快速小竅門,它能使你在設計25G系統時做出很好的平衡:

1.確定系統中的哪條鏈路將會需要信號調節;這將取決于走線長度和印刷電路板 (PCB) 材質。低損耗材料需要較少的信號調節,不過它們的價格也比標準材料要貴。損耗大于專門用途集成電路 (ASIC) 的內在補償功能的通道將需要某種形式的信號調節。例如,如果你的ASIC能夠實現30dB的補償,你就有可能希望為損耗達到27dB或以上的通道增加信號調節,而其中的3dB差異可以作為安全裕量。

圖1是一個PCB材料A和B之間的通道損耗預算分析比較示例圖。

2.對于那些需要信號調節的通道,用小型封裝實現設計靈活性。小型封裝提供高通道密度,并且使你能夠使用重定時器或引腳兼容中繼器。

3.設計一個適應重定時器或中繼器需要的電源解決方案。例如,TPS53513同步降壓轉換器能夠提供8A電流,已足夠一組6個重定時器或中繼器的用電需要。

4.確定SMBus尋址機制,這個機制需要對電路板上的每個重定時器/中繼器器件進行單獨尋址。你可以用16個唯一SMBus地址中的一個來對每個器件進行引腳配置。如果一塊電路板上有超過16個器件,可以考慮使用一個諸如TCA/PCA系列I2C/SMBus開關的I2C擴展器來將這個SMBus分為多個總線。

5.在電路板上放置一個單個低成本25MHz (±100ppm) 2.5V單端時鐘,以支持多達20個重定時器器件。由于它不用于恢復數據,所以這個時鐘不具有任何抖動需要。這個重定時器將接受時鐘計時,對其進行緩沖,并且將其復制在一個輸出引腳上,以便輕松連接到下一個重定時器。無需用到多個晶振或扇出緩沖器。如果你最終決定使用中繼器,而不是重定時器的話,那么你可以選擇不組裝這個組件來降低成本。

為了使以上這些技巧在實現起來更加簡單,TI已經引入了業內首款引腳兼容中繼器 (DS280BR810) 和重定時器 (DS250DF810) 解決方案產品組合,以實現25G背板和前端口應用。而這些是如何幫助實現功耗、性能和價格之間的平衡呢?這一切都與設計簡便性和靈活性相關。

TI的引腳兼容中繼器和重定時器解決方案使你能夠在盡可能減小延遲和降低物料清單 (BOM) 成本的同時,選擇一款滿足你性能目標的解決方案。硬件工程師知道,周圍元件的成本、尺寸和復雜度與中繼器或重定時器本身同樣重要。可以考慮一下圖2中的電路板設計示例。

TI的25G DS280BR810中繼器和DS250DF810重定時器解決方案的引腳兼容屬性使你能夠生成一個電路原理圖,以評估這兩個選項,從而實現針對最終產品的成本、功耗、和性能優化。信號完整性工程師們能夠用中繼器解決方案來開始測試,這個解決方案提供更低成本和功耗。如果系統中的抖動和串擾需要更高性能,那么它們可以升級到一個引腳兼容重定時器解決方案。

小物件真的具有大作用。可以想象一個常見的、有20000臺服務器的數據中心。使用中繼器,而不使用重定時器能夠使一個服務器網絡接口卡 (NIC) 節省大約1W的功耗,累加在一起每年節省的電費超過21000美元(每度電0.12美元),這其中還不包括所節省的冷卻方面的開銷。如果你將BOM的元件成本減少5美元,就能多節省100000美元。最后,50ns延遲與500ps延遲之間的差異在于,滿足整個數據中心服務請求的同時,每天會“浪費”8個小時的時間(假定每秒有2000個請求,每天每臺服務器的總使用時間為4小時)。

通過使用以上這些技巧,你應該能夠設計出一款在成本、功耗和性能之間做出很好均衡的電路板。

審核編輯:何安

-

模擬

+關注

關注

7文章

1422瀏覽量

83921

發布評論請先 登錄

相關推薦

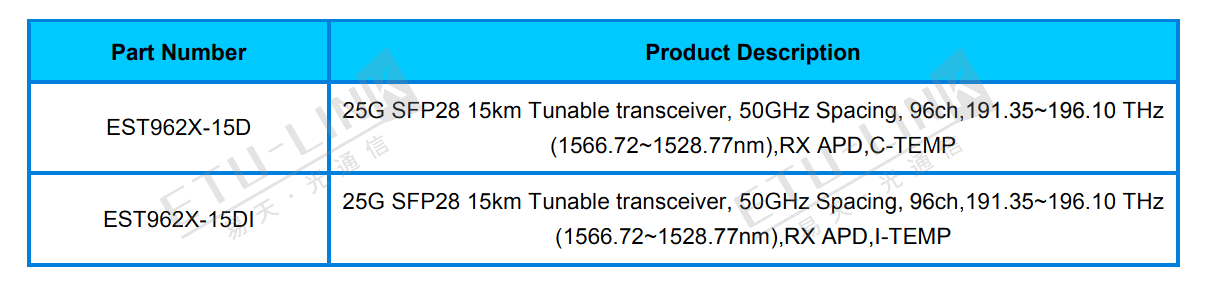

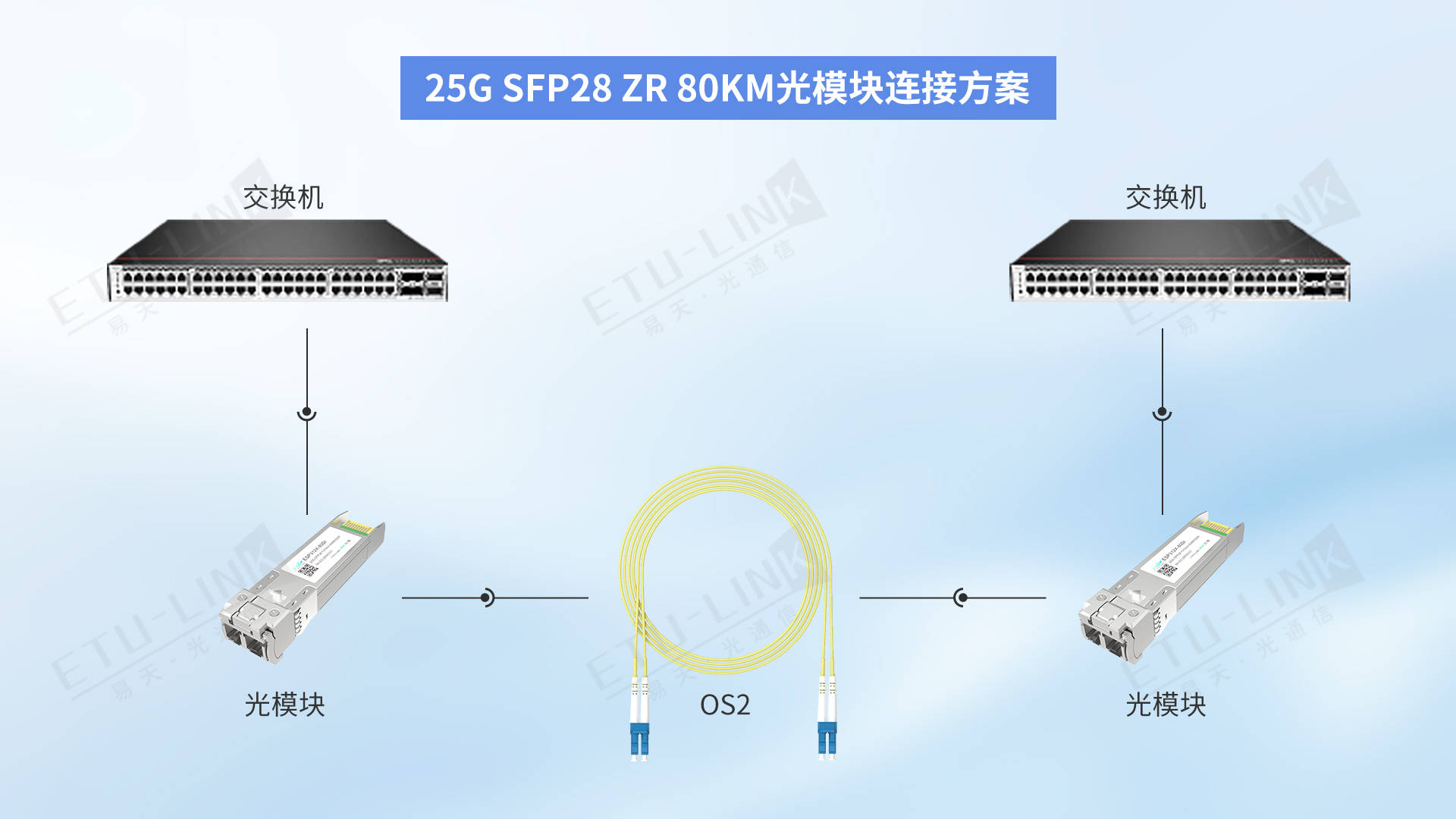

易飛揚25G SFP28 ZR傳輸模塊介紹

易飛揚25G SFP28 ZR,突破25G傳輸距離

25W氮化鎵快充芯片U8723AH合理平衡工作頻率問題

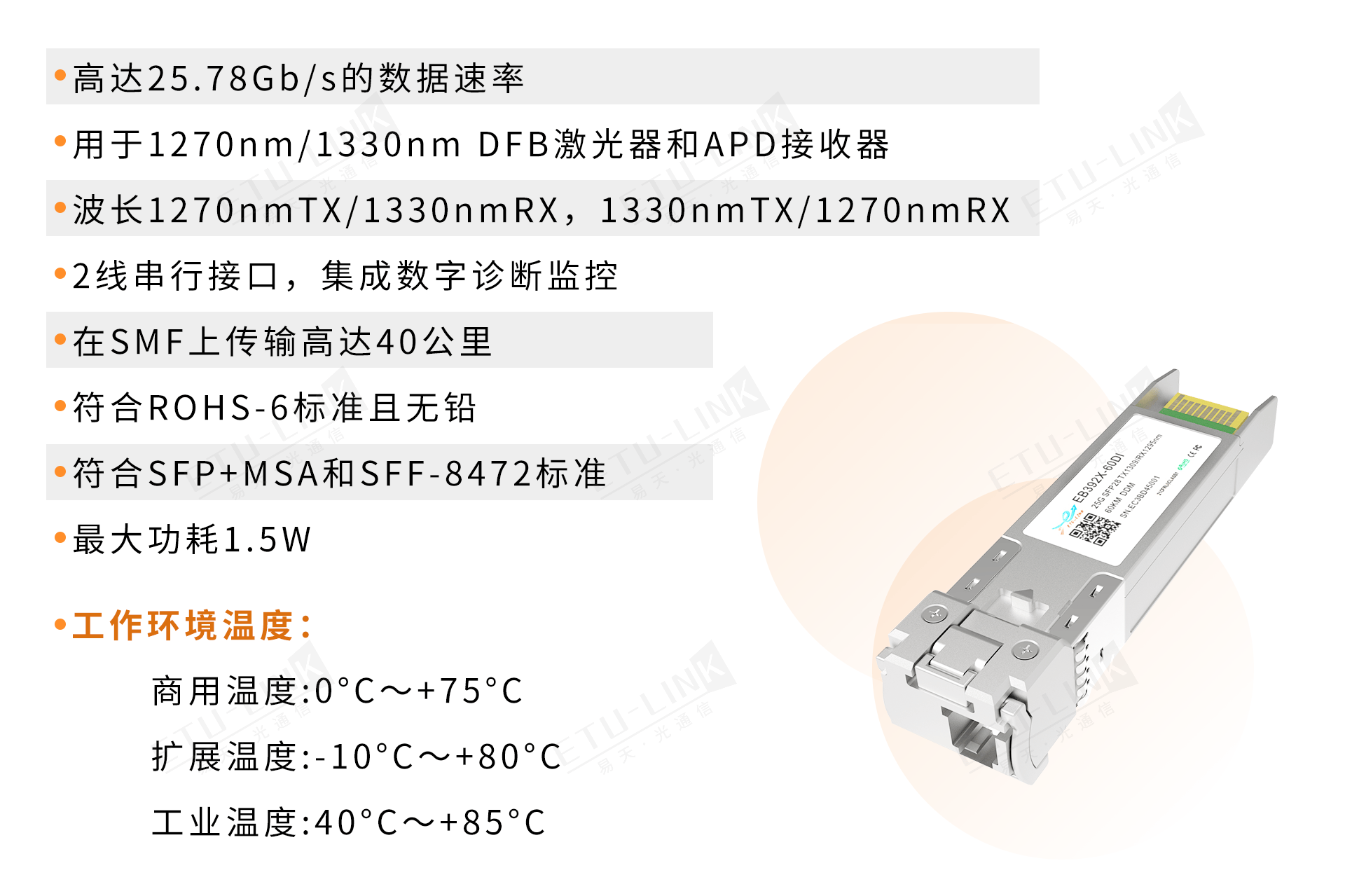

25G SFP28 BIDI光模塊介紹

明明我說的是25G信號,你卻讓我看12.5G的損耗?

明明我說的是25G信號,你卻讓我看12.5G的損耗?

25G/28G重定時器與轉接驅動器在常見應用中的最優化實現

新品發布 rBT3250-50G突發誤碼分析儀,支持突發和連續模式信號輸出及誤碼測試

5G以太網和5G前傳業務的有效解決方案——25G可調DWDM光模塊

光模塊25G SFP28 SR和LR有什么區別?

5G前傳光纖傳輸的25G光模塊晶振SG2016CAN

25G BIDI SFP28單纖光模塊分類及應用解析

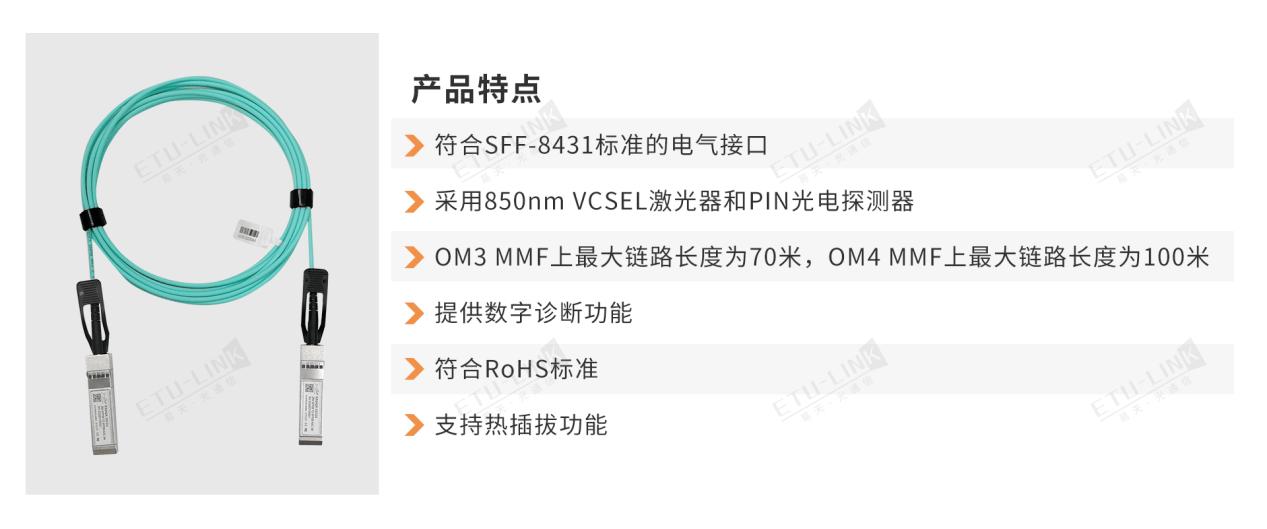

25G SFP28 AOC線纜最新數據傳輸解決方案

從百兆到百G,DWDM光模塊的演進

如何在設計25G系統時做出很好的平衡

如何在設計25G系統時做出很好的平衡

評論