作者:Julian Hagedorn

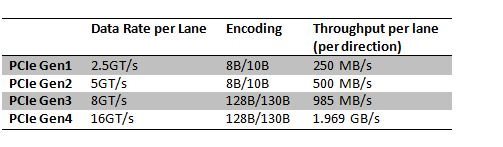

PCI Express? (PCIe?) 是一項(xiàng)業(yè)界領(lǐng)先的標(biāo)準(zhǔn)輸入/輸出 (I/O) 技術(shù),是服務(wù)器、個(gè)人電腦以及其它應(yīng)用中最常用的 I/O 接口之一。該標(biāo)準(zhǔn)多年來不斷發(fā)展,以適應(yīng)更高的數(shù)據(jù)速率(見表 1)。第 3 代 PCIe 引入了全新的編碼方案,其可在不增加數(shù)據(jù)速率一倍的情況下,將數(shù)據(jù)吞吐量提升一倍。PCI-SIG 近期宣布推出的第 4 代 PCIe 具有 16 G 每秒傳輸 (GT/s) 的比特率。第 4 代的規(guī)范預(yù)計(jì)將在 2014 或 2015 年發(fā)布。

表 1:各代 PCIe 的數(shù)據(jù)吞吐量

隨著數(shù)據(jù)速率的提升,參考時(shí)鐘需求也在不斷提高。本文將重點(diǎn)介紹參考時(shí)鐘需求。

PCIe 參考時(shí)鐘 (RefClk) 規(guī)范可針對(duì) 3 種不同架構(gòu)定義,分別是:數(shù)據(jù)時(shí)鐘、獨(dú)立 RefClk 以及通用 RefClk。每個(gè)架構(gòu)都具有特定的濾波器函數(shù)。在接收器時(shí)鐘數(shù)據(jù)恢復(fù)輸入端出現(xiàn)的有效抖動(dòng)是接收器及發(fā)送器 PLL 帶寬與 RefClk 抖動(dòng)頻譜所涉及峰值之差的函數(shù)。此外,它還取決于 RefClk 架構(gòu)。

在獨(dú)立 RefClk 架構(gòu)中,發(fā)送器 (TX) 與接收器 (RX) 都可接收獨(dú)立的 RefClk。這會(huì)導(dǎo)致嚴(yán)格的抖動(dòng)需求,而且不能應(yīng)用擴(kuò)展頻譜時(shí)鐘 (SSC)。

在數(shù)據(jù)時(shí)鐘架構(gòu)中,單個(gè) RefClk 可連接至發(fā)送器,而接收器則使用來自數(shù)據(jù)流的嵌入式時(shí)鐘信號(hào)。時(shí)鐘數(shù)據(jù)恢復(fù) (CDR) 電路可提取數(shù)據(jù)流中的時(shí)鐘。它最大限度地緩解了抖動(dòng)要求,而且也可應(yīng)用 SSC。但是,這是一種相對(duì)較新的標(biāo)準(zhǔn),很多器件都不支持。

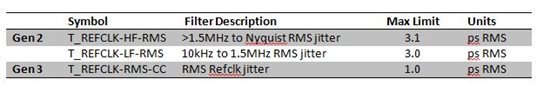

最佳備選標(biāo)準(zhǔn)(也是最常用的標(biāo)準(zhǔn))是通用 RefClk 架構(gòu)。它不僅可向發(fā)送器與接收器提供相同的 RefClk,而且還支持可減少電磁干擾 (EMI) 的 SSC,其實(shí)施非常便捷。這種架構(gòu)的缺點(diǎn)是 RefClk 需要滿足不足 12ns 的偏移需求。下列是通用 RefClk 架構(gòu)及其應(yīng)用實(shí)例。

表 2:應(yīng)用濾波器函數(shù)后的通用 RefClk 抖動(dòng)規(guī)范

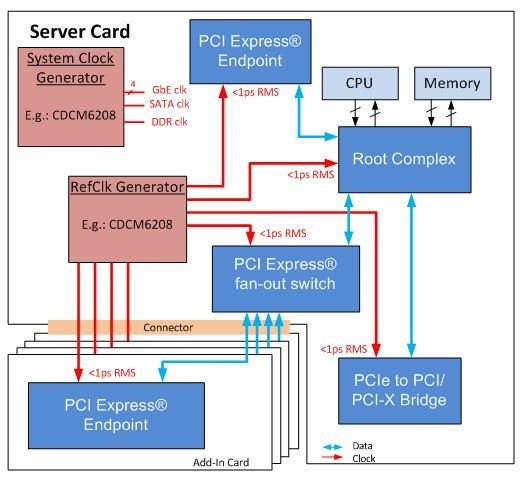

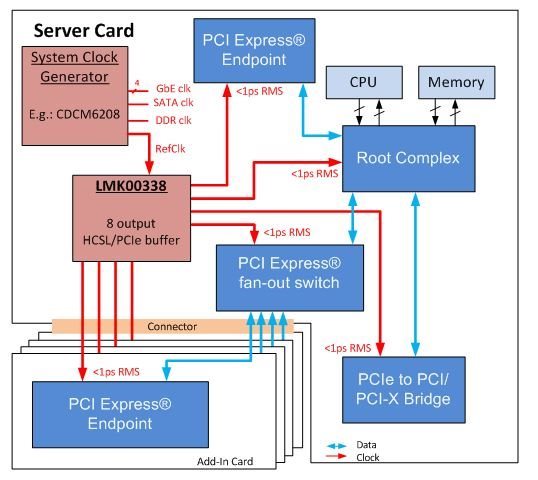

服務(wù)器卡等通用 PCIe 應(yīng)用包含幾個(gè)構(gòu)建塊。系統(tǒng)的核心是根聯(lián)合體,其代表 I/O 系統(tǒng)的根。根聯(lián)合體連接 CPU 和存儲(chǔ)器,可能具有多個(gè) PCIe 端口。此外,它還包含開關(guān)和 PCIe 端點(diǎn)(例如顯卡)。I/O 系統(tǒng)的所有組件都要符合發(fā)送器/接收器與 RefClk 的抖動(dòng)要求。如果所有構(gòu)建塊都兼容于第 3 代 PCIe,那么都要達(dá)到 1ps rms 的 RefClk 要求(圖 1)。

圖 1:解決方案 1:支持第 3 代 PCIe 通用 RefClk 抖動(dòng)限制的服務(wù)器卡實(shí)例

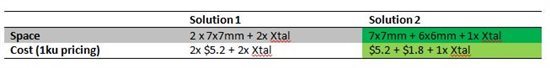

圖 1 所示系統(tǒng)可使用一個(gè) 7 輸出時(shí)鐘生成器實(shí)現(xiàn)。這種實(shí)施方案最終可能需要一個(gè)以上基于時(shí)鐘生成器的時(shí)鐘樹解決方案,因?yàn)檫€需要生成其它系統(tǒng)時(shí)鐘。系統(tǒng)時(shí)鐘生成器可為千兆位以太網(wǎng)器件、SATA 控制器、DDR 時(shí)鐘等生成參考時(shí)鐘。在圖 2 中,RefClk 生成器由時(shí)鐘緩沖器取代。這不僅可簡(jiǎn)化時(shí)鐘樹,而且還可提供成本更低、空間更優(yōu)化的解決方案。

表 3:解決方案 1 與解決方案 2 以及空間與成本的對(duì)比

圖 2:解決方案 2:使用 LMK00338 等 RefClk 緩沖器的服務(wù)器卡實(shí)例

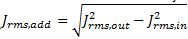

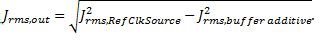

在使用緩沖器分配 RefClk 時(shí),需要考慮緩沖器引起的附加抖動(dòng)。附加抖動(dòng)的定義是器件本身對(duì)輸入信號(hào)產(chǎn)生的額外抖動(dòng)量,計(jì)算方法是: 。

。

假設(shè)噪聲過程是隨機(jī)的,而且輸入噪聲與輸出噪聲無關(guān)。緩沖器的抖動(dòng)輸出可通過該公式計(jì)算: 。

。

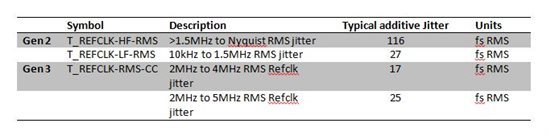

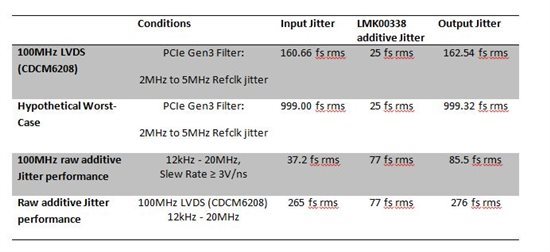

LMK00338 是一款超低附加抖動(dòng) PCIe 時(shí)鐘緩沖器。對(duì)于第 3 代 PCIe 應(yīng)用而言,一般具有 30fs rms 的附加抖動(dòng)。表 3 是應(yīng)用不同 PCIe 濾波器函數(shù)時(shí)的附加抖動(dòng)性能。

表 4:LMK00338 的附加抖動(dòng)性能

CDCM6208 等第 3 代 PCIe 高性能時(shí)鐘生成器可提供具有 160.66fs rms 抖動(dòng)(2MHz 至 5MHz 濾波器)的 RefClk。如果對(duì)該時(shí)鐘進(jìn)行分配,LMK00338 會(huì)向 RefClk 信號(hào)增加 25fs rms 的抖動(dòng)。使用以上計(jì)算公式計(jì)算出的輸出抖動(dòng)僅為 162.54 fs rms(表 5)。在最壞的情況下,RefClk 生成器可能具有 999fs rms 的抖動(dòng),使用 LMK00338 不會(huì)超出第 3 代 PCIe 的抖動(dòng)限值。

表 5 是未應(yīng)用 PCIe 濾波器函數(shù)時(shí) LMK00338 的附加抖動(dòng)性能。由于具有 77 fs rms 的低附加抖動(dòng)(集成帶寬:12kHz 至 20MHz),因此該緩沖器適用于大部分使用 HCSL 信號(hào)傳輸技術(shù)的高性能時(shí)鐘應(yīng)用。另外還提供更小的 4 輸出版本。

表 5:低抖動(dòng) RefClk 源 (CDCM6208) 驅(qū)動(dòng)的時(shí)鐘緩沖器的效果。

多個(gè)服務(wù)器卡中存在的共同問題是電源噪聲問題。噪聲可能來自多個(gè)噪聲源,首先是開關(guān)電源,以及 CPU、ASIC 或 FPGA 等數(shù)字電路。電源旁路將幫助過濾掉其中一部分噪聲,而剩下的噪聲則將影響器件性能。在剩余噪聲影響時(shí)鐘分配器件電源時(shí),會(huì)導(dǎo)致窄帶相位調(diào)制以及時(shí)鐘輸出的幅度調(diào)制。

在 100kHz 至 10MHz 的噪聲頻率范圍內(nèi),LMK00338 可在 100MHz 輸出頻率下表現(xiàn)出低于 -75dBc 的優(yōu)異電源紋波抑制 (PSRR) 特性。這種噪聲抗擾度將幫助簡(jiǎn)化電源旁路,是 LMK00338 的另一大重要優(yōu)勢(shì)。

以上分析表明,只要 RefClk 生成器符合抖動(dòng)要求,就可以放心大膽地在通用 RefClk 系統(tǒng)中使用超低附加抖動(dòng)時(shí)鐘緩沖器。

此外,LMK00338 的通用輸入級(jí)不僅可接收任何差分或單端信號(hào),而且還可將其轉(zhuǎn)換為 8 HCSL 輸出。對(duì)于第 4 代 PCIe 而言,最大 RefClk 抖動(dòng)可假定為遠(yuǎn)遠(yuǎn)小于 1ps rms。因此,支持緩沖的通用 RefClk 架構(gòu)將更適合更嚴(yán)格的較新 PCIe 標(biāo)準(zhǔn)。

如欲了解有關(guān)時(shí)鐘產(chǎn)品的更多詳情,敬請(qǐng)查看時(shí)鐘及定時(shí)解決方案指南。

原文請(qǐng)參見: http://e2e.ti.com/blogs_/b/analogwire/archive/2014/03/28/how-to-optimize-clock-distribution-in-pcie-applications.aspx

編輯:jq

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7067瀏覽量

89131 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9206瀏覽量

85564 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1735瀏覽量

131543 -

PCIe

+關(guān)注

關(guān)注

15文章

1241瀏覽量

82733

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在主板上優(yōu)化PCIe通道設(shè)置

CDC509/516/2509/2510/2516的高速時(shí)鐘分配設(shè)計(jì)技術(shù)

TCAN455x時(shí)鐘優(yōu)化和設(shè)計(jì)指南

DHCP分配IP地址,助力企業(yè)優(yōu)化管理

PCIe應(yīng)用的時(shí)鐘

AN-1926:M-LVDS簡(jiǎn)介及其時(shí)鐘和數(shù)據(jù)分配應(yīng)用

CDCE18005高性能時(shí)鐘分配器數(shù)據(jù)表

CDCE62005高性能時(shí)鐘發(fā)生器和分配器數(shù)據(jù)表

CDCE72010十路輸出高性能時(shí)鐘同步器、抖動(dòng)消除器和時(shí)鐘分配器數(shù)據(jù)表

pcie4.0和pcie3.0接口兼容嗎

FPGA的PCIE接口應(yīng)用需要注意哪些問題

FPGA開發(fā)過程中配置全局時(shí)鐘需要注意哪些問題

6678通過pcie進(jìn)行boot時(shí),PC無法寫bar空間

核芯互聯(lián)推出支持PCIe Gen 6的時(shí)鐘發(fā)生器CLG440

如何優(yōu)化PCIe應(yīng)用中的時(shí)鐘分配

如何優(yōu)化PCIe應(yīng)用中的時(shí)鐘分配

評(píng)論