傳統 I2S—為何要包括系統時鐘?

過去,我們在討論音頻話題時,偶爾會提及 I2S。我在以前的一些文章中提到過 I2S,其他人在做音頻研究時也都會提到它。簡而言之,它是一種將立體聲數據從一端傳輸至另一端的同步方法。

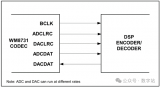

大多數人認為 I2S 有三種信號:

數據:輸入或者輸出數據

位時鐘 (Bitclock,BCK):確立數據流中兩個相鄰位之間邊界的信號

左/右時鐘 (LRCK)/字時鐘 (Wordclock):一個在采樣速率下運行、占空比為 50% 的慢時鐘,它確立數據流中兩條相鄰通道(左和右)之間的邊界。

I2S 的幕后英雄是主時鐘 (MCK),也稱作系統時鐘 (SCK),它常常被數字信號處理器 (DSP) 程序員和其他處理器愛好者們忽略。主時鐘 (MCK/SCK),通常為一個64、128、256 和 512 倍采樣速率 (FS) 的時鐘。它可以由一個輸入引腳直接提供,也可以通過一個鎖相環路 (PLL) 在某些器件內部產生。

一般而言,DSP 不需要音頻主時鐘,因為它們能夠以一種完全不同的速率對數據進行處理,然后在 BCK 和 LRCK 的驅動下,讓數據以某種速率進入輸出緩沖器(或者通過輸入緩沖器接收數據)。

如果您能暫時將注意力從您的處理器上移開,您會發現音頻主時鐘重要得多。大多數 MCK/SCK 輸入的音頻轉換器,都要求時鐘同步,而有一些則允許異相位。這就意味著,它們需要由相同的高速時鐘來提供,然后被除小。我接觸過的一些客戶會突發靈感地告訴我:“我的 ADC 需要一個 MCK,但它離我的 DAC 太遠。因此,我要在每個轉換器旁邊放置一個晶體……”有這種想法可以理解,但請您“千萬別這么做!”

您在購買晶體時,無法保證它剛好為 48.000 kHz。您的模數轉換器 (ADC) 晶體的運行精確度可能會為 +5%,而數模轉換器 (DAC) 的運行精確度可能為 –5%。這樣的精確度,會給您的設計帶來災難性的后果!這是為什么呢,下面將為您娓娓道來。

用于 I2S

用于音頻 ADC 的主時鐘

如圖 1 所示,高速主時鐘(例如:24.576 MHz 時鐘)用于驅動 ADC 的過采樣調制器。之后,來自過采樣調制器的數據被消減分解成 LRCK 給定的采樣速率。

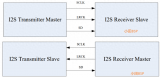

當 ADC 運行在主模式(生成 BCK 和 LRCK,作為輸出)下時,ADC 只是對 MCK/SCK 進行劃分,產生 LRCK 和 BCK 信號。這就對啦!LRCK/BCK 和主時鐘被同步—相位也可能同步(除非它是一個特殊分割器)。

如果作為一個從器件,并且主時鐘不同步,則它產生的數據會過多或者過少,以至于數字抽取器無法剛好適合于輸出字。在這種條件下,許多 ADC 會拒絕流傳輸數據。

DAC 也是如此。圖 2 顯示了一個高級 DAC 結構圖。此處,需要通過 MCK/SCK 運行內插器,而 MCK/SCK 同時還驅動 △∑ 調制器。如果 MCK/SCK 不是采樣速率的整倍數 (64/128/256/512),則在 △∑ 調制器輸出端可能會出現錯誤數據。

我在哪里/如何生成 MCK/SCK 呢?

在當今的工業應用中,CMOS 振蕩器由許多晶體振蕩器支持,并緊靠這些晶體振蕩器。它們都擁有非常好的精確度和較低的抖動。偶爾會用到壓控振蕩器(VCO),但它們會受到其輸出抖動的困擾。

許多現代的音頻轉換器現在都集成了一個 PLL,以通過慢 BCK 產生 MCK。這樣做很有效。但是,您應該注意,使用 PLL 時始終都會有產生抖動的可能,從而降低了音頻性能。

另外,我建議,如果在晶體源驅動 ADC 或是 DAC 兩者之間選擇,請您選擇通過一個晶體產生源來運行 ADC。如果輸入很糟糕,那么您做什么都于事無補!(就像您不可能把爛泥打磨光亮!)

因此,我的建議遵循的原則是:

1、如果轉換器為一個 I2S 從器件,則您必須通過相同源(如果轉換器帶有,則可以依靠內部 PLL),提供所有三個 I2S 時鐘(MCK、BCK 和 LRCK)。

2、如果轉換器為一個 I2S 主器件,則請確定能夠提供一個可靠的無抖動 MCK源。然后,讓轉換器自己分配。在可能的情況下,讓 ADC 通過一個可靠的低抖動 MCK 源在主模式下運行。這樣做可以確保最低抖動和最小高頻失真。

責任編輯:haq

-

振蕩器

+關注

關注

28文章

3832瀏覽量

139038 -

adc

+關注

關注

98文章

6495瀏覽量

544467 -

模擬

+關注

關注

7文章

1422瀏覽量

83921

發布評論請先 登錄

相關推薦

詳解I2S時序

傳統I2S—為何要包括系統時鐘

傳統I2S—為何要包括系統時鐘

評論