工程師們喜歡通過多種方法簡化設(shè)計(jì)流程。我最喜歡的是一直采用低阻抗電源驅(qū)動(dòng)模數(shù)轉(zhuǎn)換器 (ADC) 輸入。為什么我會(huì)對這種方法情有獨(dú)鐘?因?yàn)樗蔀榫_數(shù)據(jù)采集模塊帶來諸多優(yōu)勢。

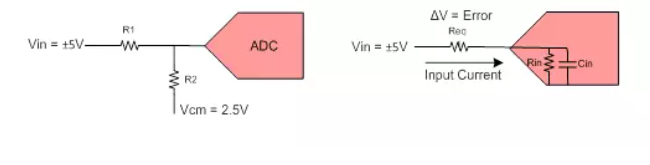

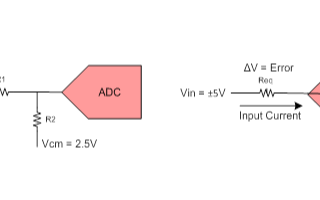

我們首先來看一種常見應(yīng)用,其中需要將高電壓信號源進(jìn)行電平轉(zhuǎn)換,將其轉(zhuǎn)換為所需的 ADC 輸入范圍。圖 1 中的簡單分壓器可用來解決該問題,即將 +/-5V 信號電平轉(zhuǎn)換為 0-5V。該分壓器的等效阻抗 Req 等于 R1 與 R2 的并行結(jié)合。

那么,這種有限電源阻抗會(huì)如何影響數(shù)據(jù)采集系統(tǒng)?

圖 1

高電源阻抗會(huì)在數(shù)據(jù)采集過程中產(chǎn)生線性和非線性錯(cuò)誤。導(dǎo)致數(shù)據(jù)采集系統(tǒng)低 SNR 及 THD 性能的主要錯(cuò)誤包括:

增益錯(cuò)誤:ADC 輸入端的電源阻抗與 ADC 的輸入阻抗構(gòu)成分壓器。電源阻抗中的這種輸入壓降會(huì)產(chǎn)生測量過程中的增益錯(cuò)誤。保持低電源阻抗有助于將這種系統(tǒng)錯(cuò)誤保持在較低水平;

趨穩(wěn)時(shí)間錯(cuò)誤:要實(shí)現(xiàn)精確轉(zhuǎn)換,需要在數(shù)據(jù)轉(zhuǎn)換器的有效采集時(shí)間內(nèi)對 ADC 輸入進(jìn)行穩(wěn)固。ADC 內(nèi)部的采樣電容器只允許在該采集時(shí)間內(nèi)充電。ADC 輸入端的電源阻抗能夠與 ADC 的輸入電容器一起創(chuàng)建更多時(shí)間常數(shù)。因此,低通濾波器會(huì)因趨穩(wěn)錯(cuò)誤在采樣信號中產(chǎn)生錯(cuò)誤;

失真:以上提到的由電源阻抗及輸入電容產(chǎn)生的低通濾波器問題還會(huì)在轉(zhuǎn)換過程中造成與信號有關(guān)的失真。該失真源于電容器所固有的非線性,這主要取決于其所存儲的電壓情況。用來采樣輸入信號的輸入電流會(huì)在電源阻抗中產(chǎn)生錯(cuò)誤電壓。對于正弦波輸入信號來說,該錯(cuò)誤不但包含諧波,而且還可加重系統(tǒng)失真。

當(dāng)驅(qū)動(dòng)高精度數(shù)據(jù)采集系統(tǒng)中的 ADC 輸入時(shí),電源阻抗的影響會(huì)非常明顯。

如欲希望獲得如何驅(qū)動(dòng) ADC 輸入的更多建議,敬請查看 TI 高精度設(shè)計(jì),其所提供的技術(shù)可為您的 ADC 實(shí)現(xiàn)最高性能:最低失真、最低噪聲的 18 位 1MSPS 最優(yōu)化數(shù)據(jù)采集參考設(shè)計(jì)。

-

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7259瀏覽量

92010 -

adc

+關(guān)注

關(guān)注

99文章

6714瀏覽量

549424 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3366瀏覽量

128313

發(fā)布評論請先 登錄

數(shù)據(jù)采集與傳輸系統(tǒng)設(shè)計(jì)

基于USB總線的高速數(shù)據(jù)采集系統(tǒng)

基于USB數(shù)據(jù)采集系統(tǒng)的研究與設(shè)計(jì)--ResearchandDesignofDataAequisitio

基于GPRS遠(yuǎn)程數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

工業(yè)能源采集及監(jiān)管系統(tǒng)的數(shù)據(jù)采集及傳輸方案

數(shù)據(jù)采集系統(tǒng)

驅(qū)動(dòng)ADC輸入時(shí)簡化設(shè)計(jì)流程的方法

如何采用數(shù)據(jù)采集卡設(shè)計(jì)測井數(shù)據(jù)采集控制系統(tǒng)?

請問數(shù)據(jù)采集系統(tǒng)該如何去設(shè)計(jì)?

數(shù)據(jù)采集系統(tǒng)具有的功能是什么

基于聲卡的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

8通道數(shù)據(jù)采集系統(tǒng)與16位8通道單電源隔離式數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

ADI研討會(huì):如何簡化數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

低阻抗電源驅(qū)動(dòng)ADC輸入會(huì)如何影響數(shù)據(jù)采集系統(tǒng)

16位、100 kSPS、單電源、低功耗數(shù)據(jù)采集系統(tǒng)

評論