Other Parts Discussed in Post:LM10011

系統級節電與功率預算優化是許多應用的關鍵。例如,數據中心運營商努力控制能耗,便攜式設備設計人員力圖降低流耗實現更長的電池使用壽命,而通信系統則需要降低工作溫度提高穩定性。電源設計主要規范的當前著眼點是:1)在整個負載電流范圍內最大限度提高效率;和 2) 根據負載需要自適應縮放輸出電壓。

使用電壓識別 (VID) 調節輸出電壓是滿足這些需求的方法之一。當然,在英特爾和 AMD 提供的眾所周知的自適應電壓縮放 (AVS) 規范基礎上,VID 可編程性已經在微處理器應用的 DC/DC 內核電壓穩壓器中得到了廣泛使用。然而,這些 VID 控制器建立在多相位降壓拓撲基礎之上,在特性上專門圍繞超大電流需求進行了定制。

DSP、FPGA 以及 ASIC 現在具有類似的功能,可根據器件活動、電源及時鐘域配置、工作模式以及工作溫度,實現最大限度的功耗降低。雖然支持 VID[1] 的數字化脈寬調制器 (PWM) 控制器解決方案可用來滿足這一需求,但確實也需要對無處不在地模擬控制負載點 (POL) 穩壓器進行輸出電壓數字化調節。在調節過程中,可輕松調整模擬電源實施(或許已經完成設計或已經通過測試臺測試),滿足其它方案無法實現的系統級功率預算與成本目標要求。

數字輸出電壓調節

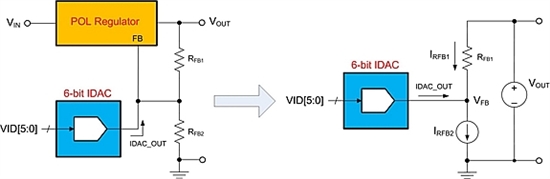

鑒于上述設計目標中的優勢利益,TI 現在提供一款 VID 編程器[2]作為專用標準產品 (ATSP)。圖1是用于補充模擬型 POL DC/DC 解決方案的 LM10011,其包含高精度數字可編程電流數模轉換器 (IDAC),支持模式可選 4 位及 6 位 VID 接口。IDAC_OUT 引腳的精確 DC 電流與 4 位或 6 位數字輸入字成比例,可輸入到輸出穩壓環路的反饋 (FB) 節點。隨著輸入字的累加,IDAC_OUT 電流可降低,從而可根據穩壓器反饋電阻器調高輸出電壓設置點。FB 節點一般由模擬控制環路的誤差放大器保持在恒定電壓下。

圖1:常規POL穩壓器與電流DAC配對,構成6位數字VID接口

該實施過程中最為重要的是 VID 解決方案與模擬 POL 穩壓器設計方案的兼容性。POL 可有效部署為 DSP 的從設備。根據設計,該 IDAC 解決方案可幫助 DSP 及其它數字負載實現其全面的節電性能,降低功耗,例如在通信基礎設施應用中。實際上,該款 VID 解決方案主要用于與任何 POL 穩壓器一起工作,調節 KeyStone? 多核 DSP [3] 等支持 VID 功能的處理器的內核電壓 (VCORE)。

DSP內核電源

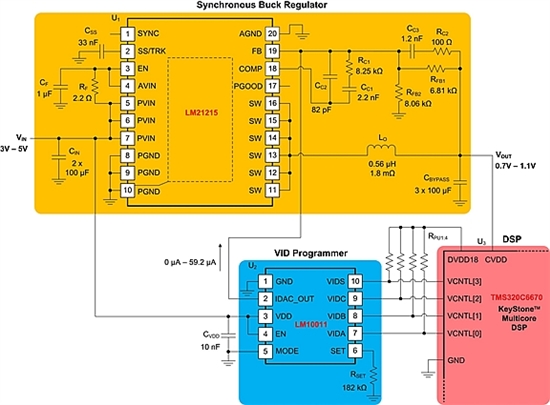

圖 2 是同步降壓 POL 穩壓器提供的、具有內核電壓 CVDD 的多核 DSP 原理圖。電源級包括 15A 電壓模式穩壓器、560nH 電感器以及陶瓷輸入輸出濾波器電容器[2]。來自 DSP 的 6 位 VID 命令有助于根據 DSP 性能要求的不斷變化調節輸出電壓 VOUT。

圖2:使用可調節性受VID控制的同步降壓穩壓器為支持內核電壓軌的多核DSP/SoC平臺供電

根據圖2所示的系統實施方案,具體控制方案針對 6 位 VID 使用了 4 線 (VCNTL) 接口,從而可在 VID 工作中實現更高的分辨率或精細粒度。IDAC_OUT 電流具有 59.2μA 的最大滿量程范圍 (VID[5:0] = 000000b = code 0)。在 6 位模式下,這可提供分辨率為 940nA 的 64 種設置以及優于 1% 的誤差精度。

輸出電壓由 DSP 判定為電壓介于 0.7V 至 1.103V 之間的電平。這相當于 VOUT 調節分辨率為 403mV/63 或 6.4mV。壓擺限制可防止輸出發生突變。而 VID 的抗尖峰脈沖濾波器則可提供噪聲抗擾度(實際上是在 VID 線路的轉換與 IDAC_OUT 電流的后續變化之間添加一個小小的延遲)。在接收到 VID 命令之前的啟動過程中,IDAC_OUT 電流可根據 RSET 值,假設為 16 個分立電平之一。這允許 DSP 的內核電壓在各種電平下上電,實現更高的系統靈活性與可靠性。

但值得注意的是具體的 DSP 可能無法支持所有的電壓或范圍。例如對 KeyStone I DSP 而言,預期工作范圍在代碼 31 和 50 之間(0.905V 至 1.020V)[4]。圖2中 LM10011 的電源電壓來自輸入總線。另一種選項是使用 PWM 控制器提供的、或系統中其它地方(如果有)提供的額定 3.3V 或 5V 偏置電壓軌。無需在 DSP 和電流 DAC 之間使用電平轉換器或膠合邏輯。

有關 VID 接口及相關定時細節更加詳細的說明。VCNTL[2:0] 可為每個 VID 代碼承載兩位數據。處于低或高電平的 VID 分別可用來選擇較低及較高的數位,而處于高電平的 VIDS 也可鎖存 VID 命令,從而可使用 40μs 時間常數初始化 IDAC_OUT 的電流變化。因此每次電壓調整都要求從 DSP 到控制器的兩次對頭拼接的訪問。第一次訪問寫入較低的三位,第二次訪問寫入較高的三位。

使用 VID GUI 軟件[5]可記錄啟動時輸出電壓波形和跟隨高、低 VID 轉換的瞬態響應,如圖4所示。輸入電壓為 5.3V。和預想的一樣,輸出電壓轉換發生在 VIDS 信號的上升沿。

總結

本文中我們簡單淺顯地探討了與 DSP 功率預算優化有關的種種挑戰,介紹了一種通過 VID 接口來使用低成本模擬 POL 控制器的簡單方法。文中包括主要的設計注意事項與電路實施。這種方法復雜性低,簡單易用,適用于功率及 BOM 優化的應用,可充分滿足其隨時存在的上市時間及成本限制需求。簡單、準確和低成本是重要的設計指標。

了解有關 LM92x 數字電源控制器的更多詳情;

LM10011 VID 編程器;

觀看本視頻,深入了解第一個 VID 編程器;

進一步了解支持 SmartReflex 的 KeyStone 多核 DSP SoC;

下載 LM10011 GUI 設計工具軟件。

閱讀原文, 請參見: http://www.edn.com/design/power-management/4421699/1/Optimizing-DSP-power-budget-by-adjusting-regulator

編輯:jq

-

dsp

+關注

關注

553文章

7987瀏覽量

348768 -

穩壓器

+關注

關注

24文章

4223瀏覽量

93762 -

電源管理

+關注

關注

115文章

6180瀏覽量

144452 -

代碼

+關注

關注

30文章

4780瀏覽量

68529 -

POL

+關注

關注

0文章

81瀏覽量

27460

發布評論請先 登錄

相關推薦

數字穩壓器與傳統穩壓器的比較

如何提高穩壓器的使用壽命

低壓穩壓器與高壓穩壓器區別

LDO穩壓器和串聯穩壓器的區別

通過優化的功率級布局免費提高大電流直流/直流穩壓器的EMI性能

如何通過調節穩壓器優化DSP功率預算

如何通過調節穩壓器優化DSP功率預算

評論