在日常工作中,大家應該都會經常遇到需要調節cascode的bias這種情況。不敢自吹自擂的說,作者君目前還是能挺快的調好管子的參數的。不過回想起來剛學模擬電路的時候,作者君也是曾經感覺是如打地鼠一般的痛苦。

所以作者君就想跟小讀者們分享一下自己的經驗,幫助大家更快的跳過這個“打地鼠”的環節。

PS:大部分情況下,我們假設一旦電流確定,Vgs也是確定的。

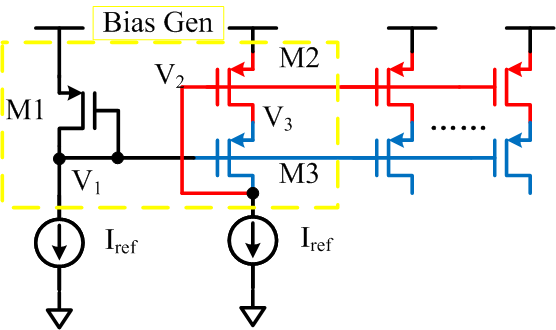

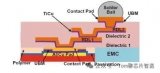

如圖這樣的一個bias 產生電路。我們有了從外面拉進來的兩路電流Iref,所以這左邊三個管子就是我們調節這個bias的全部工作量了。應該很容易吧?

讓我們試試看?

首先確定V1.

因為V1是diode M1產生的,對于右邊的M2和M3來說,它包括兩個電壓,Vgs3和Vds2. 我們來分別看看這兩方面:

Vgs3:因為電流已經確定,所以如果M3在飽和區,那么Vgs3也是確定的。

如果Vdsat3大概在100mV到200mV之間(作者君的習慣),并且M3的Vds3也大概比Vdsat3多100mV左右,作者君會認為M3的size就調好了,不需要動了。

如果Vdsat3的數值太小,也就是這個管子太過于strong了,減小(W/L)3就好;

如果Vdsat3的數值太大,也就是這個管子太過于weak了,增大(W/L)3就好;

Vds2:M2是主要的電流源,所以一般給它預留的Vdsat2,以及Vds2會稍微大一些。比如作者君一般的習慣,Vdsat2會給大概150mV到250mV的預留。同樣Vds2會給多100mV左右的預留。

假設我們已經調節好了M3的size。如果此時看到的Vds2在我們預留范圍內,那么就大功告成了。撒花!

如果Vds2過小,那么就減小V1吧!因為一個飽和區的M3,V3其實是會跟著V1一起浮動的。減小V1就很容易了,M1是個diode嘛!要讓M1的Vgs變大,那就減小(W/L)1.

跟V1相關的M3已經確定了,我們來花力氣針對一下和V2有關的M2吧!

首先,我們還是看看M2的周圍環境:M3已經確定的情況下,V3是基本固定的;

此時,如果Vgs2大小合適,也就是Vdsat2是在前面提到的范圍內,那就哈哈哈,完工!

如果Vgs2不夠好,那就調M2吧!

Vgs2如果太小,說明M太strong,減小(W/L)2就好;

Vgs2如果太大,說明M太weak,增大(W/L)2就好;

最后,我們在已經確定了M1,M2,M3的情況下,再重新看看M2和M3的Vds。

可能出現的一種情況是:M3的Vds3有點大。假設這種情況:理想的Vds3是250mV,Vds2是350mV,但是此時的Vds3是500mV。

大家想想看,為什么會出現這樣的情況呢?

一般來說,這是由于比較大的Vth2造成的。

因為Vgs2=Vds2+Vds3,所以如果此時的Vth2是600mV,Vdsat2是250mV,就會出現Vds2是350mV,而Vds3是500mV的情況。

怎么辦?或者說需要調嗎?

那就看你的要求啦!如果一般情況下你的電流源的負載會讓M3的drain這邊產生大概1V的電壓,當你的Vdd是1.8V的時候,等效M3的Vds3也有450mV。作者君覺得,放過自己未嘗不是一件好事情?^_^

如果你的Vdd只有1.6V(不要問我為什么設置這樣的Vdd,當然是為了好算啊!1V+250mV+350mV),嘿嘿嘿,沒辦法,革命尚未成功……

因為調節M2和M3的過程就是打地鼠,如果只是Vds3造成的問題,我們為什么不換個思考方向呢?

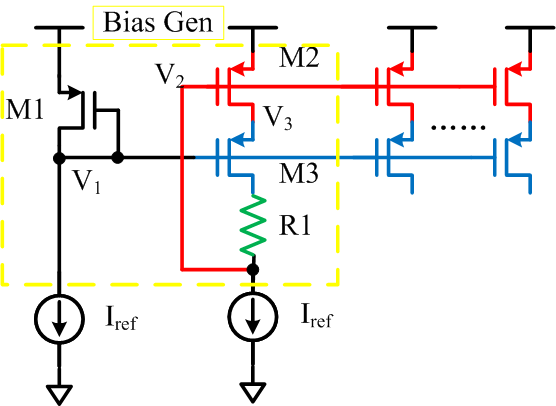

當當當!surprise!加個電阻R1就好了!

這個電阻分去了Vds3上面不應該有的500mV-250mV=250mV的電壓,讓這個bias的產生支路和有外界loading的右邊各個支路的情況變得接近。所以能過讓current mirror變得更準確。

最后留個課堂作業吧?有時候,我們能看到有這樣的電阻R2-4存在,大家說說它有什么作用?

PS:最后多說一句,如果需要有倍數的加大current mirror,大家務必保證L是一樣的。比如說W/L=1u/0.5u是bias產生模塊里面2uA對應的size,那么要mirror出4uA的電流,應該是W/L=2u/0.5u,而不是說只要ratio成比例就行。大家可以試試看4u/1u能不能讓你得到精確的mirror的4uA電流?

編輯:jq

-

模擬電路

+關注

關注

125文章

1556瀏覽量

102719 -

電流

+關注

關注

40文章

6846瀏覽量

132110 -

Cascode

+關注

關注

0文章

3瀏覽量

6943

原文標題:基本cascode單元的細節討論

文章出處:【微信號:analogIC_gossip,微信公眾號:通向模擬集成電路設計師之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

存儲單元是指什么

三星做出重大決策,投資圖形處理單元(GPU)

柔性制造單元及柔性的定義

細節控必備!東芝“顯微屏”電視Z700NF,打造專精細節的“顯微屏”電視

單元/集成測試服務

射頻單元中的異常分析

深度剖析汽車內部結構和原理

剖析基本cascode單元的細節

剖析基本cascode單元的細節

評論