QA&問:電阻電壓系數(VCR)的影響

什么是電阻電壓系數?

本文就來回答這個問題。

VCR(電阻電壓系數)定義為電阻在特定的電壓變化范圍內發生的變化。這意味著電阻值在不同電壓下的穩定性。你(包括我自己)可能并沒有意識到VCR的存在,但每個電阻在加載電壓時都存在某種程度的不穩定性。對于電壓電平穩定或可調節且可預測的應用而言,VCR不是問題。但對于電力輸送系統或測試設備等其他應用而言,電壓的變化會導致電阻發生不可接受的變化。

那么應該如何最大程度地減少VCR的影響呢?

選擇正確的電阻并了解影響VCR的因素,可將VCR降至最低。與采用直寫工藝的電阻相比,采用標準厚膜沉積工藝的電阻的VCR更差。這是受改善的電阻精度以及減少的邊緣的影響。實際上,較大尺寸的電阻具有較好的VCR,因為可以使用歐姆值較低的材料來實現高阻值。

在制造電阻時,常用激光或機械修整工藝將電阻值調整到規定的公差范圍內。其電阻公差通常在1%左右或以下。然而,在制造過程中,修整電阻元件可能會對電阻的VCR產生不利影響。對于厚膜片式電阻而言,對電阻元件執行此類校準修整會產生微裂紋,因為在修整后厚膜材料將會冷卻。這種微裂紋會導致寄生阻抗變化、電噪聲提高和VCR增加。

編輯:jq

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:消除VCR電阻電壓系數影響,你該怎么做?

文章出處:【微信號:得捷電子DigiKey,微信公眾號:得捷電子DigiKey】歡迎添加關注!文章轉載請注明出處。

相關推薦

晶硅太陽能板具有更高的轉化效率。同時,要確保太陽能板的質量可靠,以減少因質量問題導致的能效損失。 逆變器 :逆變器是將太陽能板產生的直流電轉化為交流電的關鍵設備。選擇高效、穩定的逆變器可以最大程度提高電能轉換效率。 二、

![的頭像]() 發表于

發表于 12-05 11:06

?284次閱讀

減少EMI(電磁干擾)是電子電路和系統設計中非常重要的一項任務,以下是一些減少EMI的有效方法: 一、屏蔽 屏蔽是用來減少電磁場向外或向內穿透的措施,可以分為靜電屏蔽、電磁屏蔽和磁屏蔽三種

![的頭像]() 發表于

發表于 11-20 14:40

?646次閱讀

在交流耦合輸入的情況下,將 BTL 模式下的輸出失調電壓指定為高達 150mV。這對PBTL 模式是否同樣適用?如何才能最大限度地減少電壓失調,或者調節為 0?

發表于 11-08 08:02

在電子電路設計中,硬件工程師們經常將注意力集中在電阻的阻值、功率額定值、容差和溫度系數(TCR)等參數上,以確保設計的精度和穩定性。然而,電阻的電壓系數(VCR)這一參數常常被忽視。雖然在一些設計中

![的頭像]() 發表于

發表于 11-06 09:40

?469次閱讀

電子發燒友網站提供《最大限度地減少TRF7964A和TRF7970A省電模式下的電流消耗.pdf》資料免費下載

發表于 10-26 10:57

?0次下載

電子發燒友網站提供《最大限度地減少TPS53355和TPS53353系列器件的開關振鈴.pdf》資料免費下載

發表于 10-15 11:17

?0次下載

電子發燒友網站提供《最大限度地減少UCC287XX系列的待機消耗.pdf》資料免費下載

發表于 09-25 09:35

?0次下載

電子發燒友網站提供《通過優化補償最大限度地減少導通時間抖動和紋波.pdf》資料免費下載

發表于 08-26 11:34

?0次下載

德索工程師說道在探討使用4芯M9插頭是否能減少安裝時間之前,我們需要先明確安裝時間的影響因素。安裝時間的長短通常取決于多個因素,如連接器的設計復雜度、安裝操作的難易程度、以及安裝工具的使用等。因此,要評估4芯M9插頭是否能減少安

![的頭像]() 發表于

發表于 04-17 14:44

?829次閱讀

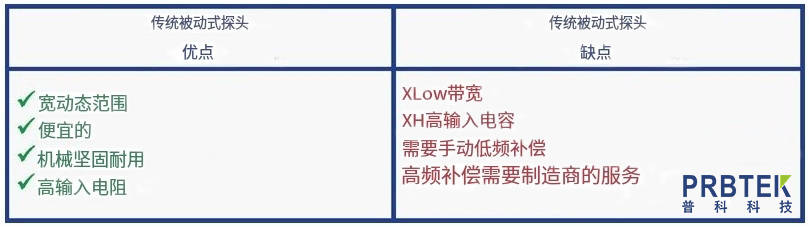

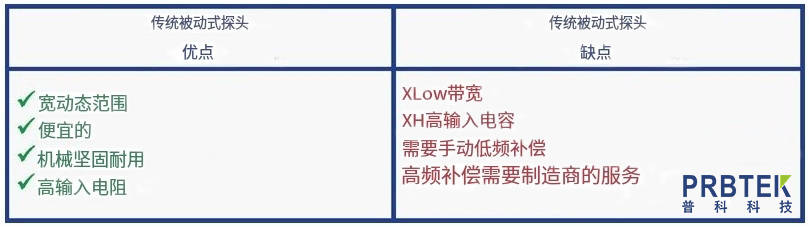

探測電路總是會對信號產生一定的影響。探頭負載會改變被探測的信號,可能導致測量問題,甚至可能導致電路執行不同的操作。減少電容負載可以幫助最大限度地減少這些影響。在本應用中,您將了解低電容探頭如何改進

![的頭像]() 發表于

發表于 03-25 10:51

?521次閱讀

電阻器VCR

深圳崧皓電子

發布于 :2024年03月25日 06:37:27

隨著城市的發展和人們生活水平的提高,對公共設施的需求也越來越大。然而,在局部資源有限的情況下,如何合理分配設施資源成為一個重要的問題。GIS最大覆蓋模型通過優化設施位置,以最大程度地滿足區域內

![的頭像]() 發表于

發表于 02-25 15:04

?1428次閱讀

快充對電池有傷害嗎 如何最大限度地減少快充對電池的影響 快速充電(也被稱為快充)是一種可快速給手機電池充電的技術。雖然快充在我們日常生活中帶來了便利,但很多人擔心它是否會對手機電池的壽命產生負面影響

![的頭像]() 發表于

發表于 02-19 10:01

?1915次閱讀

在我的應用程序中,HSPDM 觸發 EVADC 同時對兩個通道進行采樣。

我應該如何配置 EVADC 以最大限度地減少采樣抖動并最大限度地提高采樣率?

在用戶手冊中,它提到 SSE=0,USC=0

發表于 01-18 07:59

我以前用過AD6645,現在在用ad9238畫板子,做中頻信號采集。板子上還有高速FPGA以及DSP。由于adc的位數比較高,14bit和12bit,我不太清楚板子的底噪要做到什么程度才能最大

發表于 01-09 07:45

如何最大程度地減少VCR的影響

如何最大程度地減少VCR的影響

評論