RISC-V在云端、數(shù)據(jù)中心、汽車與網(wǎng)絡(luò)技術(shù)中的頻繁創(chuàng)新和亮相,已經(jīng)讓這一成長中的ISA一只腳邁入了高性能計算場景。然而缺少強(qiáng)大的性能監(jiān)測工具讓RISC-V的應(yīng)用優(yōu)化成了問題,尤其是在RISC-V如今不少軟件源于從非原生移植的情況下,運(yùn)算性能不能發(fā)揮出百分百的實(shí)力成了令人頭疼的問題。

與此同時,英特爾和ARM都擁有自己專用的性能監(jiān)控方案,讓開發(fā)者可以發(fā)揮出其硬件的全部效力,但RISC-V仍然依靠定制或廠商特定的方案,而缺少通用性能監(jiān)控軟件工具的完整支持。

Perf對RISC-V的支持

系統(tǒng)級的性能優(yōu)化往往是靠性能剖析和代碼優(yōu)化來實(shí)現(xiàn)的,前者是為了尋找性能瓶頸,后者則是為了改善軟件性能,因此這類性能分析/監(jiān)控工具成了處理器開發(fā)時必不可少的軟件。盡管RISC-V的ISA規(guī)范已經(jīng)定義了硬件性能監(jiān)控(HPM),但總體支持程度上仍未完善。

就以Linux上的性能分析工具Perf為例,該工具可以借助PMU(性能監(jiān)控單元)、tracepoint和內(nèi)核計數(shù)器來分析程序中的硬件事件,比如處理器時鐘周期、指令計數(shù)器等,也可以分析一些軟件事件,比如Page Fault等。

Perf分為兩種模式,一種是perf stat,一種是perf record。如今上游Linux的perf雖然已經(jīng)對RISC-V有了支持,但僅對perf stat有一些基本的支持。比如mcycle這一CSR用于處理器運(yùn)行的時鐘周期計數(shù),而minstret這一CSR則用于退休指令計數(shù)。

RISC-V privileged規(guī)范中,RISC-V定義了幾種特權(quán)模式,分別是U-mode(用戶模式)、S-mode(管理員模式)和M-mode(機(jī)器模式)。但目前只有在機(jī)器模式下才能對這些寄存器進(jìn)行讀寫,管理員模式下缺乏可寫入的寄存器。

計數(shù)器卻又是每時每刻運(yùn)行中的,所以現(xiàn)在可以做到周期和指令計數(shù),卻無法啟用、禁用和暫停計數(shù)器,無法使用任何可編程計數(shù)器和事件采樣。不僅如此,RISC-V的perf不僅無法處理計數(shù)器溢出,也不支持溢出中斷。雖然市面上很多RISC-V處理器已經(jīng)考慮到了這一點(diǎn),采用定制的形式來完成部分任務(wù),比如Esperanto就為自己的ET-SoC-1千核RISC-V處理器加入了商業(yè)級的芯片除錯與性能監(jiān)控能力,但RISC-V規(guī)范本身缺少這些支持,這也就不利于當(dāng)下RISC-V的開源生態(tài)。

完整的Perf支持缺少了什么?

于是我們現(xiàn)在發(fā)現(xiàn)管理員模式下無法寫入計數(shù)器,也無法改變mcountinhibit來直接開啟或停止計數(shù)器,也無法改變mhpmcountern來開啟或禁用直接讀取。接著就是沒有中斷指示器,我們不知道哪一個計數(shù)器出現(xiàn)了數(shù)值溢出,也沒有事件篩選功能。那么針對這些問題的解決方案是什么,哪些措施才能實(shí)現(xiàn)完整的Perf支持呢?來自西部數(shù)據(jù)的Atish Patra在近期的RISC-V峰會上提出了他以及開發(fā)社區(qū)所青睞的答案——SBI PMU擴(kuò)展和sscofpmf ISA擴(kuò)展。

SBI PMU擴(kuò)展將作為一個接口,讓管理員模式下的軟件發(fā)現(xiàn)硬件計數(shù)器的細(xì)節(jié),針對特定的perf事件來配置硬件計數(shù)器,在請求下開始或停止計數(shù)器。除此之外,SBI PMU擴(kuò)展還引入了固件性能計數(shù)器來監(jiān)控固件事件,比如未對齊的存取指令數(shù)、RFENCE和IPI數(shù)等等。如今在RISC-V的SBI 1.0版本中我們也可以看到,PMU擴(kuò)展已經(jīng)成了該規(guī)范的一部分。

接著是sscofpmf擴(kuò)展,ss代表的是特權(quán)架構(gòu)和管理員級的擴(kuò)展,cofpmf代表的是溢出計數(shù)和特權(quán)模式篩選。該擴(kuò)展新增了一個32位的scountovf只讀寄存器,該寄存器存儲的是29個mhpmcounter的第63位(OF),如此一來就能準(zhǔn)確快速地判斷究竟是哪個事件的計數(shù)器溢出了。這一擴(kuò)展已經(jīng)凍結(jié),目前處于審查狀態(tài),預(yù)計不久的將來就會批準(zhǔn),來自Linux內(nèi)核的支持工作也在推進(jìn)中。

小結(jié)

RISC-V作為一個尚處于發(fā)展初期的架構(gòu),在某些方面確實(shí)還有不及其前輩x86和ARM的地方,我們這次從性能監(jiān)控上就能看出一些端倪,但RISC-V自身的特性也為它帶來了不小的優(yōu)勢。

首先,RISC-V是站在巨人的肩膀上發(fā)展的,它可以有效地規(guī)避以上那些架構(gòu)走錯的老路。其次,開源開放讓RISC-V有了龐大的社區(qū)支持,像以上這些解決方案,其實(shí)已經(jīng)被多次提及,來自社區(qū)的力量勢必可以讓RISC-V走得更遠(yuǎn)。

審核編輯:何安淇

-

監(jiān)測

+關(guān)注

關(guān)注

2文章

3597瀏覽量

44509 -

RISC-V

+關(guān)注

關(guān)注

45文章

2271瀏覽量

46133

原文標(biāo)題:優(yōu)化的關(guān)鍵,RISC-V中的性能監(jiān)控

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

聽懂什么是信號完整性

ADS8866按照TI的3線MODE時序讀數(shù),讀出的數(shù)據(jù)少了3位,為什么?

高速PCB的信號完整性、電源完整性和電磁兼容性研究

官方,buildroot文件系統(tǒng)支持gstreamer嗎?

信號完整性與電源完整性-電源完整性分析

信號完整性與電源完整性-信號的串?dāng)_

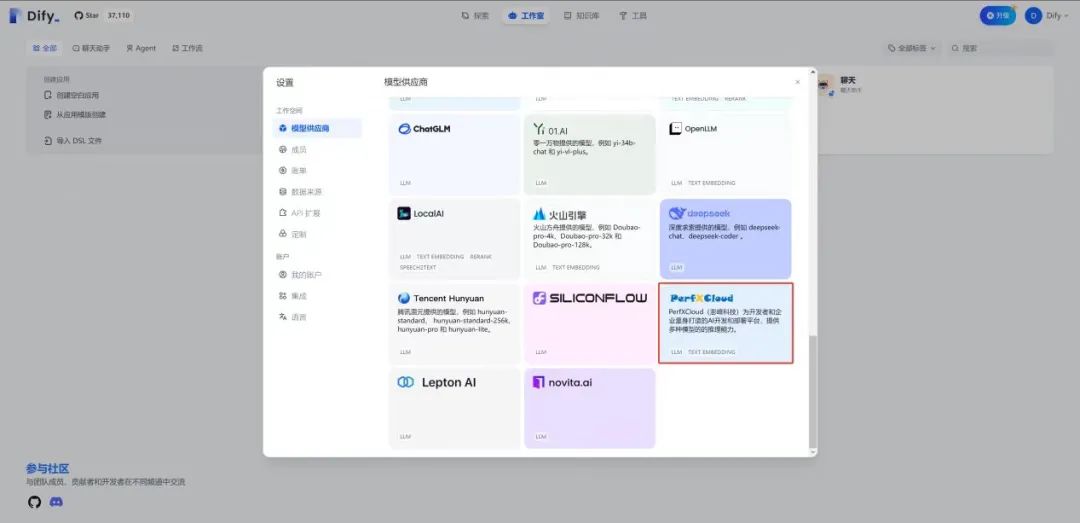

在Dify中使用PerfXCloud大模型推理服務(wù)

完整的Perf支持缺少了什么

完整的Perf支持缺少了什么

評論