小芯片(Chiplet)已經成為當今大廠角逐的一大方向,對于小芯片來說,需要一種芯片到芯片的互連/接口技術,現在已有多種Die-to-Die接口可以滿足這類需求。其中,基于SerDes的或并行的Die-to-Die接口在數據速率、引腳數量和成本等方面都有其獨特的優勢。但在設計用于諸如數據中心、人工智能 (AI) 訓練或推理、服務器和網絡等高性能計算 (HPC) 應用的高端Muiti-die SoC時,為了讓不同的供應商開發的Multi-Die SoC實現互操作,業界正著力于建立Multi-Die的互連標準,以維護一個成功的生態系統。

OpenHBI憑借最高邊緣密度標準從眾多die-to-die標準中突出重圍,成為HPC等對小芯片間傳輸帶寬要求極高的系列應用的最佳接口標準。

為何使用并行 Die-to-Die 接口?

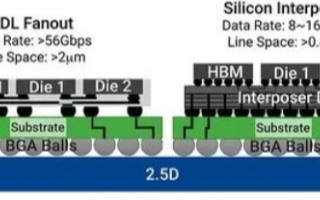

現在多家芯片廠商利用小芯片模型將芯片集成到現有的高級封裝類型中,這些裸片可以是不同工藝節點的,裸片可以并排放置,并通過專用die-to-die接口相連接,這是一種普遍且成本較低的方法。如想獲得更高的密度,可以將這些組塊封裝在2.5D或3D設計中。

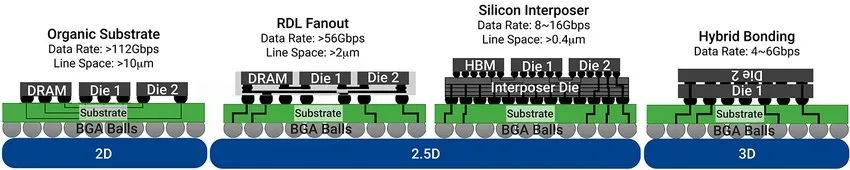

在此,我們先科普下常見的三種封裝形式,一個是2D封裝,把各個Chiplet組裝在有機基材和層壓板上;一個是2.5D封裝,它的中介層使用硅或再分配層 (RDL) 扇出,用于在SoC中傳遞Chiplet間的信號;還有一個是3D封裝,它使用混合粘合技術來垂直堆疊Chiplet。

▲ 圖1 封裝選項

其中2.5D封裝由于采用RRL扇出技術,能夠橋接2D技術的低成本和硅中介層的密度,又有許多代工廠以及傳統的OSAT提供商可提供此類服務,進一步降低了成本,因此成為了一種有吸引力的選擇。

對于那些對封裝成本和復雜度不敏感的高性能計算 SoC,并行Die-to-Die接口已成為首選技術。這主要是因為,并行Die-to-Die接口基本上都包含了大量的(上千個)IO 引腳,來驅動跨Chiplet的單端信號。由于每個引腳的數據速率僅為幾個G字節/秒 (Gbps)(8至16 Gbps),且Chiplet之間的距離僅為幾毫米(3至5毫米),因此驅動器和接收器都可以簡化,同時實現遠低于1e-22至1e-24的系統誤碼率 (BER)。不需要額外的糾錯機制,例如前向糾錯 (FEC) 和重試,系統BER就可以滿足要求,從而避免增加鏈路復雜性和延遲。

通過簡化IO、消除串并轉換 (SerDes) 步驟,并避免超高速信號傳輸,并行Die-to-Die接口能夠實現極高的能效和較低的延遲,同時支持整個鏈路的極高吞吐量。因此,并行Die-to-Die接口對于不受封裝成本和裝配限制的高性能計算應用SoC非常有吸引力。

Die-to-Die接口標準應運而生

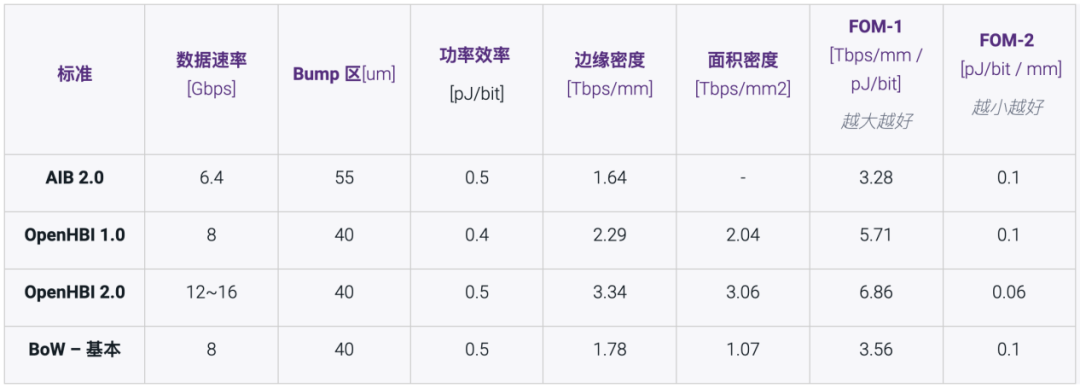

現在的小芯片方案,各家都為并行Die-to-Die接口部署了許多專有架構。為了建立一個穩健的生態系統,讓不同的供應商所開發的以及不同功能的Chiplet互聯操作,行業開始制定Die-to-Die接口標準,主要包括AIB、OpenHBI、BoW等,為先進封裝中的并行Die-to-Die接口提供特性。表1顯示了不同標準的主要特性比較。

▲ 表1 先進封裝的并行Die-to-Die接口標準 (來源:OCP Tech Week全球技術峰會,2020年11月)

先進封裝由于凸塊間距大,封裝路由密度高,在同等能效的情況下,對外形尺寸和邊緣效率的要求更高。在以上這些標準中,OpenHBI能提供最高邊緣密度的標準,非常適用于必須在兩個Chiplet之間傳輸極高帶寬的應用。它可達到每引腳8Gbps的速度,在最大數據速率下可以達到3mm的最大互連長度并實現小于或等于0.5pJ/bit的功耗目標。

什么是 OpenHBI?

OpenHBI利用JEDEC的HBM3電氣特性和IO類型來降低風險。它使用低電壓和未端接的單端 DDR 信號來傳輸Chiplet之間的數據。OpenHBI標準具有許多關鍵特征:

整合多個OpenHBI兼容的Die-to-Die接口,實現互操作性

利用JEDEC HBM3 IO類型和電氣特性

可與支持HBM存儲器和OpenHBI標準的雙模HBM主機控制器互操作

支持硅中介層和晶圓級集成扇出或同等技術

實現對稱Die-to-Die接口

實現目標速度:每引腳 8Gbps,正邁向12-16Gbps

在最高數據傳輸速率時提供長達3mm的互連距離

實現小于等于0.5pJ/bit的功耗目標

提供大于1.5T位/毫米(包括發射器和接收器)的線性(邊緣)帶寬密度

定義 PHY 和邏輯 PHY 抽象層,輕松適配上層

支持正常的和旋轉的Chiplet方向

可以調整帶寬和邊緣(DW 數量)以匹配各種用例

支持小芯片 (Chiplet) 配置和測試 (CCT) 接口

支持通道修復,提高制造良率

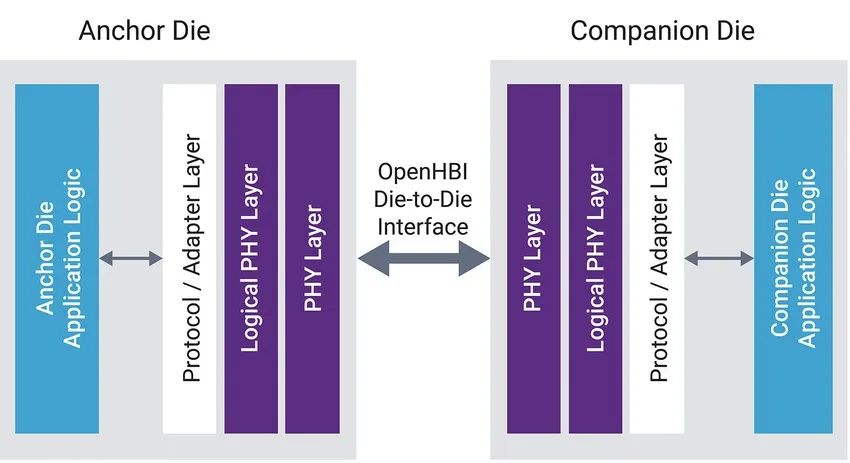

OpenHBI標準主要針對圖2所示的下層(PHY和邏輯PHY層),然后將適配器層用于與上層(協議層)進行連接。因此,系統可實現不依賴于各個應用所用的協議。

▲ 圖2 OpenHBI 接口邏輯劃分

PHY層主要執行提供時鐘、變速器(數據速率轉換 N:1)、校準和訓練、通道修復以及數據傳輸和恢復的功能。如果需要,邏輯 PHY層將執行以下功能:奇偶校驗生成和校驗、數據成幀和對齊、數據總線反向、位重新排序。

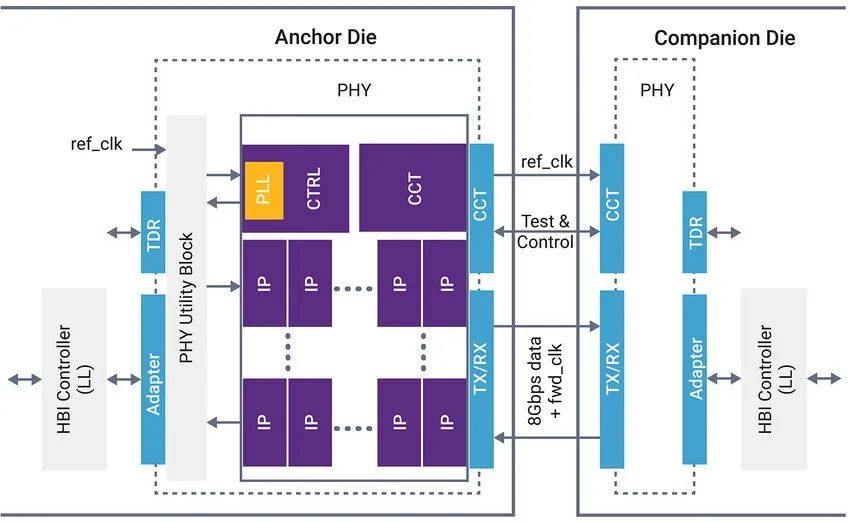

圖3展示了一種OpenHBI PHY實現方案,可以將不同的功能分割到不同的實現中。

▲ 圖3 OpenHBI PHY IP模塊圖

PHY使用時鐘轉發技術,其中傳輸時鐘和數據也在Chiplet之間傳輸。接收端基于DLL的簡單數據恢復電路,可節省功耗和面積。

除了有效載荷數據路徑外,PHY還實現低速CCT,可供錨芯片和小芯片用于傳達配置和狀態參數以及控制DWORD初始化、校準和測試過程。OpenHBI PHY實現I3C、JTAG和供應商自定義信號。此外CCT將參考時鐘從錨芯片傳播到小芯片Chiplet,以便它們共享相同的時鐘參考。

OpenHBI PHY的其他主要功能包括:

帶有APB/TDR接口的配置端口,用于訪問內部控制和狀態寄存器 (CSR)

可配置PHY,支持多種DWORD數量,以適應具體用例

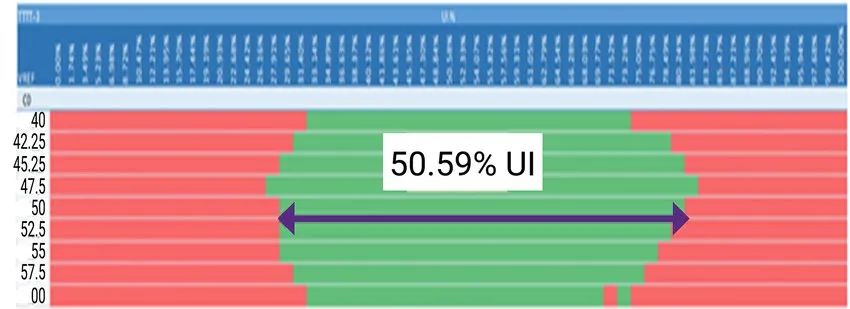

裸片測試(已知良好Chiplet)和封裝后測試的綜合可測試性,包括關鍵模塊 BIST、各種環回模式、模式生成和匹配能力,以及生成重建的眼圖,作為 pass/fail 測試。

新思科技IP助力小芯片的互聯

一些芯片設計公司可能擁有開發自己的小芯片和IP的資源,但即使是較大的公司也負擔不起內部開發所有IP的費用。他們可能希望采購第三方IP以節省時間和金錢。

在這樣的背景下,新思科技可提供一系列Die-to-Die IP,包括高帶寬互聯 (HBI) 和基于SerDes的PHY和控制器。DesignWare HBI PHY IP支持多種標準,包括AIB、BoW和OpenHBI。該IP實現了一個寬并行和時鐘轉發的PHY接口,以先進的2.5D封裝為目標,以利用基于內插器的技術中更精細的芯片到芯片連接。

▲ 圖4 使用新思科技HBI+PHY Die-to-Die鏈路的眼圖

無疑,小芯片的發展前景廣闊,尤其是摩爾定律走到極限的情況下,但是小芯片仍然面臨諸多難題,如設計和集成、生態系統復雜性、制造/測試和產量,資質和可靠性、標準等,但業界正在圍繞著這些難題逐個攻克,相信,未來會有更多的應用采用小芯片的方案。

原文標題:Chiplet互聯難?解決方案在這兒

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

芯片

+關注

關注

455文章

50714瀏覽量

423155 -

封裝

+關注

關注

126文章

7873瀏覽量

142894 -

服務器

+關注

關注

12文章

9123瀏覽量

85328

原文標題:Chiplet互聯難?解決方案在這兒

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Chiplet成大芯片設計主流方式,開啟IP復用新模式

數據中心光互聯解決方案

北極雄芯開發的首款基于Chiplet異構集成的智能處理芯片“啟明930”

先進封裝Chiplet全球格局分析

chiplet和cowos的關系

奇異摩爾與智原科技聯合發布 2.5D/3DIC整體解決方案

互聯與chiplet,技術與生態同行

奇異摩爾聚焦高速互聯:Chiplet互聯架構分析及其關鍵技術

Nordic Chiplet芯片級解決方案助力微型模塊收集和傳輸心電圖數據

西門子EDA創新解決方案確保Chiplet設計的成功應用

UCIe規范引領Chiplet技術革新,新思科技發布40G UCIe IP解決方案

最新Chiplet互聯案例解析 UCIe 2.0最新標準解讀

小芯片(Chiplet)互聯解決方案

小芯片(Chiplet)互聯解決方案

評論