摘要

在濕法工藝實施中使用單晶片處理器是先進半導體制造的一種趨勢,因為它具有無污染、靈活的工藝控制以及在不損壞圖案的情況下提高顆粒去除效率的優點。然而,在氮化硅去除過程中,不僅磷酸消耗的成本問題,而且包括蝕刻速率、均勻性和選擇性在內的工藝性能都是使該工藝難以從臺式轉換到單晶片型的障礙。在這里,我們提出了一種新穎的設計,該設計引入了上晶片加熱板,以保持磷酸蝕刻劑的高溫,從而克服在氮化物剝離工藝中單晶片處理器中蝕刻速率低、均勻性差和選擇性低的常見問題。在這項工作中,研究了單晶片處理器中的操作變量(如轉速、攪拌時間和溫度)對蝕刻速率、均勻性和選擇性的交互影響,以深入了解這一過程。鈣的腐蝕選擇性明顯降低。當H3PO4溫度從144℃升高到154℃時,溫度從100℃升高到60℃,而加熱器板的引入已被證明能顯著提高蝕刻選擇性。

介紹

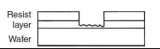

在半導體制造中,氮化硅(Si3N4)和二氧化硅(SiO2)是最典型和廣泛使用的電介質材料,用作硬掩模、犧牲層、注入隔離物或應力誘導膜.1–5氮化硅通常可以通過各種方法去除,例如干法蝕刻、HF、BOE(緩沖氧化物蝕刻)等。然而,在磷酸介質中,氮化硅對氧化物的高蝕刻選擇性使得氧化硅用作蝕刻停止層,以保護下層膜或結構免受氮化物膜剝離產生的損害。

為了克服單晶片處理器在氮化物剝離過程中遇到的上述常見問題,本工作提出了一種新的設計,通過引入加熱板上晶片來保持磷酸溶液的工作溫度和低粘度,以實現高蝕刻速率和良好的均勻性。

實驗

厚度為1200–1800納米的Si3N4薄膜被沉積在二氧化硅薄膜上,以防止在低壓化學氣相沉積(LPCVD)室中由溫度> 700℃的SiH2Cl2和NH3的氣體混合物引起的應力誘發的破裂。因此,制備了兩種樣品,硅/二氧化硅/氮化硅和硅/二氧化硅,用于評估各自的蝕刻速率。這些樣品用煮沸磷酸溶液提供的設備蝕刻.用KLA-滕科爾橢偏儀測量蝕刻前后的氮氧化物沉積厚度,以獲得氮化物或氧化物層厚度的減少。透射電鏡數據證實并校正了該橢偏儀的精度。通過用于光點缺陷檢查的KLA-滕科表面掃描測量工藝前后氧化物涂覆晶片表面上的粒子數,以獲得氧化物層表面上的加法計數。

結果和討論

加熱板的影響。

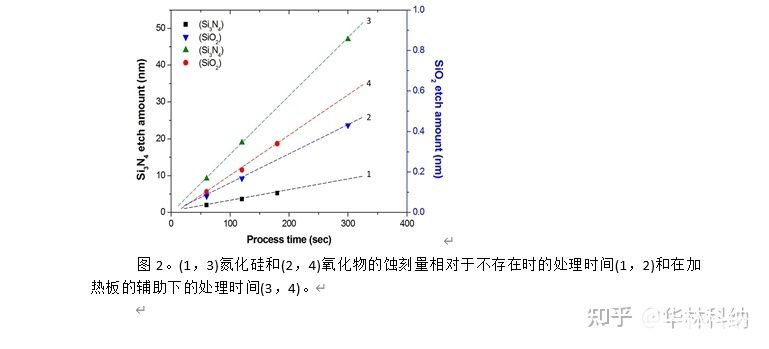

圖2顯示了有無加熱板時二氧化硅和氮化硅的典型蝕刻速率,其中第1行和第2行的數據是從沒有加熱板的單晶片處理器獲得的。

轉速和攪拌時間對氮化硅刻蝕速率的影響。

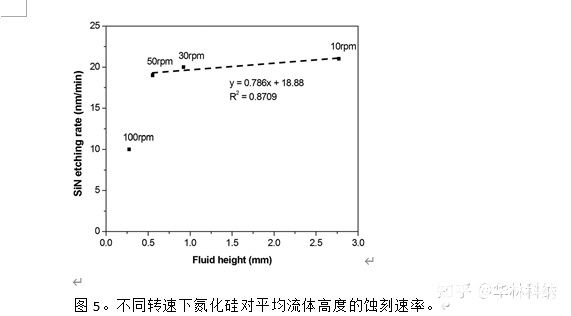

為了獲得加熱板、晶圓旋轉速度、處理時間和化學品之間的關系,必須進行幾項測試。圖5清楚地顯示了在三種轉速(10、30和50轉/分)下,Si3N4蝕刻速率與平均流體高度的線性相關性.這種線性相關性可能是由于流體在最快轉速下的停留時間太短,導致加熱板加熱效率低,導致蝕刻速率比其他速度低得多。同時,用于在較高轉速下有效溶解硅酸的蝕刻劑體積不足也影響了蝕刻速率。由于在這一系列測試中沒有進行攪拌步驟,因此很容易判斷通過加熱板加熱H3PO4以提高蝕刻速率的必要性。

氮化硅對二氧化硅的刻蝕選擇性。

盡管文獻中廣泛討論了Si3N4/SiO2的蝕刻選擇性,但大多數情況是基于試樣或槽式工具。

結論

本文設計了一種具有加熱器板上部晶片的新型單晶片處理器,以保持磷酸的蝕刻溫度,從而克服傳統單晶片處理器在氮化物剝離工藝中遇到的問題。在這種設計中,系統中采用了加熱板來保持晶片表面上磷酸的溫度,因為當流體從管道中分配出來時,高粘性磷酸(對溫度非常敏感)在晶片表面上的不平滑流動會影響蝕刻的均勻性。典型的過程包括3個步驟:(1)以200轉/分的速度在晶片上分配H3PO4溶液3秒鐘;(2)用H3PO4溶液的連續流降低加熱器板;和(3)低轉速下的槳式踏板。在初步測試中,該單晶片處理器的轉速、處理時間和加熱器溫度是有效提高蝕刻均勻性的重要變量。在這項工作中,加熱器板的溫度設置對氮化硅、氧化物的蝕刻速率和蝕刻選擇性有很大影響,同時過高的加熱器溫度不能保持最小的二氧化硅損失,但提供了高的Si3N4蝕刻速率.我們將找到這種單晶片處理器的最佳條件,并在未來的工作中研究硬件參數與加熱器如何幫助蝕刻均勻性之間的關系。

審核編輯:符乾江

-

蝕刻

+關注

關注

10文章

424瀏覽量

15912 -

晶片

+關注

關注

1文章

406瀏覽量

31899

發布評論請先 登錄

呼氣末二氧化碳監測中的傳感器應用

二氧化碳光聲傳感技術

礦井下的“隱形守護者”:解碼礦用二氧化碳傳感器

什么是高選擇性蝕刻

VirtualLab Fusion應用:氧化硅膜層的可變角橢圓偏振光譜(VASE)分析

OptiFDTD應用:用于光纖入波導耦合的硅納米錐仿真

紅外 CO2(二氧化碳) 氣體傳感器和分析模組

芯片濕法蝕刻工藝

OptiFDTD應用:用于光纖入波導耦合的硅納米錐仿真

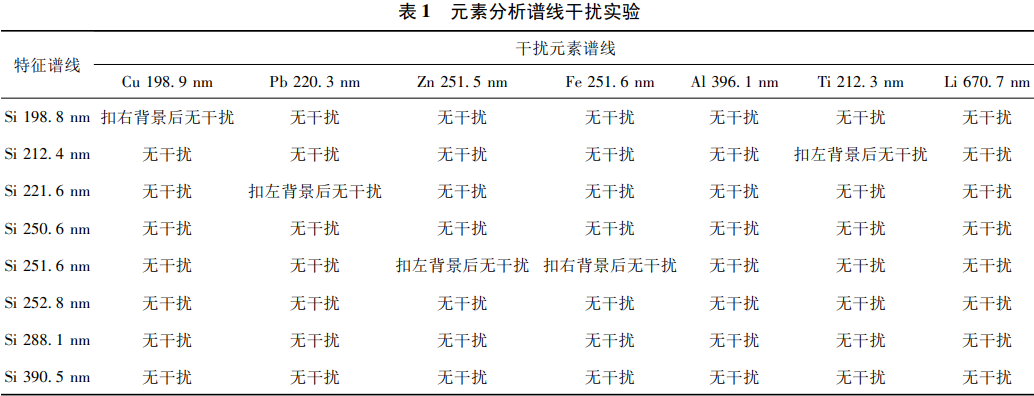

偏硼酸鋰熔融-電感耦合等離子體發射光譜法測定有色金屬礦中二氧化硅

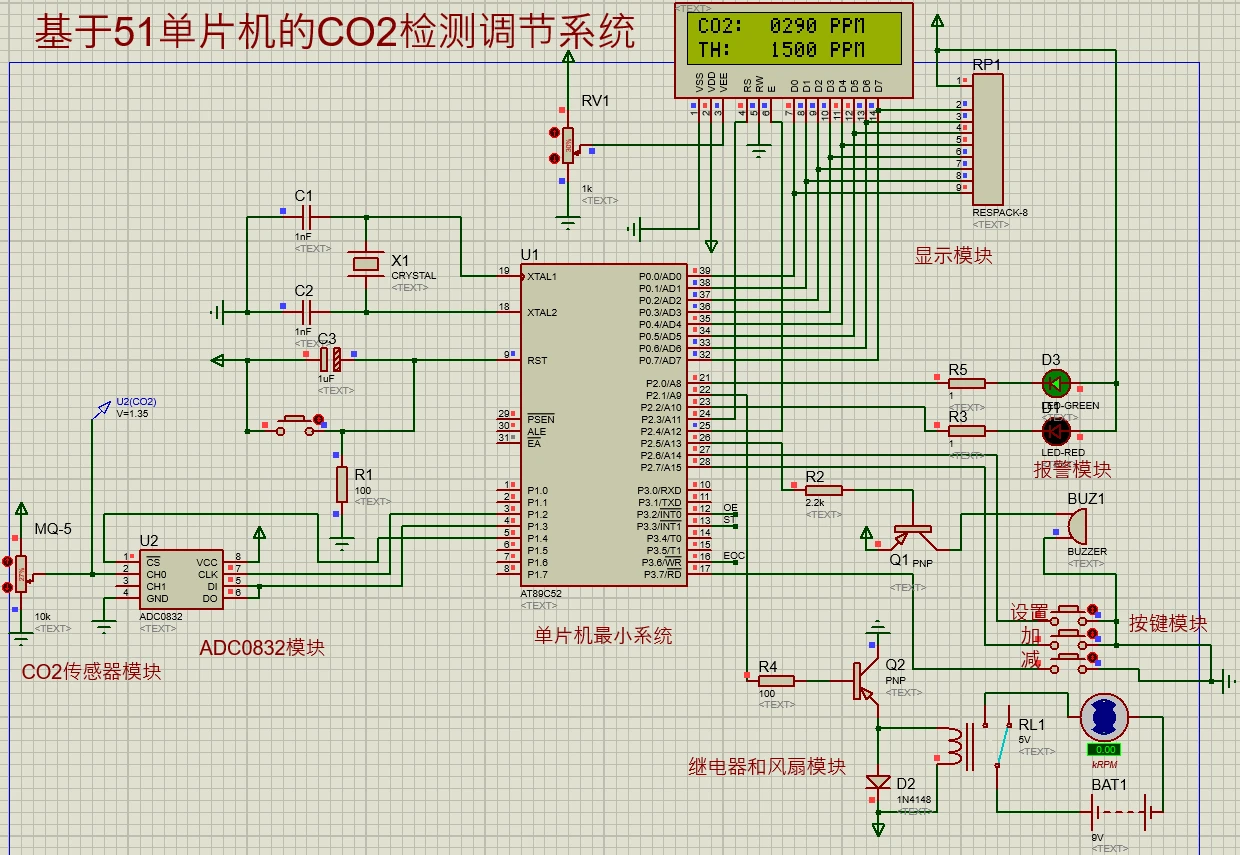

基于51單片機的二氧化碳濃度檢測調節系統仿真

磷酸中二氧化硅的選擇性濕法蝕刻方法

磷酸中二氧化硅的選擇性濕法蝕刻方法

評論