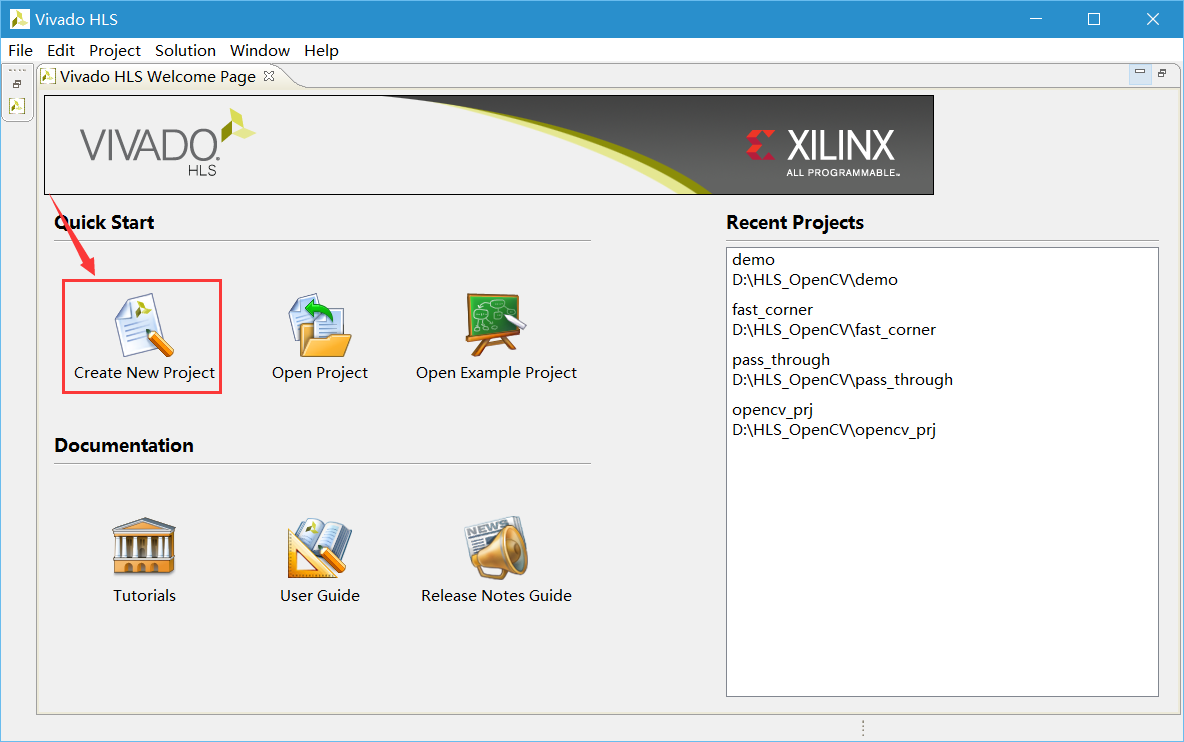

先從運行一個創建一個項目開始吧。

首先打開Vivado設計套件Vivado HLS 2015.4;

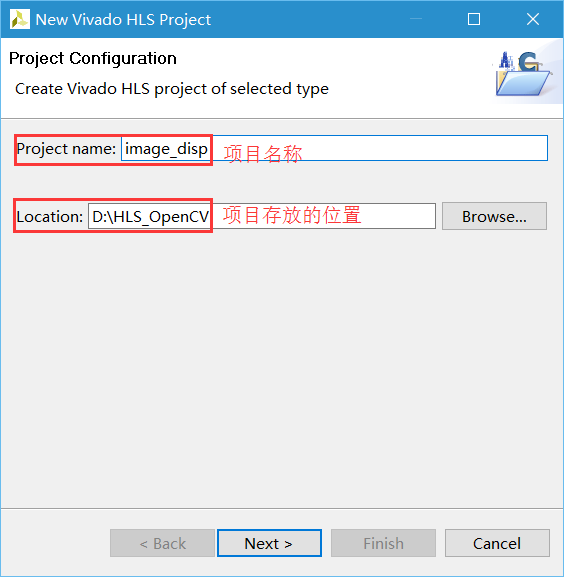

輸入項目的名稱和存放的位置;

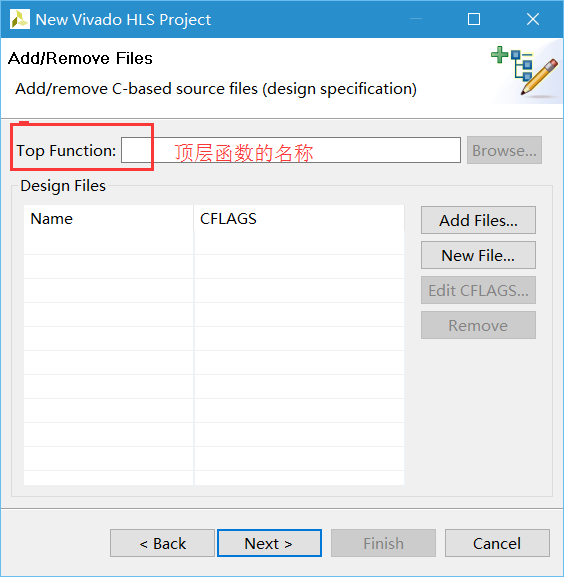

點擊下一步,輸入設計頂層函數的名稱,接著下一步;

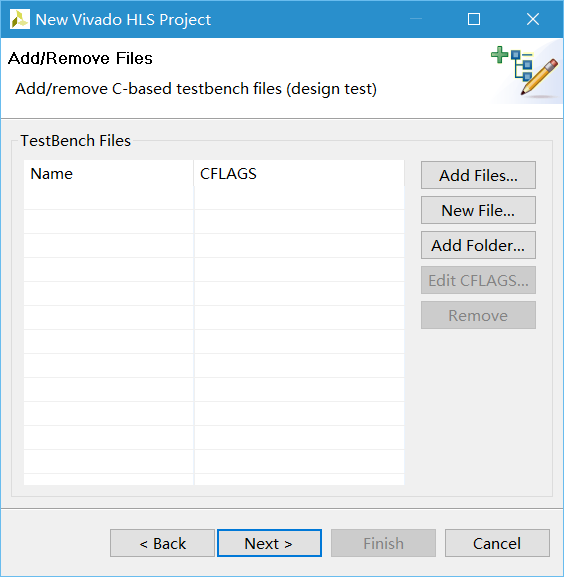

暫時不需要填寫,直接下一步;

解決方案的名字默認 (solution1)就好, 時鐘周期根據需要自己設,這里我設(10 ns), 時鐘的不確定性一般為12.5%,接著選擇器件,最后“finish”。

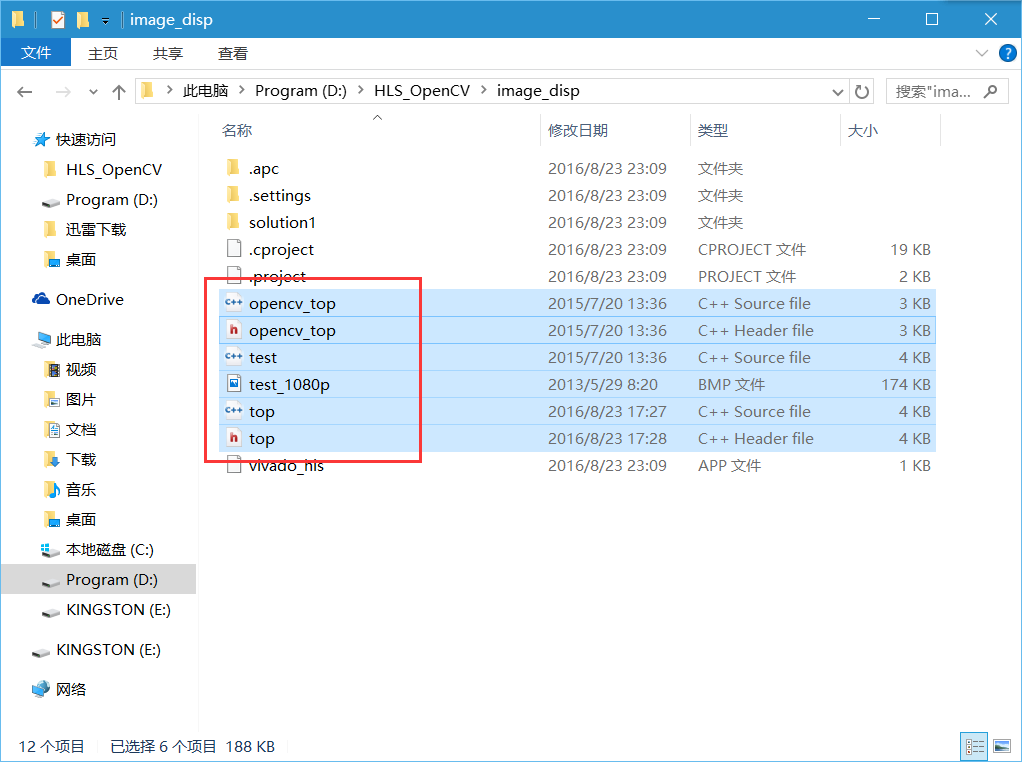

將該例程的設計文件和testbench全部復制到剛才創建的項目目錄下:

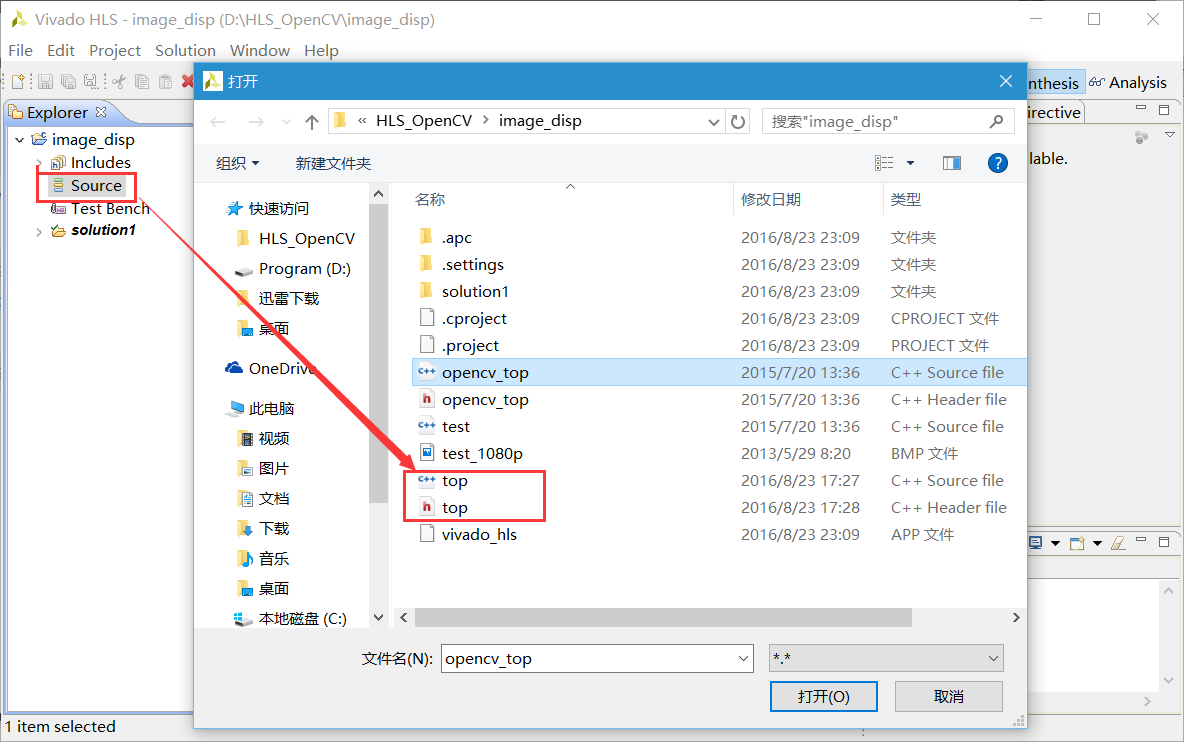

在設計資源窗口右擊“Source”,添加設計文件;

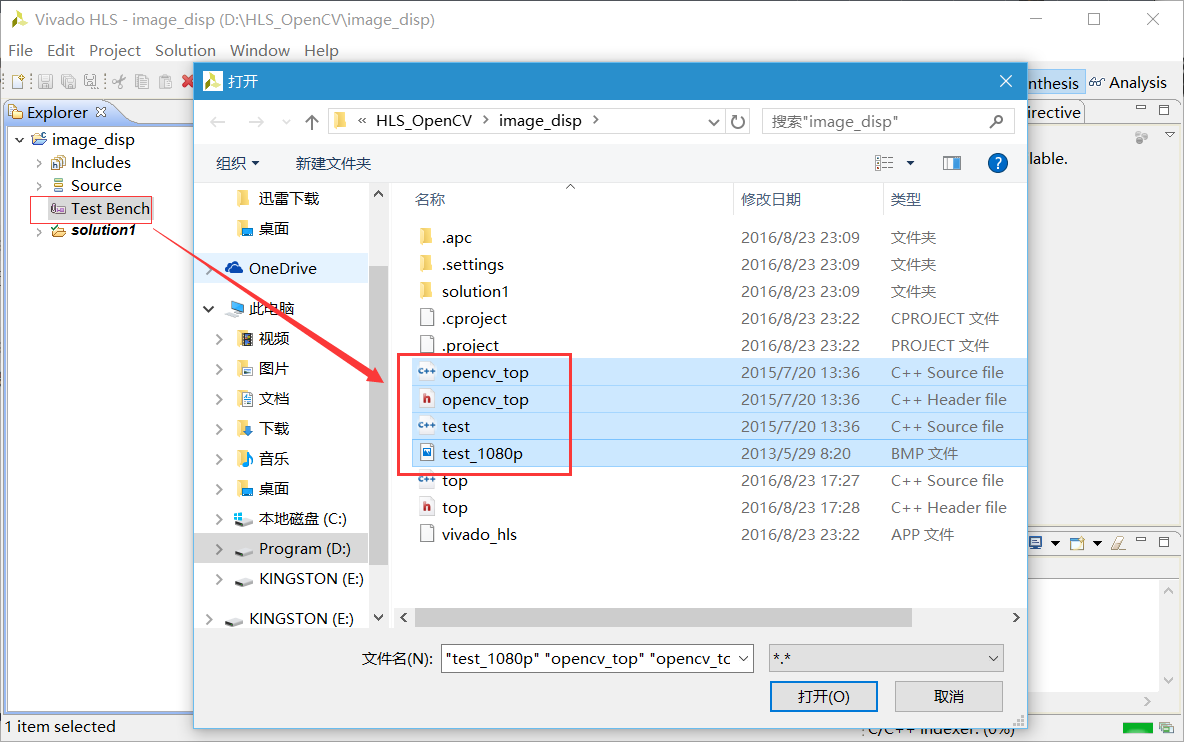

再接著右擊“Test Bench”,添加文件;

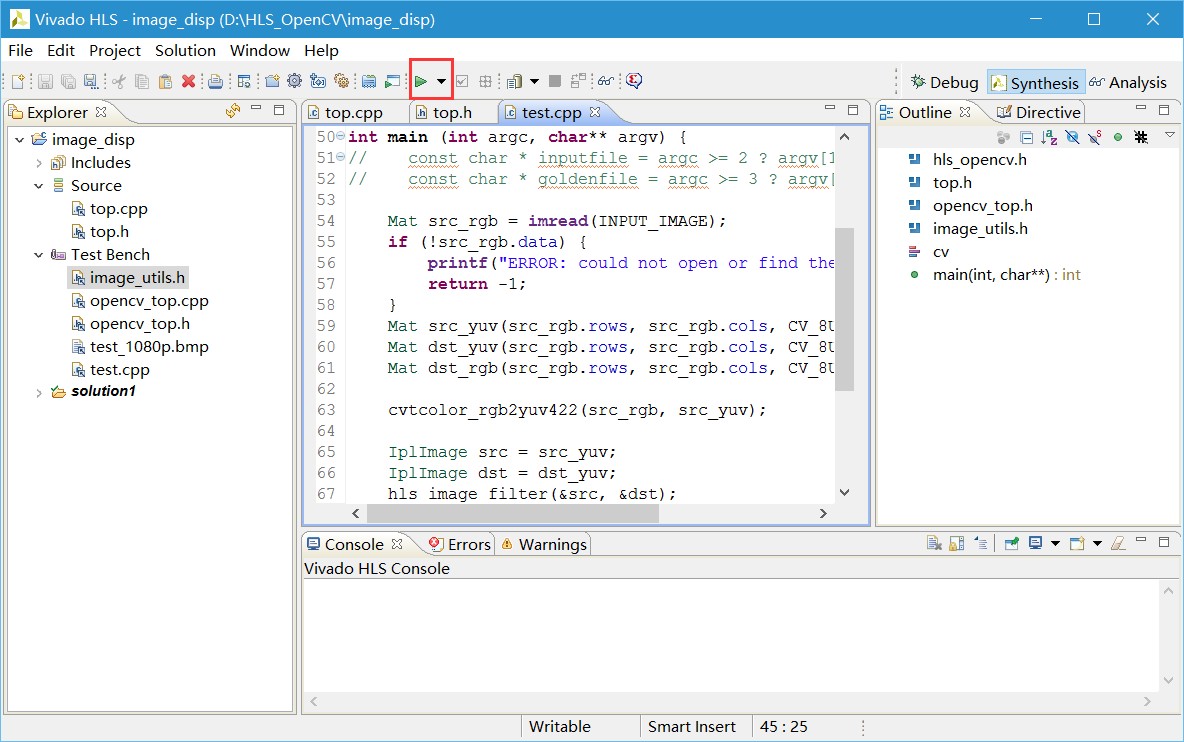

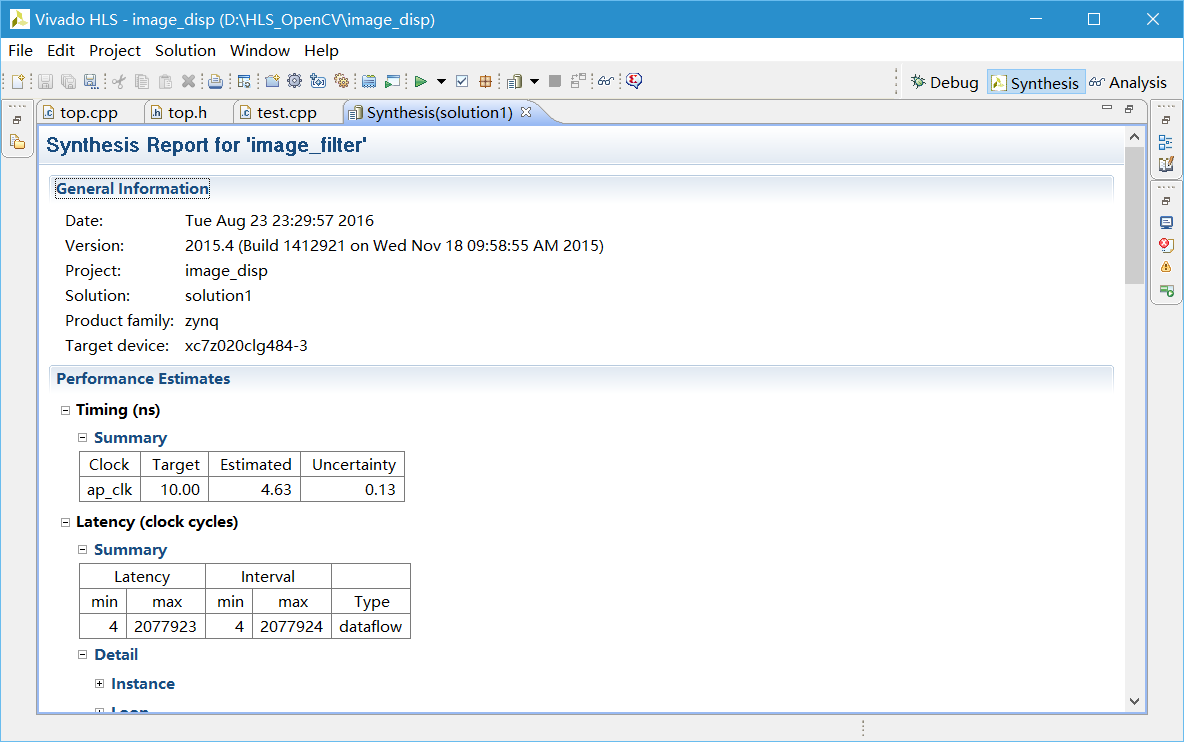

至此,項目建設完成。接著進行綜合仿真,驗證設計。 點擊“Run C Snthry”。

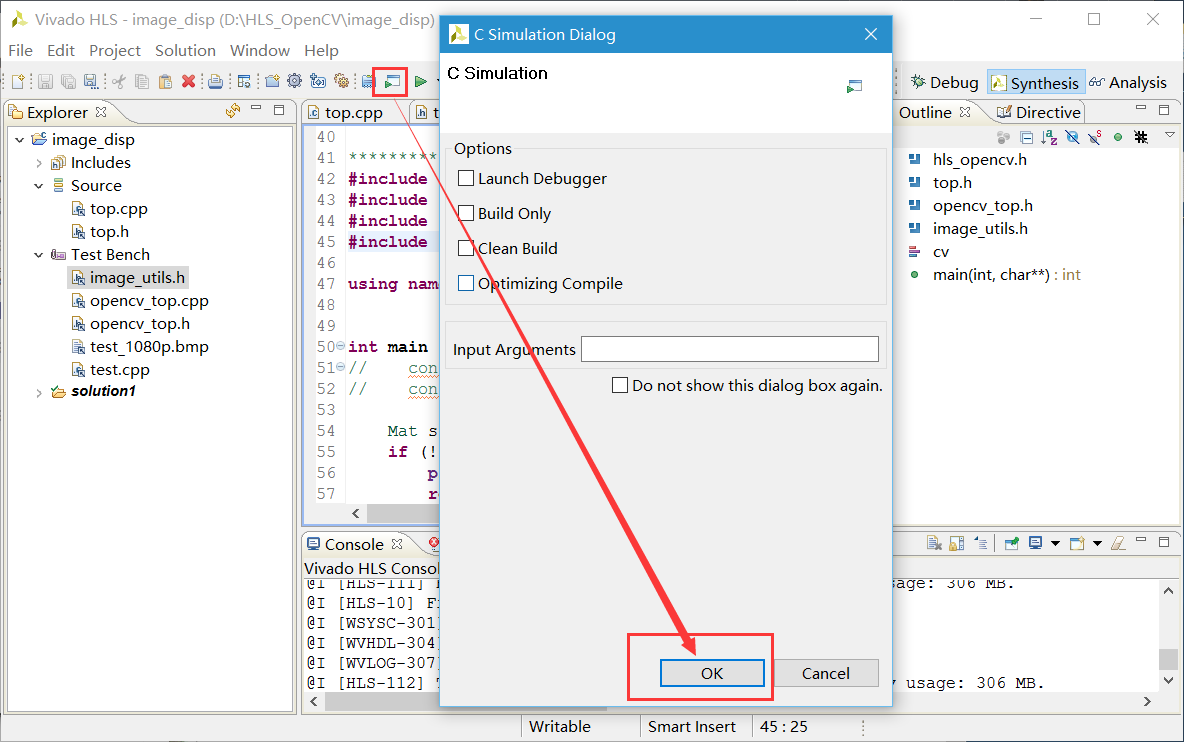

點擊“Run C Simulation”,接著點擊“OK”;

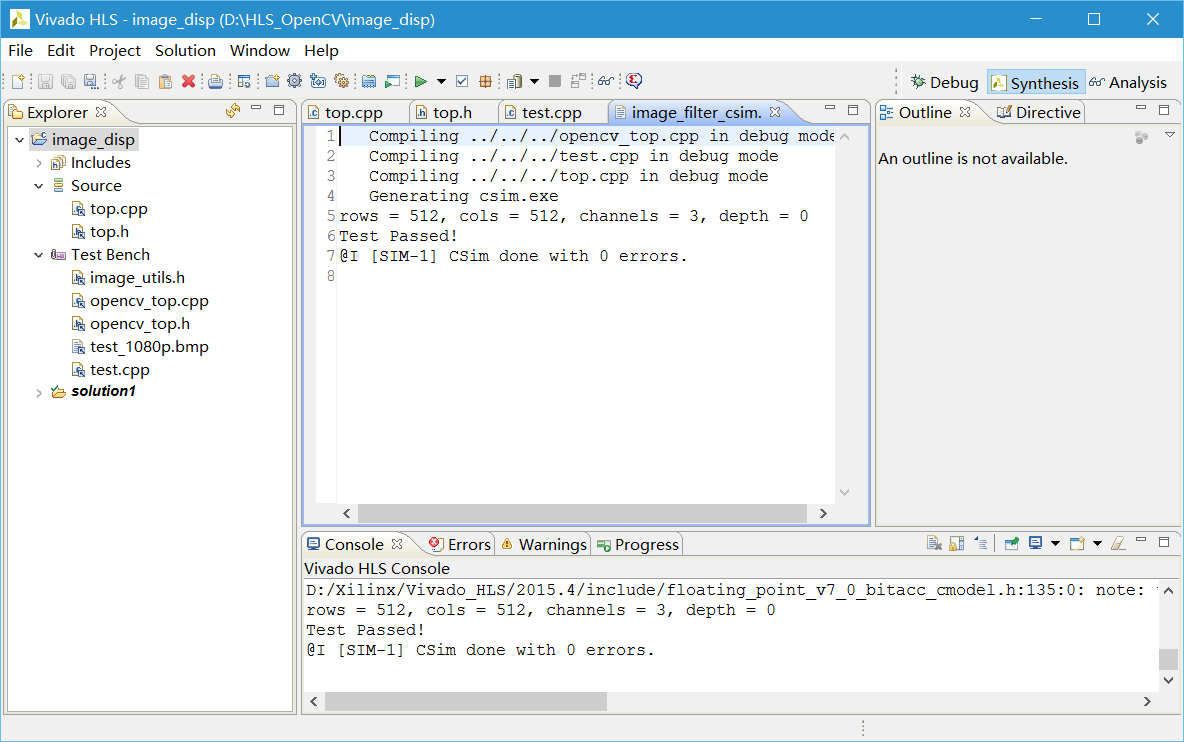

至此,此項目在沒有硬件調試的前提下算是成功運行了。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

HDL

+關注

關注

8文章

327瀏覽量

47424 -

模型

+關注

關注

1文章

3286瀏覽量

49009 -

Vivado

+關注

關注

19文章

815瀏覽量

66750

發布評論請先 登錄

相關推薦

從Level1 Model到Level3 Modle來感受器件模型是如何開發的

? ? ? ?本文從Level1 model到Level3 model的Ids電流公式的發展來感受Compact器件模型是如何開發的。 MOS技術擴展到納米尺寸,帶來了電路模擬器中器件

助力AIoT應用:在米爾FPGA開發板上實現Tiny YOLO V4

Darknet 上訓練的截圖

四、 通過 Vivado HLS 為 FPGA 準備模型要將模型部署到 FPGA,需要將神經網絡操作轉換為硬

發表于 12-06 17:18

Vivado使用小技巧

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

優化 FPGA HLS 設計

優化 FPGA HLS 設計

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

介紹

高級設計能夠以簡潔的方式捕獲設計,從而

發表于 08-16 19:56

一種在HLS中插入HDL代碼的方式

很多人都比較反感用C/C++開發(HLS)FPGA,大家第一拒絕的理由就是耗費資源太多。但是HLS也有自己的優點,除了快速構建算法外,還有一個就是接口的生成,尤其對于AXI類接口,按照

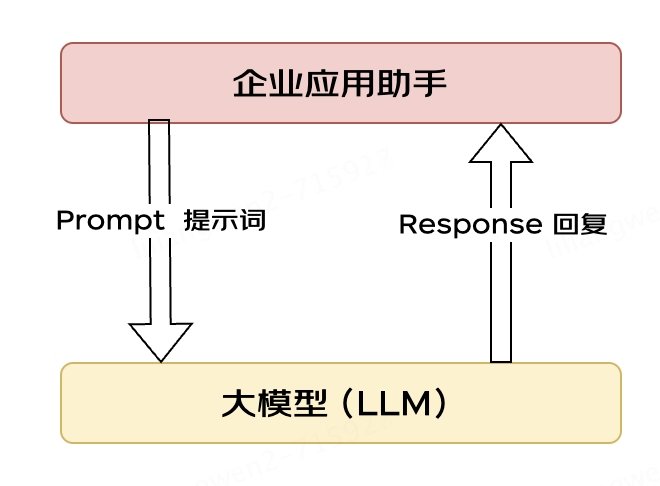

大模型應用之路:從提示詞到通用人工智能(AGI)

大模型在人工智能領域的應用正迅速擴展,從最初的提示詞(Prompt)工程到追求通用人工智能(AGI)的宏偉目標,這一旅程充滿了挑戰與創新。本文將探索大模型在實際應用中的進展,以及它們如

FPGA設計中 Verilog HDL實現基本的圖像濾波處理仿真

今天給大俠帶來FPGA設計中用Verilog HDL實現基本的圖像濾波處理仿真,話不多說,上貨。

1、用matlab代碼,準備好把圖片轉化成Vivado Simulator識別的格式,即每行一

發表于 05-20 16:44

簡談Xilinx Zynq-7000嵌入式系統設計與實現

、IO及其他外設、用于工業控制領域如嵌入式應用。

AP SoC的誕生背景:

在全可編程平臺設計階段,設計已經從傳統上以硬件描述語言HDL為中心的硬件邏輯設計,轉換到以C語言為代

發表于 05-08 16:23

Verilog到VHDL轉換的經驗與技巧總結

Verilog與VHDL語法是互通且相互對應的,如何查看二者對同一硬件結構的描述,可以借助EDA工具,如Vivado,打開Vivado后它里面的語言模板后,也可以對比查看Verilog和VHDL之間的差異。

Vivado 使用Simulink設計FIR濾波器

小于通帶內抖動值0.03db。

通過將輸入信號改為脈沖信號,脈沖寬度為1個周期,此時可觀測到此fir濾波器的沖擊響應。經過以上步驟,基本驗證此濾波器的設計能夠達到需求。

5. 將模型導入到

發表于 04-17 17:29

Vivado編譯常見錯誤與關鍵警告梳理與解析

Xilinx Vivado開發環境編譯HDL時,對時鐘信號設置了編譯規則,如果時鐘由于硬件設計原因分配到了普通IO上,而非_SRCC或者_MRCC專用時鐘管腳上時,編譯器就會提示錯誤。

簡談Xilinx Zynq-7000嵌入式系統設計與實現

應用。

AP SoC的誕生背景:

在全可編程平臺設計階段,設計已經從傳統上以硬件描述語言HDL為中心的硬件邏輯設計,轉換到以C語言為代表的軟件為中心的功能

發表于 04-10 16:00

# FPGA 編程如何工作?

Vivado? HLS 編譯器提供了一個與專用和標準處理器共享關鍵技術的編程環境,可優化基于 C 的程序。

=#6。= TensorFlow 和 PyTorch 等 AI 平臺

工程師使用Pytorch 或

發表于 03-30 11:50

Vivado HLS從HDL到模型和C的描述

Vivado HLS從HDL到模型和C的描述

評論