在前面的文章《FPGA工程師的核心競(jìng)爭(zhēng)力-學(xué)習(xí)篇(一)》中,提到要做一名合格的FPGA工程師,需要從底層做起,模塊編寫、工程搭建、系統(tǒng)開發(fā)、平臺(tái)架構(gòu)設(shè)計(jì),到系統(tǒng)級(jí)的軟硬件全棧能力。對(duì)于FPGA工程師而言,概括起來,日常工作主要集中于算法邏輯設(shè)計(jì)和接口驅(qū)動(dòng)設(shè)計(jì)。然而,從初級(jí)工程師到高級(jí)工程師,直至技術(shù)專家,不能永遠(yuǎn)停留在底層設(shè)計(jì),有了成熟的邏輯開發(fā)經(jīng)驗(yàn)后,需要往更高層次轉(zhuǎn)變,做系統(tǒng)級(jí)設(shè)計(jì),達(dá)到系統(tǒng)架構(gòu)師或總師的級(jí)別,這時(shí)候需要的是全局觀。

有沒有好的設(shè)計(jì)方法,可以讓工程師們走得更順利、更遠(yuǎn)呢?全球數(shù)十萬FPGA工程師正致力于讓系統(tǒng)設(shè)計(jì)更簡(jiǎn)單、更高效,具體怎樣開展呢?Xilinx隆重推出了UltraFast設(shè)計(jì)方法論。

關(guān)于UltraFast設(shè)計(jì)方法論

Xilinx推出的UltraFast設(shè)計(jì)方法論是一整套旨在幫助簡(jiǎn)化當(dāng)今器件設(shè)計(jì)進(jìn)程的最佳實(shí)踐。這些設(shè)計(jì)的規(guī)模與復(fù)雜性需要執(zhí)行特定的步驟與設(shè)計(jì)任務(wù),從而確保設(shè)計(jì)每個(gè)階段的成功開展。當(dāng)您遵循這些步驟和最佳實(shí)踐進(jìn)行操作,將有助于您盡可能最快且最高效的方式實(shí)現(xiàn)期望的設(shè)計(jì)目標(biāo)。

具體設(shè)計(jì)方法論是什么呢?這里提供設(shè)計(jì)指南:

(1)《UltraFast設(shè)計(jì)方法指南》(UG949),該指南中描述了各種設(shè)計(jì)任務(wù)、分析與報(bào)告功能,以及用于設(shè)計(jì)創(chuàng)建和收斂的最佳實(shí)踐。

(2)《UltraFast 設(shè)計(jì)方法快捷參考指南》(UG1231) 中采用易于使用的雙面卡格式著重講解了主要設(shè)計(jì)方法論步驟。

(3)《UltraFast 設(shè)計(jì)方法時(shí)序收斂快捷參考指南》(UG1292) 提供了有關(guān)時(shí)序收斂的建議,包括運(yùn)行初始設(shè)計(jì)檢查、設(shè)定設(shè)計(jì)基線和解決時(shí)序違例。

(4)《UltraFast 設(shè)計(jì)方法檢查表》(XTP301) 可從賽靈思 Documentation Navigator 獲取,也可作為獨(dú)立電子數(shù)據(jù)表獲取。您可使用此檢查表來識(shí)別整個(gè)設(shè)計(jì)進(jìn)程中的常見錯(cuò)誤和決策點(diǎn)。

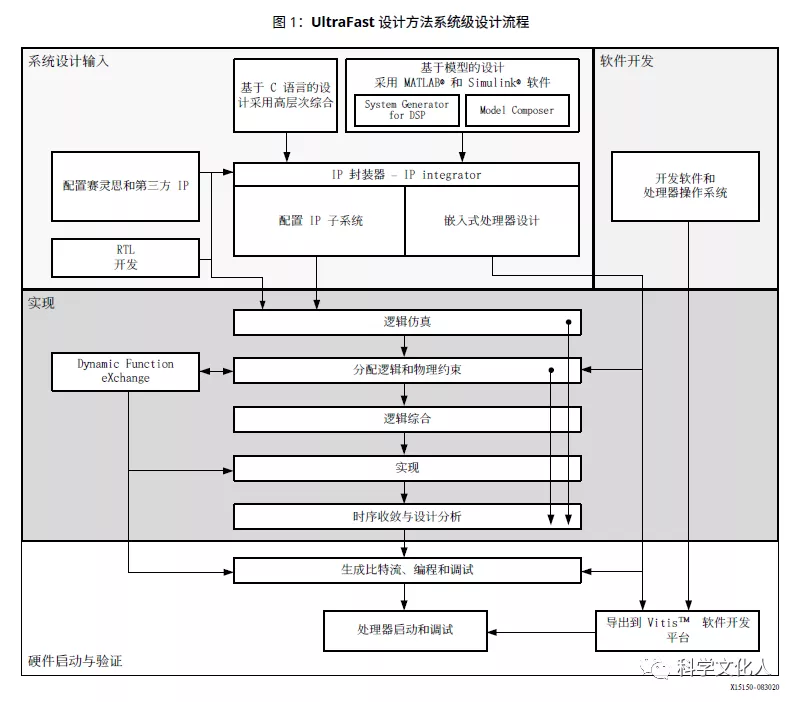

(5)《UltraFast 設(shè)計(jì)方法論系統(tǒng)級(jí)設(shè)計(jì)流程》圖展示了 賽靈思 Documentation Navigator 中提供的整個(gè) Vivado?Design Suite 設(shè)計(jì)流程。您可單擊圖中的設(shè)計(jì)步驟以打開相關(guān)文檔、宣傳材料以及常見問題及解答以幫助您入門。

另外建議:除上述資源外,賽靈思建議,處理嵌入式設(shè)計(jì)時(shí)請(qǐng)參閱《UltraFast 嵌入式設(shè)計(jì)方法指南》(UG1046),使用含基于 C 的 IP 的 Vivado IP integrator 開發(fā)復(fù)雜系統(tǒng)時(shí)請(qǐng)參閱《UltraFast Vivado HLS 方法指南》(UG1197)。

本文主要參考UG949,進(jìn)行重點(diǎn)闡述。在最新的UG949(2020版)中,共240頁,內(nèi)容主要分為6章,分別為:

?引言

?開發(fā)板和器件規(guī)劃

?利用RTL創(chuàng)建設(shè)計(jì)

?設(shè)計(jì)約束

?設(shè)計(jì)實(shí)現(xiàn)

?設(shè)計(jì)收斂

指點(diǎn)迷津:做任何事情,只講勤奮努力是不夠的,最重要的是找到好的方法可以高效完成任務(wù),這條真理,放之四海而皆準(zhǔn)。

引言

介紹UltraFast設(shè)計(jì)方法論,如何使用該指南,使用UltraFast設(shè)計(jì)方法檢查表,使用UltraFast設(shè)計(jì)方法論DRC,使用UltraFast設(shè)計(jì)方法系統(tǒng)級(jí)設(shè)計(jì)流程,以及了解UltraFast設(shè)計(jì)方法概念。

其中,使用UltraFast設(shè)計(jì)方法論進(jìn)行DRC,即設(shè)計(jì)規(guī)則檢查,個(gè)人覺得很重要,可以為后面節(jié)省不少時(shí)間。能在綜合和實(shí)現(xiàn)前搞定的東西,就別留在調(diào)試中去,不然累死了還找不到問題原因。

Vivado Design Suite 包含一組方法論相關(guān) DRC,可使用 report_methodology Tcl 命令來運(yùn)行。此命令針對(duì)以下每個(gè)設(shè)計(jì)階段都具有相應(yīng)的規(guī)則:

? 在綜合前,在細(xì)化 RTL 設(shè)計(jì)中用于驗(yàn)證 RTL 結(jié)構(gòu)

? 在綜合后,用于驗(yàn)證網(wǎng)表和約束

? 在實(shí)現(xiàn)后,用于驗(yàn)證約束和時(shí)序相關(guān)問題。

建議:為了最大限度發(fā)揮作用,請(qǐng)?jiān)诿總€(gè)設(shè)計(jì)階段運(yùn)行方法論DRC,并解決其中所有問題,然后再繼續(xù)執(zhí)行下一個(gè)階段。

TCL命令其實(shí)功能很強(qiáng)大,能完成所有界面引導(dǎo)操作,還能完成在界面引導(dǎo)不能勝任的操作。TCL的用戶指南為《Vivado Design Suite Tcl 命令參考指南》(UG835)。

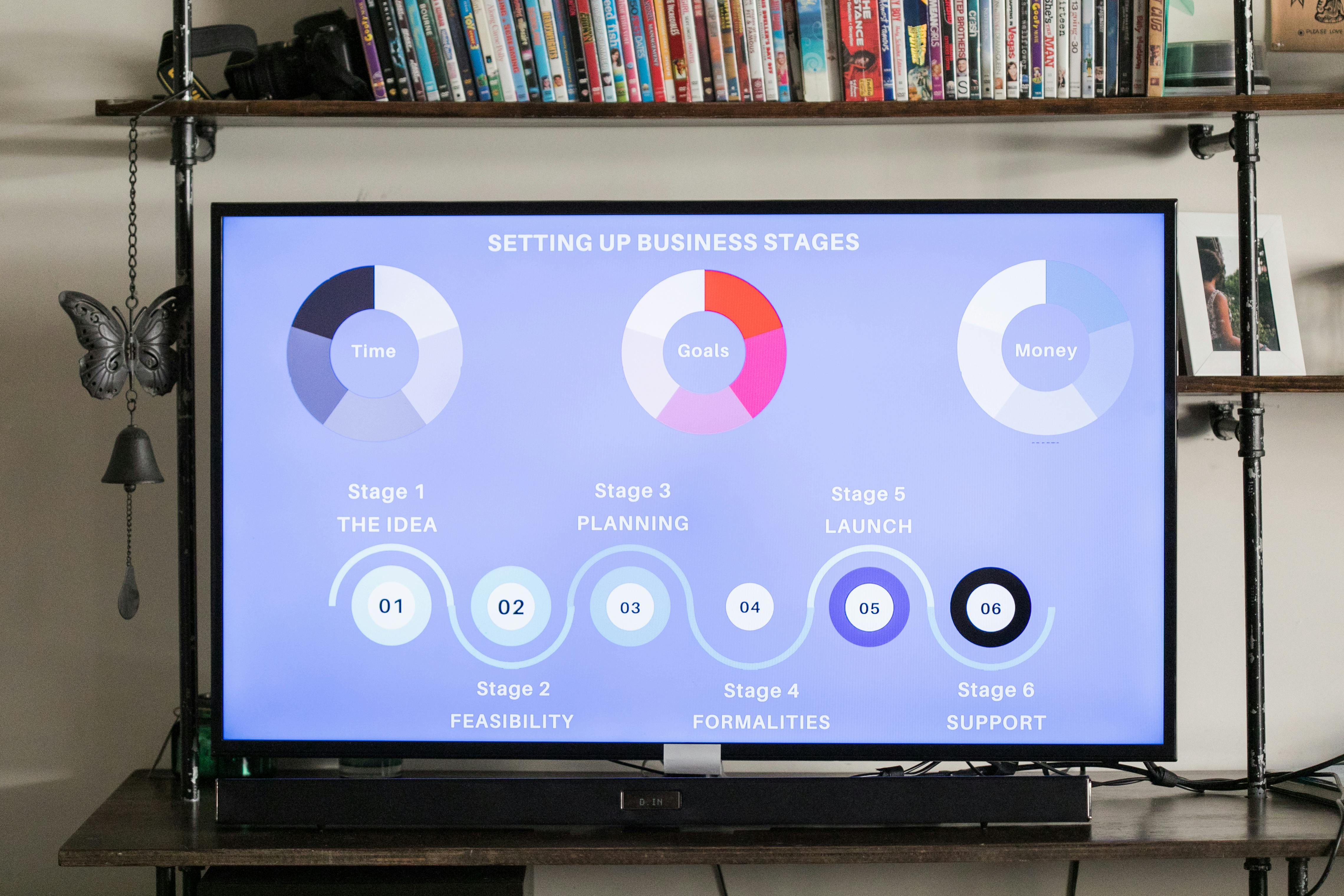

對(duì)于UltraFast設(shè)計(jì)方法系統(tǒng)級(jí)設(shè)計(jì)流程,用一張圖來表示最直觀:

在UltraFast 設(shè)計(jì)方法概念中,最重要的思想就是,從設(shè)計(jì)之初即采用正確方法并盡早關(guān)注設(shè)計(jì)目標(biāo)(包括 RTL、時(shí)鐘、管腳和 PCB 管腳分配)至關(guān)重要。在每個(gè)設(shè)計(jì)階段中正確定義和驗(yàn)證設(shè)計(jì)有助于減少后續(xù)實(shí)現(xiàn)階段的時(shí)序收斂、布線收斂和功耗問題。

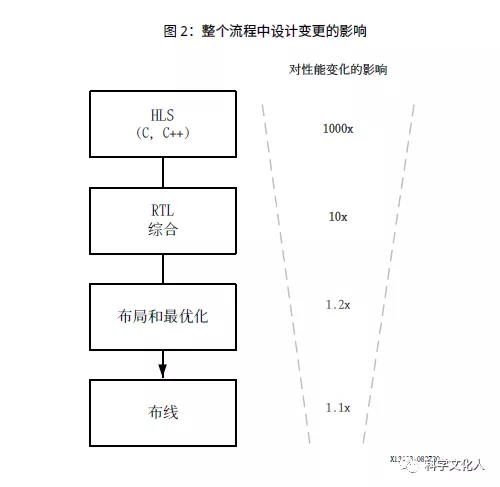

在開發(fā)周期早期,需要注意時(shí)序設(shè)計(jì)目標(biāo)。設(shè)計(jì)流程的早期階段(C、C++ 和 RTL 綜合)對(duì)于設(shè)計(jì)性能、密度和功耗的影響遠(yuǎn)超后期實(shí)現(xiàn)階段的影響。因此,如果設(shè)計(jì)不滿足時(shí)序目標(biāo),建議重新評(píng)估綜合階段(包括 HDL 和約束),而不是僅在實(shí)現(xiàn)階段通過迭代來尋找解決方案。圖2中關(guān)于HLS,高層次綜合,主要面對(duì)從事軟件開發(fā)人員,但是他想利用FPGA進(jìn)行工程設(shè)計(jì),說不定他不懂RTL,不懂HDL,因此采用高級(jí)語言C或C++來設(shè)計(jì)。

UltraFast設(shè)計(jì)方法強(qiáng)調(diào)對(duì)設(shè)計(jì)預(yù)算(例如,面積、功耗、時(shí)延和時(shí)序)進(jìn)行監(jiān)控以及盡早采取如下措施更正設(shè)計(jì)的重要性:

? 利用賽靈思模板創(chuàng)建最佳 RTL 結(jié)構(gòu),并在執(zhí)行細(xì)化后進(jìn)行綜合前采用方法 DRC 來驗(yàn)證 RTL。由于 Vivado 工具從始至終使用時(shí)序驅(qū)動(dòng)的算法,設(shè)計(jì)必須從設(shè)計(jì)流程開始就得到正確的約束。

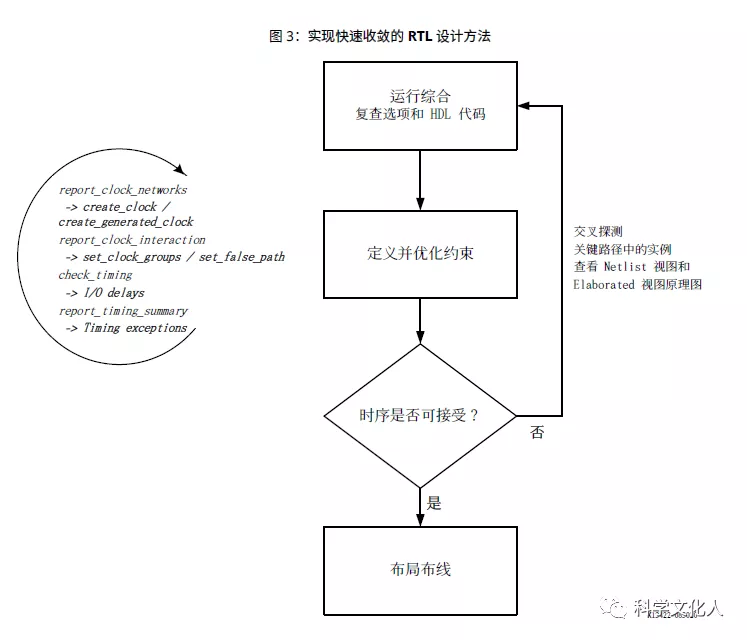

? 在綜合后開展時(shí)序分析。要指定正確的時(shí)序,您必須分析設(shè)計(jì)中每個(gè)主時(shí)鐘及有關(guān)生成時(shí)鐘之間的關(guān)系。在 Vivado 工具中,每次時(shí)鐘交互都必須滿足時(shí)序要求,除非顯式聲明為異步時(shí)鐘交互或偽路徑 (false path)。

? 在繼續(xù)執(zhí)行下一個(gè)設(shè)計(jì)階段前采用正確的約束滿足時(shí)序要求。可遵循如下建議并使用 Vivado Design Suite 的交互式分析環(huán)境來加速總體時(shí)序與實(shí)現(xiàn)收斂。

如能夠通過正時(shí)序裕度 (positive margin) 或相對(duì)較小的負(fù)時(shí)序裕度 (negative timing margin) 滿足設(shè)計(jì)目標(biāo),那么綜合即可視為完成。例如,如果綜合后未能滿足時(shí)序要求,那么布局布線結(jié)果也不太可能滿足時(shí)序要求。

時(shí)序違例對(duì)電路運(yùn)行會(huì)產(chǎn)生較大影響,很可能跑飛,導(dǎo)致邏輯混亂。關(guān)于時(shí)序約束,在UG949中會(huì)講到。另外,在UG612、UG625、UG903等也有講到進(jìn)行時(shí)序收斂和約束的方法。

開發(fā)板和器件規(guī)劃

正確規(guī)劃開發(fā)板上的器件朝向并向特定管腳分配信號(hào)可以顯著提升總體系統(tǒng)性能、降低功耗、提升散熱性能并縮短設(shè)計(jì)周期。將器件與印刷電路板 (PCB) 進(jìn)行物理或邏輯交互的方式以直觀方式展現(xiàn)出來,即可精簡(jiǎn)通過器件的數(shù)據(jù)流。

未正確規(guī)劃 I/O 配置則可能導(dǎo)致系統(tǒng)性能下降和設(shè)計(jì)收斂時(shí)間延長(zhǎng)。賽靈思強(qiáng)烈建議在考慮 I/O 管腳分配的同時(shí)進(jìn)行開發(fā)板級(jí)規(guī)劃。

當(dāng)然,對(duì)于從事邏輯算法開發(fā)的人員,不太關(guān)注器件規(guī)劃,硬件工程師一張?jiān)韴D和器件表扔過去就可以開始干活了。

這一章就不詳細(xì)說明了,去官網(wǎng)下載沒有興趣慢慢看吧。

利用RTL創(chuàng)建設(shè)計(jì)

完成器件 I/O 管腳分配、PCB 布局規(guī)劃并決定 Vivado? Design Suite 的使用模型后,即可開始創(chuàng)建設(shè)計(jì)。設(shè)計(jì)創(chuàng)建包括:

? 規(guī)劃設(shè)計(jì)的層級(jí)

? 識(shí)別要在設(shè)計(jì)中使用和定制的 IP 核

? 對(duì)于沒有合適的 IP 可用的互連邏輯和功能,請(qǐng)創(chuàng)建定制 RTL

? 創(chuàng)建時(shí)序約束、功耗約束和物理約束

? 指定綜合與實(shí)現(xiàn)階段所使用的其它約束、屬性及其它元件

創(chuàng)建設(shè)計(jì)時(shí),主要的考慮要素包括:

? 實(shí)現(xiàn)所需的功能

? 按期望的頻率運(yùn)行

? 按期望的可靠程度運(yùn)行

? 符合硅片資源和功耗預(yù)算要求

在此階段做出的決策將影響最終產(chǎn)品。在這一階段的錯(cuò)誤決策會(huì)導(dǎo)致后續(xù)階段問題層出不窮,進(jìn)而造成整個(gè)設(shè)計(jì)周期中不斷返工。在此過程中盡早花時(shí)間詳細(xì)規(guī)劃設(shè)計(jì)有助于達(dá)成設(shè)計(jì)目標(biāo)并最大限度縮短實(shí)驗(yàn)室中的調(diào)試時(shí)間。

特別是開始一個(gè)新的項(xiàng)目時(shí),這一步實(shí)在是太重要了。我們講究邏輯,沒有邏輯的世界是飄渺的,會(huì)導(dǎo)致矛盾重重,做事效率低,漏洞百出。

1.定義理想的設(shè)計(jì)層級(jí)

設(shè)計(jì)創(chuàng)建的第一步是決定如何對(duì)設(shè)計(jì)進(jìn)行邏輯分區(qū)。定義層級(jí)時(shí)主要考慮的是如何對(duì)含特定功能的設(shè)計(jì)部分進(jìn)行分區(qū)。

這樣便于特定設(shè)計(jì)人員單獨(dú)設(shè)計(jì) IP,以及隔離一段代碼以供復(fù)用。

說白一點(diǎn),就是功能模塊劃分。一個(gè)完整的功能系統(tǒng),總是由若干個(gè)功能單元構(gòu)成,就好比一個(gè)人,眼、耳、口、鼻、四肢、內(nèi)臟、肌肉,各司其職,同時(shí)又協(xié)同工作。

但僅根據(jù)功能來確定層級(jí)會(huì)導(dǎo)致對(duì)時(shí)序收斂、運(yùn)行時(shí)間和調(diào)試的最優(yōu)化方法考慮不周。在層級(jí)規(guī)劃過程考慮如下因素也有助于時(shí)序收斂。

1.1 在頂層附近添加 I/O 組件

盡可能在頂層附近添加 I/O 組件,以保障設(shè)計(jì)可讀性。推斷組件時(shí),請(qǐng)?zhí)峁┮瓿晒δ艿拿枋觥H缓螅C合工具會(huì)對(duì)HDL 代碼進(jìn)行解釋,以確定使用哪些硬件組件來執(zhí)行該功能。可推斷的組件為簡(jiǎn)單的單端 I/O(IBUF、OBUF、OBUFT 和 IOBUF)以及 I/O 中的單數(shù)據(jù)速率寄存器。

1.2 在頂層附近插入時(shí)鐘元件

朝頂層方向插入時(shí)鐘元件便于模塊間的時(shí)鐘共享。時(shí)鐘共享可以減少時(shí)鐘資源占用,從而提高資源利用率,提升性能,并降低功耗。除了在其中創(chuàng)建時(shí)鐘的模塊之外,時(shí)鐘路徑只能向下驅(qū)動(dòng)進(jìn)入模塊。任何先自上而下而后又自下而上貫穿的路徑都會(huì)在VHDL 仿真中造成 delta cycle 問題,此類問題的調(diào)試既艱難又費(fèi)時(shí)。

1.3 在邏輯邊界處寄存數(shù)據(jù)路徑

對(duì)層級(jí)邊界輸出進(jìn)行寄存可將關(guān)鍵路徑包含在單一模塊或邊界內(nèi)。輸入同樣可以寄存在層級(jí)邊界處。相比于遍布多個(gè)模塊的路徑,模塊內(nèi)部的時(shí)序路徑始終更便于分析和修復(fù)。未在層級(jí)邊界處寄存的任何路徑都應(yīng)采用層級(jí)重構(gòu)來加以綜合或者扁平化以便實(shí)現(xiàn)跨層級(jí)最優(yōu)化。在邏輯邊界處寄存數(shù)據(jù)路徑有助于保留整個(gè)設(shè)計(jì)進(jìn)程中的可追溯性(用于調(diào)試),因?yàn)檫@樣可以最大限度避免跨層級(jí)最優(yōu)化,并且邏輯不會(huì)跨模塊遷移。

模塊之間有交互,當(dāng)一個(gè)模塊的輸出信號(hào)送入下一個(gè)模塊時(shí),最好通過寄存再輸出。同樣,很多時(shí)候?yàn)榱吮苊饪鐣r(shí)鐘處理以及模塊復(fù)用,會(huì)對(duì)輸入信號(hào)進(jìn)行打拍處理。

1.4 針對(duì)功能和時(shí)序調(diào)試最優(yōu)化層級(jí)

把關(guān)鍵路徑限定在同一層級(jí)邊界內(nèi)有助于時(shí)序的調(diào)試和滿足時(shí)序要求。同樣,出于功能調(diào)試(及修改)目的,相關(guān)信號(hào)應(yīng)限定在同一層級(jí)上。這樣即可使相關(guān)信號(hào)的探測(cè)和修改變得相對(duì)簡(jiǎn)單,因?yàn)楫?dāng)信號(hào)限定在單個(gè)層級(jí)中時(shí),更易于跟蹤通過綜合對(duì)信號(hào)名稱進(jìn)行的最優(yōu)化。

2.IP 的使用

使用預(yù)先驗(yàn)證的 IP 核能夠大幅減少設(shè)計(jì)和驗(yàn)證工作量,從而加速產(chǎn)品上市進(jìn)程。如需了解有關(guān)使用 IP 的更多信息,請(qǐng)參閱以下資源:

? 《Vivado Design Suite 用戶指南:采用 IP 進(jìn)行設(shè)計(jì)》(UG896)

? 《Vivado Design Suite 用戶指南:采用 IP integrator 設(shè)計(jì) IP 子系統(tǒng)》(UG994)

? Vivado Design Suite QuickTake 視頻:在 Vivado 中配置和管理可復(fù)用 IP

當(dāng)然,有時(shí)候我們對(duì)第三方IP不放心,自己進(jìn)行IP開發(fā)和封裝,方便移植和復(fù)用。

2.1 規(guī)劃IP要求

根據(jù)所需功能以及其它設(shè)計(jì)目標(biāo),評(píng)估賽靈思或其它第三方合作伙伴提供的 IP 選項(xiàng)。

考慮需要使用的接口,例如,存儲(chǔ)器接口、網(wǎng)絡(luò)接口和外設(shè)接口。

2.2 AMBA AXI

AXI4 專為高性能、高時(shí)鐘頻率系統(tǒng)設(shè)計(jì)制定,適用于高速互連。

AXI4-Lite 是 AXI4 的精簡(jiǎn)版,主要用于訪問控制寄存器和狀態(tài)寄存器。

AXI4-Stream 用于從主接口到從接口的單向數(shù)據(jù)流。典型應(yīng)用包括 DSP、視頻和通信。

用的最多的算是AXI4-Stream,接口和時(shí)序簡(jiǎn)單,比較方便使用。

關(guān)于如何使用IP,就不贅述了,本文的長(zhǎng)度已經(jīng)可以預(yù)感,會(huì)比較長(zhǎng)。

3 RTL 編碼指南

可創(chuàng)建定制 RTL 來實(shí)現(xiàn)膠合邏輯功能以及不含適合 IP 的功能。

創(chuàng)建 RTL 或例化賽靈思原語時(shí)使用 Vivado Design Suite 語言模板。這些語言模板包含建議的編碼結(jié)構(gòu),用于正確推斷賽靈思器件架構(gòu)。使用語言模板可以簡(jiǎn)化設(shè)計(jì)進(jìn)程,并改進(jìn)結(jié)果。要從 Vivado IDE 打開“語言模板”,請(qǐng)選擇“Flow Navigator”中的“Language Templates”選項(xiàng),然后選擇所需模板。

在工程開發(fā)中,我本人其實(shí)沒有這樣做,習(xí)慣于自己創(chuàng)建文件,定義接口,然后進(jìn)行邏輯設(shè)計(jì)。當(dāng)然,好的方法我們要虛心學(xué)習(xí)借鑒。關(guān)注FPGA器件映射的本質(zhì),也許會(huì)有助于進(jìn)行RTL設(shè)計(jì)。

3.1 控制信號(hào)和控制集

控制集是控制信號(hào)(置位/復(fù)位信號(hào)、時(shí)鐘使能信號(hào)和時(shí)鐘信號(hào))的組合,用于驅(qū)動(dòng)任意給定 SRL、LUTRAM 或寄存器。對(duì)于控制信號(hào)的任意獨(dú)特組合,都會(huì)組成 1 個(gè)獨(dú)立控制集。由于 7 系列 slice 中的寄存器全部共享公用控制信號(hào),導(dǎo)致只能將含公用控制集的寄存器封裝到相同 slice 中,因此該功能十分重要。例如,如果具有給定控制集的寄存器僅具有 1 個(gè)寄存器作為負(fù)載,那么其占據(jù)的 slice 中的另 7 個(gè)寄存器將變?yōu)椴豢捎谩?/p>

復(fù)位

復(fù)位是需要在設(shè)計(jì)中考慮并加以限制的較為常見且重要的控制信號(hào)之一。復(fù)位會(huì)對(duì)設(shè)計(jì)的性能、面積和功耗產(chǎn)生顯著影響。

多路復(fù)用器的輸入輸出中所描述的異步復(fù)位可能導(dǎo)致將寄存器放置到 slice 中而不是放置到 DSP 塊中。在此類情況下,將使用額外邏輯資源,從而對(duì)功耗和設(shè)計(jì)性能產(chǎn)生負(fù)面影響。

使用復(fù)位的時(shí)間和位置

賽靈思器件具有專用的全局置位/復(fù)位信號(hào) (GSR)。在器件配置結(jié)束時(shí),此信號(hào)會(huì)設(shè)置硬件中所有時(shí)序單元的初始值。

謹(jǐn)慎判斷何時(shí)設(shè)計(jì)需要復(fù)位以及何時(shí)不需要復(fù)位。大多數(shù)情況下,在控制路徑邏輯上可能需要復(fù)位以確保正常運(yùn)行。然而在數(shù)據(jù)路徑邏輯上通常不需要復(fù)位。復(fù)位的使用限制如下:

? 限制復(fù)位信號(hào)線的總體扇出。

? 減少?gòu)?fù)位布線所需的互連數(shù)量。

? 簡(jiǎn)化復(fù)位路徑的時(shí)序。

? 在大多數(shù)情況下,這樣即可整體改進(jìn)性能、面積和功耗。

同步復(fù)位對(duì)比異步復(fù)位

如需復(fù)位,賽靈思建議使用同步復(fù)位。同步復(fù)位相比于異步復(fù)位具有諸多優(yōu)勢(shì)。詳細(xì)說明,參考UG949。

3.2 掌握推斷的結(jié)果

代碼最終必須映射到器件中存在的資源上。請(qǐng)盡力理清所處理的關(guān)鍵架構(gòu)中的關(guān)鍵算法、存儲(chǔ)和邏輯元件。這樣在對(duì)設(shè)計(jì)功能進(jìn)行編碼時(shí),即可預(yù)測(cè)代碼將映射到的硬件資源。

3.3 有助于提升性能的編碼方式

關(guān)鍵路徑上的高扇出

高扇出信號(hào)線在設(shè)計(jì)進(jìn)程早期階段更便于處理。性能要求和路徑的結(jié)構(gòu)往往會(huì)導(dǎo)致高扇出問題。

流水線設(shè)置注意事項(xiàng)

另一種提升性能的方法是對(duì)具有多個(gè)邏輯層次的長(zhǎng)數(shù)據(jù)路徑進(jìn)行重構(gòu)并將其分布在多個(gè)時(shí)鐘周期中。此方法可加速時(shí)鐘周期并增加數(shù)據(jù)吞吐量,但代價(jià)是時(shí)延和流水線開銷邏輯管理工作增加。

自動(dòng)流水線設(shè)置注意事項(xiàng)

可以選擇在布局期間插入額外的流水線寄存器,以解決特定總線和接口上的時(shí)序收斂難題。

3.4 提升功耗的編碼方式

?時(shí)鐘或數(shù)據(jù)路徑門控

?最大限度增加門控元件數(shù)量

?使用專用時(shí)鐘緩存的時(shí)鐘使能管腳

?無需優(yōu)先級(jí)編碼器時(shí)使用 Case 塊

由于篇幅較長(zhǎng),先到此為止,下篇我們將針對(duì)設(shè)計(jì)約束、設(shè)計(jì)實(shí)現(xiàn)和設(shè)計(jì)收斂進(jìn)行學(xué)習(xí)分析。

參考文獻(xiàn)

[1]Xiinx ,《UltraFast設(shè)計(jì)方法指南》(UG949)。

審核編輯:符乾江

-

FPGA

+關(guān)注

關(guān)注

1629文章

21754瀏覽量

604203 -

編碼

+關(guān)注

關(guān)注

6文章

946瀏覽量

54869

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

芯和半導(dǎo)體榮獲2024上海軟件核心競(jìng)爭(zhēng)力企業(yè)

中國(guó)AI企業(yè)創(chuàng)新降低成本打造競(jìng)爭(zhēng)力模型

Keysight助力提升工程師的測(cè)試測(cè)量知識(shí)水平

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

學(xué)習(xí)SOLIDWORKS提高學(xué)生的就業(yè)競(jìng)爭(zhēng)力

硬件工程師業(yè)余時(shí)間變現(xiàn),應(yīng)該從何處入手?

嵌入式軟件工程師如何提升自己?

干硬件這一行,各種辛酸只有同行才懂吧 ? #電路設(shè)計(jì) #電子愛好者 #硬件工程師 #電子工程師

安筱鵬:AI大模型重構(gòu)產(chǎn)業(yè)競(jìng)爭(zhēng)力的五種模式

數(shù)據(jù)中臺(tái):如何構(gòu)建企業(yè)核心競(jìng)爭(zhēng)力

FPGA工程師的核心競(jìng)爭(zhēng)力 - 方法篇(一)

FPGA工程師的核心競(jìng)爭(zhēng)力 - 方法篇(一)

評(píng)論