二、輸出(并-轉-串)邏輯資源

7系列設備中的OSERDESE2是專用的 并-轉-串 轉換器,使用特定的時鐘和邏輯資源設計來使得高速源同步接口實現變得容易。每個OSERDESE2模塊都包含一個特定的串化器(serializer)用于數據和三態(3-state)控制。數據和3態(3-state)串化器都可以配置成SDR和DDR模式。數據串行化的位寬可以達到8:1(如果使用原語模塊級聯,則可以到10:1和14:1)。3態的串行化最高可達14:1,有一個專用的DDR3模式可用于支持高速內存應用程序。

The OSERDESE2 in 7 series devices is a dedicated parallel-to-serial converter with specific

clocking and logic resources designed to facilitate the implementation of high-speed

source-synchronous interfaces. Every OSERDESE2 module includes a dedicated serializer

for data and 3-state control. Both data and 3-state serializers can be configured in SDR and

DDR mode. Data serialization can be up to 8:1 (10:1 and 14:1 if using OSERDESE2 Width

Expansion). 3-state serialization can be up to 14:1. There is a dedicated DDR3 mode to

support high-speed memory applications.

Figure 3-13 shows a block diagram of the OSERDESE2, highlighting all the major

components and features of the block.

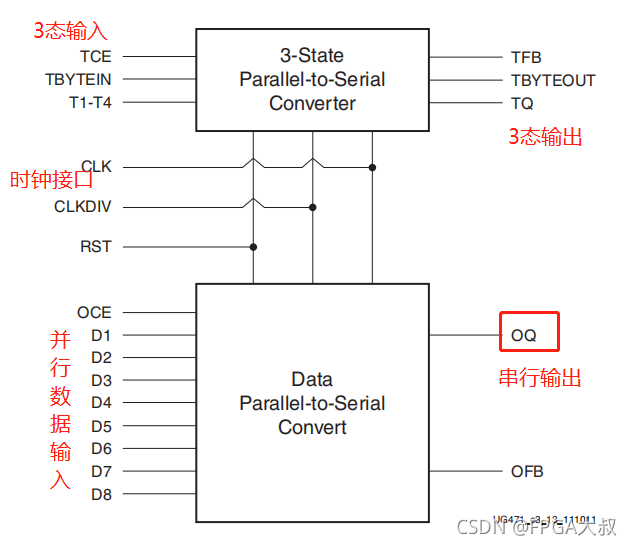

下圖是 OSERDESE2的模塊圖,顯示了主要的組成部件和特性:

2.1數據(并-轉-串)轉換器

在一個OSERDESE2塊中,數據(并-轉-串)轉換器接收2-8位的并行數據 (14位:使用OSERDESE2 位寬擴展),將數據串行化,然后通過OQ輸出接口傳遞給IOB。并行數據串行化是從從最低位開始。也就是說:從D1管腳輸入的數據最先傳輸到OQ輸出管腳。數據并串轉換器支持兩種模式:SDR和DDR。

OSERDESE2數據比率轉換使用兩個時鐘:CLK 和 CLKDIV。CLK是高度的串行時鐘,CLKDIV是分頻并行時鐘。CLK和CLKDIV必須相位對齊。

在使用之前,必須對OSERDESE2進行復位操作。OSERDESE2包含一個內部計數器用來控制數據流。如果沒有成功對復位同步(CLKDIV時鐘域)釋放,則會引起非預期的輸出。

The data parallel-to-serial converter in one OSERDESE2 blocks receives two to eight bits of

parallel data from the fabric (14 bits if using OSERDESE2 Width Expansion), serializes the

data, and presents it to the IOB via the OQ outputs. Parallel data is serialized from lowest

order data input pin to highest (i.e., data on the D1 input pin is the first bit transmitted at

the OQ pins). The data parallel-to-serial converter is available in two modes: single-data

rate (SDR) and double-data rate (DDR).

The OSERDESE2 uses two clocks, CLK and CLKDIV, for data rate conversion. CLK is the

high-speed serial clock, CLKDIV is the divided parallel clock. CLK and CLKDIV must be

phase aligned. See OSERDESE2 Clocking Methods.

Prior to use, a reset must be applied to the OSERDESE2. The OSERDESE2 contains an

internal counter that controls dataflow. Failure to synchronize the reset deassertion with

the CLKDIV will produce an unexpected output

2.2 3-State Parallel-to-Serial Conversion

除了數據的并串轉換之外,一個OSERDESE2模塊還包含了一個3態并串轉換器。與數據的并串轉換不同,3態轉換器串行化最高只能支持4位的并行3態信號。3態轉換器不能進行級聯。

In addition to parallel-to-serial conversion of data, an OSERDESE2 module also contains a

parallel-to-serial converter for 3-state control of the IOB. Unlike data conversion, the

3-state converter can only serialize up to four bits of parallel 3-state signals. The 3-state

converter cannot be cascaded.

三、OSERDESE2原語介紹

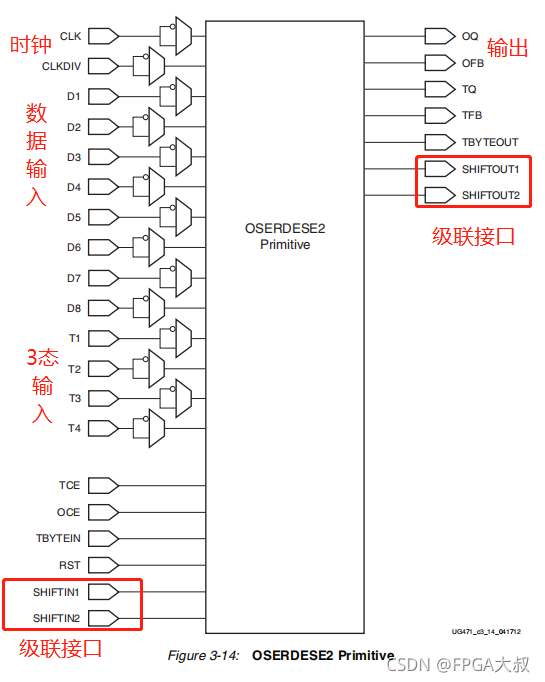

3.1 OSERDESE2框圖

3.2 OSERDESE2例化

掃一眼,直接看3.3

OSERDESE2 #(

.DATA_RATE_OQ("DDR"), // DDR, SDR

.DATA_RATE_TQ("DDR"), // DDR, BUF, SDR

.DATA_WIDTH(4), // Parallel data width (2-8,10,14)

.INIT_OQ(1'b0), // Initial value of OQ output (1'b0,1'b1)

.INIT_TQ(1'b0), // Initial value of TQ output (1'b0,1'b1)

.SERDES_MODE("MASTER"), // MASTER, SLAVE

.SRVAL_OQ(1'b0), // OQ output value when SR is used (1'b0,1'b1)

.SRVAL_TQ(1'b0), // TQ output value when SR is used (1'b0,1'b1)

.TBYTE_CTL("FALSE"), // Enable tristate byte operation (FALSE, TRUE)

.TBYTE_SRC("FALSE"), // Tristate byte source (FALSE, TRUE)

.TRISTATE_WIDTH(4) // 3-state converter width (1,4)

)

OSERDESE2_inst (

.OFB(OFB), // 1-bit output: Feedback path for data

.OQ(OQ), // 1-bit output: Data path output

// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each)

.SHIFTOUT1(SHIFTOUT1),

.SHIFTOUT2(SHIFTOUT2),

.TBYTEOUT(TBYTEOUT), // 1-bit output: Byte group tristate

.TFB(TFB), // 1-bit output: 3-state control

.TQ(TQ), // 1-bit output: 3-state control

.CLK(CLK), // 1-bit input: High speed clock

.CLKDIV(CLKDIV), // 1-bit input: Divided clock

// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each)

.D1(D1),

.D2(D2),

.D3(D3),

.D4(D4),

.D5(D5),

.D6(D6),

.D7(D7),

.D8(D8),

.OCE(OCE), // 1-bit input: Output data clock enable

.RST(RST), // 1-bit input: Reset

// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each)

.SHIFTIN1(SHIFTIN1),

.SHIFTIN2(SHIFTIN2),

// T1 - T4: 1-bit (each) input: Parallel 3-state inputs

.T1(T1),

.T2(T2),

.T3(T3),

.T4(T4),

.TBYTEIN(TBYTEIN), // 1-bit input: Byte group tristate

.TCE(TCE) // 1-bit input: 3-state clock enable

);

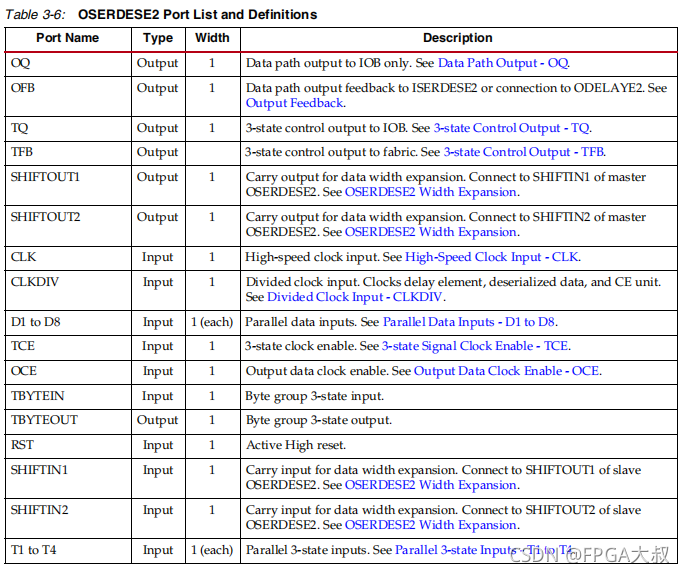

3.3 OSERDESE2端口

為了便于查看,后文對端口的進一步介紹一并寫到表格。

下圖為原文:

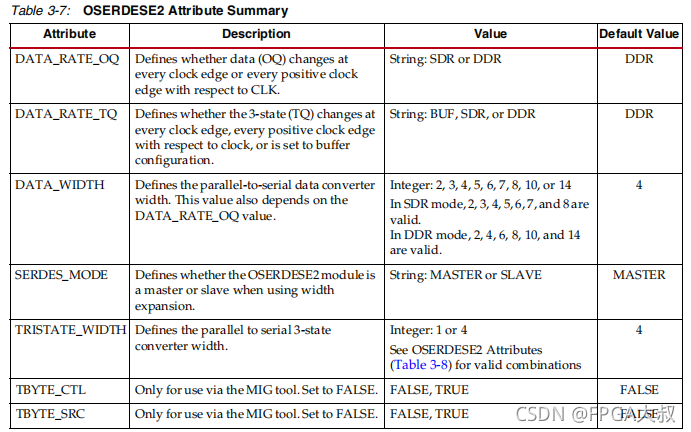

3.4 OSERDESE2屬性

下圖為原文:

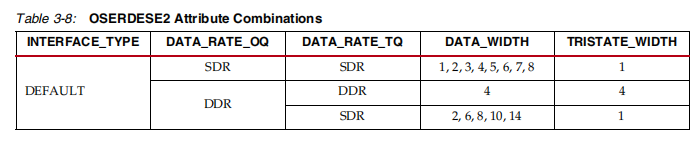

下圖為OSERDESE2屬性組合:

3.5 OSERDESE2時鐘

在并轉串過程中,CLK和 CLKDIV的相位關系是非常重要的。理想情況下,CLK和 CLKDIV是相位對齊的。在FPGA中有好幾種時鐘設置方式來幫助設計滿足CLK和 CLKDIV的相位關系要求。對于OSERDESE2來說,只有一種是有效的:

- CLK由BUFIO驅動,CLKDIV由BUFR驅動

- CLK和CLKDIV由同一個MMCM或PLL驅動 (常用)

當使用一個MMCM來驅動OSERDESE2的CLK 和CLKDIV時,buffer類型不能混用。舉個栗子:如果CLK由BUFG驅動,CLKDIV也必須由BUFG驅動。

The phase relationship of CLK and CLKDIV is important in the parallel-to-serial

conversion process. CLK and CLKDIV are (ideally) phase-aligned within a tolerance.

There are several clocking arrangements within the FPGA to help the design meet the

phase relationship requirements of CLK and CLKDIV. The only valid clocking

arrangements for the OSERDESE2 are:

? CLK driven by BUFIO, CLKDIV driven by BUFR

? CLK and CLKDIV driven by CLKOUT[0:6] of the same MMCM or PLL

When using a MMCM to drive the CLK and CLKDIV of the OSERDESE2 the buffer types

suppling the OSERDESE2 can not be mixed. For example, if CLK is driven by a BUFG,

CLKDIV must be driven by a BUFG as well.

3.6 OSERDESE2級聯

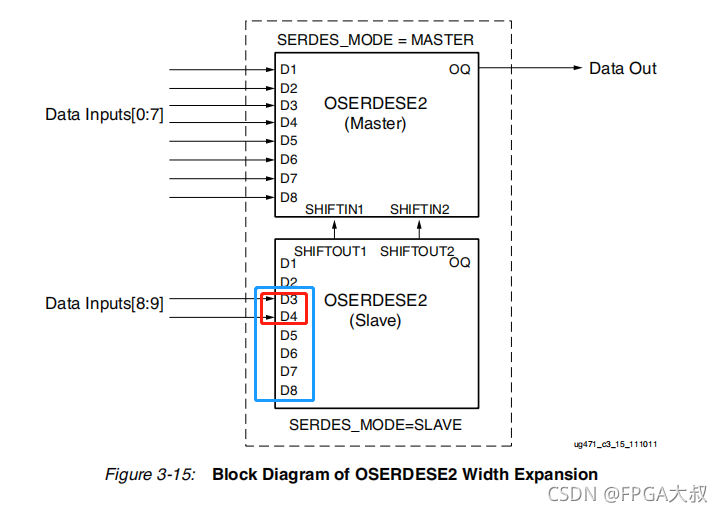

用兩個OSERDESE2模塊級聯來構造一個超過8:1的并-串轉換器。通過連接主OSERDESE2的SHIFTIN端口和從OSERDESE2的SHIFTOUT端口,轉換器可以擴展為10:1和14:1(僅DDR模式)。(注:筆者感覺有點懵,曾在項目用主的SHIFTOUT端口接到從的SHIFTIN端口 = =||)。對于差分輸出,連接_P管腳。當輸出不是差分信號時,從OSERDESE2的輸出buffer是不允許的,位寬擴展無法使用。

當使用補充的signal-ended標準時(也就是說DIFF_HSTL和DIFF_SSTL),位寬擴展可能不能使用。這是因為在I/O塊的OLOGICE2/3塊全部用作補充的signal-ended標準來傳輸這兩個補充的信號,沒有多余的OLOOGICE2/3資源可用來位寬擴展。

The OSERDESE2 modules be used to build a parallel-to-serial converter larger than 8:1. In

every I/O tile there are two OSERDESE2 modules; one master and one slave. By

connecting the SHIFTIN ports of the master OSERDESE2 to the SHIFTOUT ports of the

slave OSERDESE2, the parallel-to-serial converter can be expanded to up to 10:1 and 14:1

(DDR mode only). For a differential output, the master OSERDESE2 must be on the

positive (_P pin) side of the differential output pair. When the output is not differential, the

output buffer associated with the slave OSERDESE2 is not available and width expansion

cannot be used.

When using complementary single-ended standards (e.g., DIFF_HSTL and DIFF_SSTL),

width expansion might not be used. This is because both OLOGICE2/3 blocks in an I/O

tile are used by the complementary single-ended standards to transmit the two

complementary signals, leaving no OLOGICE2/3 blocks available for width expansion

purposes.

下圖是10:1DDR模式并-串轉換器,使用一主一從兩個OSERDESE2模塊。在這個例子中中從OSERDES端口D3-D4被用作并行數據接口的最后兩位。

注:位寬擴展時,從OSERDESE2模塊使用端口D3-D8; D1-D2不用。

3.7 OSERDESE2潛伏期

之前文章也介紹過:

Delay:延遲,延遲時間后才發生

Latency:潛伏,潛伏時間后信號才穩定

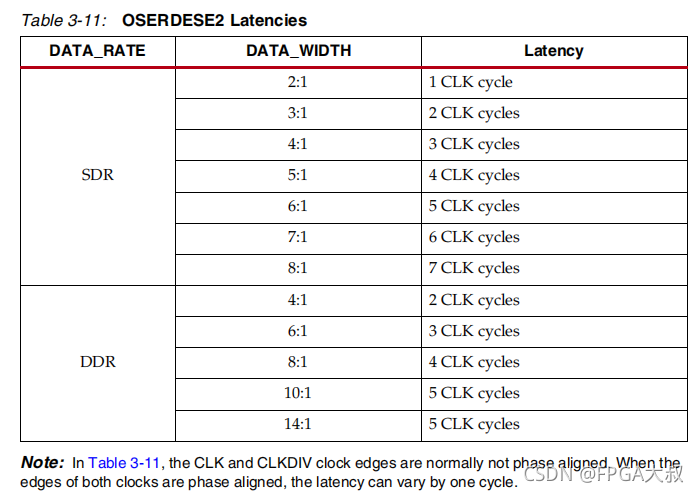

OSERDESE2塊輸入到輸出的潛伏期由DATA_RATE和DATA_WIDTH屬性決定。潛伏期被定義為事件a到事件b的一段時間:(a)當CLKDIV的上升沿,D1-D8的數據輸入到OSERDESE2,(b)當串行數據流的第一位出現在OQ。簡單解釋下:就是輸入到輸出的時間。下圖整理了不同OSERDESE2潛伏期的值。

The input to output latencies of OSERDESE2 blocks depend on the DATA_RATE and

DATA_WIDTH attributes. Latency is defined as a period of time between the following

two events: (a) when the rising edge of CLKDIV clocks the data at inputs D1–D8 into the

OSERDESE2, and (b) when the first bit of the serial stream appears at OQ. Table 3-11

summarizes the various OSERDESE2 latency values.

四、圖解OSERDES串行化數據流

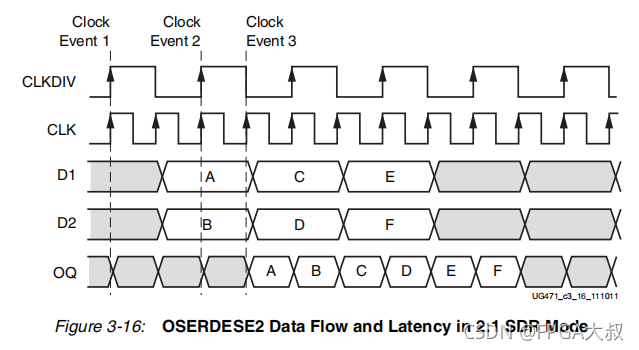

4.1 案例①SDR模式

2:1 SDR 數據串行化的時序圖:

Clock Event 1:

在CLKDIV的上升沿,由FPGA邏輯驅動的字AB給到OSERDESE2的輸入端D1和D2(經過一些傳播延遲)

Clock Event 2 :

在CLKDIV的上升沿,由D1和D2輸入的字AB被采樣到OSERDES。

Clock Event 3

在AB被采樣進入OSERDESE2后,數據A在OQ輸出一個CLK時鐘周期。這個潛伏期由3.7章節的表格查詢可知。

4.2 案例②DDR模式

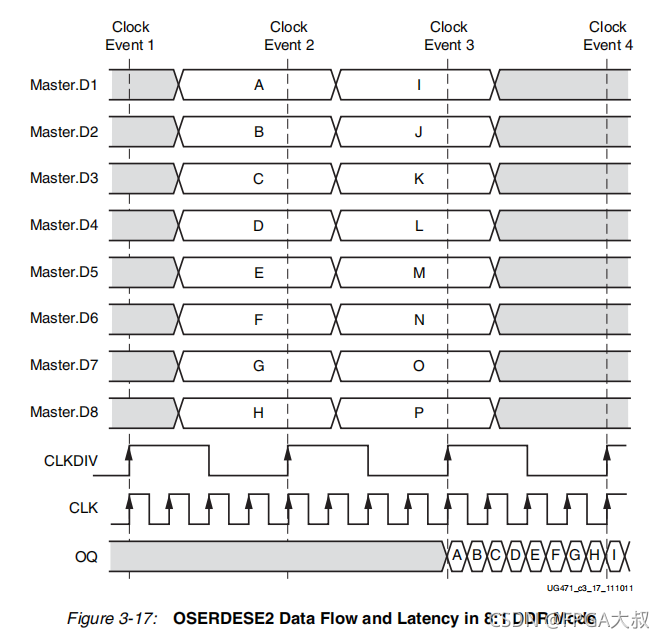

8:1 DDR數據串行化時序圖:

Clock Event 1:

在CLKDIV的時鐘上升沿,由FPGA邏輯驅動的字ABCDEFGH給到OSERDESE2的輸入管腳D1-D8。

Clock Event 2:

在CLKDIV的時鐘上升沿,D1-D8輸入的ABCDEFGH被采樣進OSERDESE2。

Clock Event 3:

在ABCDEFGH被采樣進OSERDESE2后,數據位A首先在OQ輸出4個CLK周期。這個潛伏期由3.7章節的表格查詢可知。

D1-D8輸入的第二個字 IJKLMNOP 被采樣進入 OSERDESE2 。

Clock Event 4

在Clock Events 3和4之間, ABCDEFGH整個字被連續的傳輸到OQ,,一個完整的8位傳輸在一個CLKDIV周期內完成。

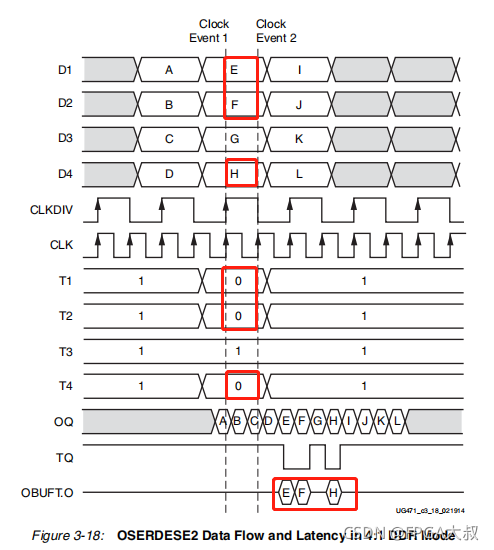

4.3 案例③3-state

The operation of a 3-state controller:

Clock Event 1

T1,T2,T4被驅動位低電平來釋放3-態條件。OSERDESE2的T1-T4和D1-D4串行化路徑是完全相同的(包括潛伏期),所以EFGH和0010在Clock Event 1是始終對齊的。

Clock Event 2

在EFGH被采樣進入OSERDESE2后,數據位E出現在OQ一個CLK周期,潛伏期可看3.7。

在0010被采樣進入OSERDESE2 3態塊后,三態輸入的0在TQ輸出一個CLK周期,潛伏期可看3.7。

看圖得知:OBUFT的輸出端O輸出EFH,對應三態輸入0釋放掉三態條件時候的D1-D4輸入,并且輸出在TQ為低時有效。(這是筆者根據上圖猜測的結論,實際上筆者還沒使用過 = =)

五、后記

最后的I/O FIFO先略過。

加上前兩篇,《UG471-SelectIO》(1-3) 基本翻譯完成。

算是小小的成就,給自己打Call~

如有錯誤,歡迎拍磚~

但是,本系列UG471文章還停留在翻譯介紹階段,下一步我會將其整理到LVDS接口的使用中進行介紹。未完待續。

審核編輯:符乾江

-

FPGA

+關注

關注

1630文章

21781瀏覽量

604936 -

Xilinx

+關注

關注

71文章

2169瀏覽量

121846

發布評論請先 登錄

相關推薦

調試Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作怎么解決?

MSP430F471x3,MSP430F471x6, MSP430F471x7混合信號微控制器數據表

IPC-6012E CN 2020中文 CN 剛性印制板的鑒定及性能規范

FPGA | Xilinx ISE14.7 LVDS應用

Xilinx ISE14.7 LVDS的應用

Xilinx SelectIO資源內部的IDELAYE2應用介紹

《Xilinx—UG471中文翻譯》(3)OSERDESE2原語介紹

《Xilinx—UG471中文翻譯》(3)OSERDESE2原語介紹

評論