所有IP核沒有正確工作,原因一半是時鐘,一半是復位。

前言

復位與初始化部分其實還挺復雜,還好GTX已經幫我們做好了,不想麻煩的直接跳到文末看結論~~~不過了解下也挺有意思的~~

同時GTX復位也挺隨意的,你想怎么復位都可以,支持整體復位,單個組件復位。我們也可以不復位,核不會因為我們沒有進行軟復位就不對核進行復位,在上電之后會自動進行一系列的復位,不隨你的意志而轉移。下面我們就來仔細研究研究GTX的復位吧!

一、復位與初始化

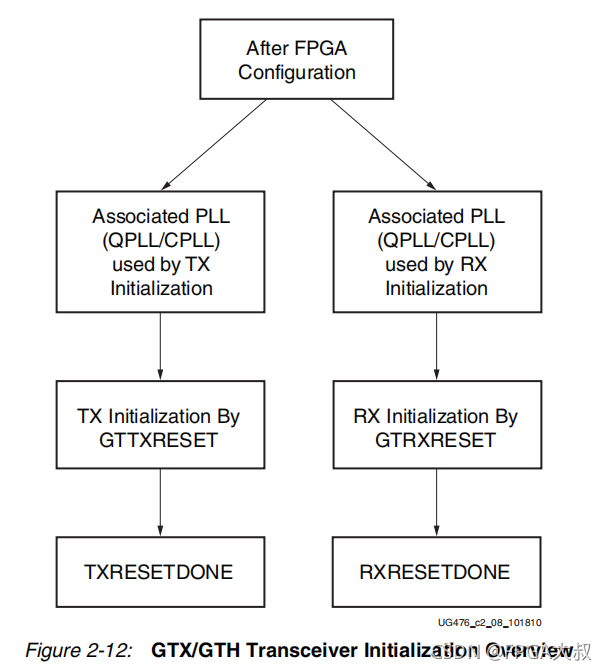

在FPGA上電配置之后,必須進行初始化才能使用GTX/GTH。(后文全用GTX表示,同樣適用于GTH)GTX的發送器(TX)和接收器(RX)可以獨立的同步進行初始化。

GTX的TX和RX初始化包含兩步:

1. 初始化相關的PLL來驅動TX/RX

2. 初始化TX和RX的數據路徑(PMA+PCS)

GTX的TX和RX能從QPLL或者CPLL接收一個時鐘。所以在TX/RX初始化之前必須對相關的PLL(QPLL/CPLL)進行初始化。TX/RX使用的任何PLL都是單獨的進行復位,PLL復位操作與TX/RX復位完全獨立。TX/RX的數據路徑復位必須在相關的PLL復位完成,locked之后進行。(就跟我們使用PLL IP核一樣,等locked拉高之后,時鐘穩定才能使用)

看圖說話:TX/RX是獨立的并行的進行復位操作。

GTX的TX和RX使用一個狀態機來控制初始化過程,并被劃分為幾塊來分別復位。該劃分允許復位狀態機按順序控制復位過程:PMA可以首先被復位,PCS可以在TXUSERRDY或者 RXUSERRDY信號被斷言后進行復位。在需要的時候,它也同樣允許PMS,PCS,他們內部的功能模塊獨立的進行復位。

GTX提供了兩種復位類型: initialization 和 component。

? Initialization Reset: 初始化復位。這種復位用作GTX完全復位。必須在設備上電及配置完成之后。在必要的時候,TX端口和RX端口的復位(GTTXRESET 和 GTRXRESET)同樣可被用來重新初始化GTX的TX和RX。

? Component Reset: 模塊復位。對TX / RX 單獨部分進行復位。 TX模塊復位端口包括TXPMARESET 和TXPCSRESET 。RX 模塊復位端口包含RXPMARESET,RXDFELPMRESET,EYESCANRESET, RXPCSRESET, RXBUFRESET和 RXOOBRESET。(有木有很多很復雜。。)

注:

1. 所有的復位高電平有效。

2. 這些復位都是異步的。對這些異步復位的推薦設計是一個(各自時鐘域)時鐘周期的脈沖信號。

3. 復位端口不應該被用做下電的目的。

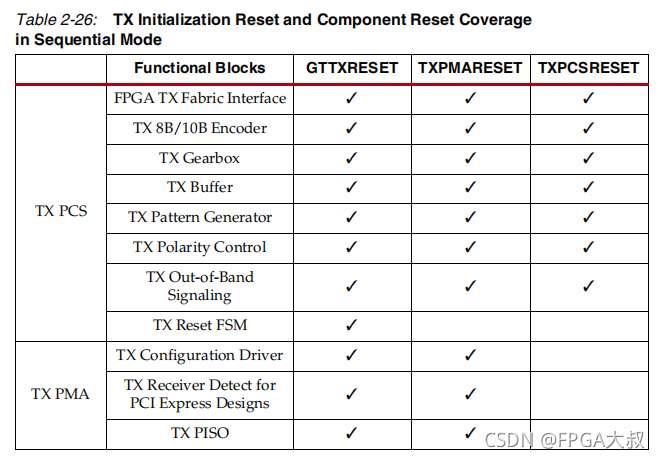

兩種復位類型主要有以下不同:

TX部分:

RX部分:

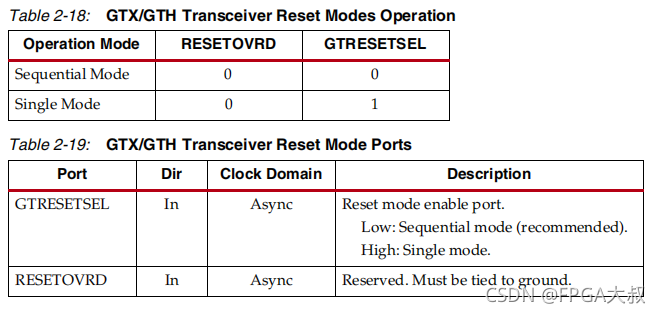

二、復位模式

GTX的初始化復位 (initialization reset) 只能使用順序復位模式(Sequential mode )。

GTX的TX復位只能使用順序復位模式(Sequential mode )。

GTX的RX復位可以使用兩種復位模式:

Sequential mode :順序復位。隨復位狀態機(initialization 或 component)順序復位各個部分。

Single mode :單獨復位。僅復位單個部分(PMA、PCS、內部功能塊)。

復位完成由信號(TX/RX)RESETDONE表示,由低到高。

復位模式對CPLL和QPLL沒有任何影響。GTX也可以被軟件進行彈性復位設置,不管是哪種模式。

使用GTRESETSEL來選擇復位模式,RESETOVRD必須驅動為低電平。詳細見下表:

注:復位前,GTRESETSEL和RESETOVRD需要300-500ns的有效時間。

三、CPLL復位

在相關時鐘邊沿信號被檢測到之前,CPLL必須使用CPLLPD端口來下電。在CPLLPD被釋放后,CPLL在使用之前必須進行復位。每個GTX通道都有3個專用端口用來CPLL復位。如下圖:

CPLLRESET :CPLL的復位輸入。推薦設計是一個時鐘周期。

CPLLLOCK :拉高時,表示CPLL的復位完成。

內部CPLL復位信號:低有效。但是由GTX內部電路產生的真正的CPLL復位必須比CPLLRESET高脈沖時間要長。這個時間跟帶寬、時鐘頻率等有關。

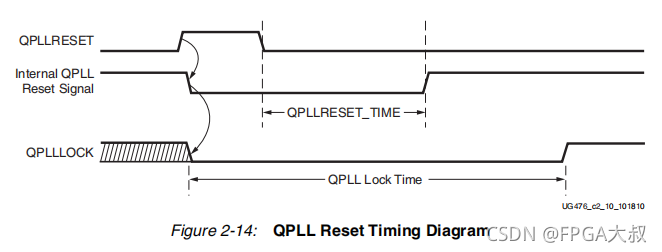

四、QPLL復位

QPLL復位大致與CPLL相同。放張圖:

五、GTX TX初始化與復位

開門見山的說:GTX的TX復位只能使用順序復位模式(Sequential mode )。

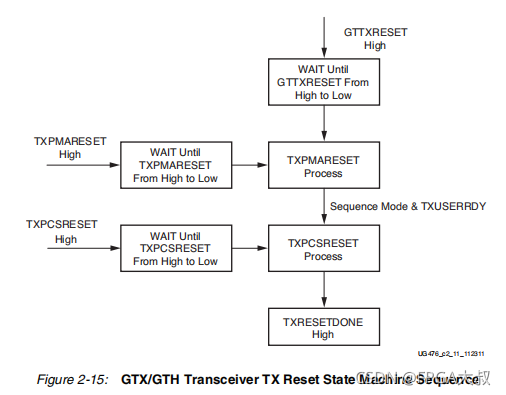

GTX的TX使用一個復位狀態機來控制復位過程。TX復位分為兩部分:TX PMA和TX PCS。

回憶下(1)GTX基本知識所介紹的:GTX的TX和RX均有PMA+PCS兩個子層組成。

在整個PMA和PCS中,都由這個復位狀態機按順序執行復位。如下圖:

使用TXPMARESET來對TX進行復位,TXRESETDONE拉高表示復位完成。

直到TXUSERRDY被檢測為高時,TX復位狀態機才對PCS進行復位。但是,驅動TXUSERRDY為高需滿足以下條件:

1. 所有應用到的時鐘包括TXUSRCLK/TXUSRCLK2必須穩定,或者locked(在PLL/MMCM被使用的時候)

2. 用戶接口已經準備好傳輸數據到GTX。

5.1 GTX TX復位和初始化的端口信號

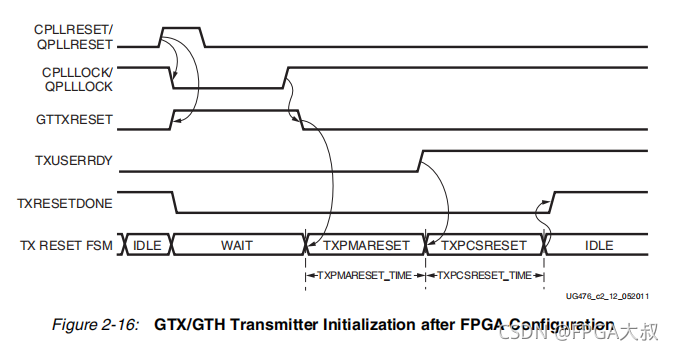

5.2 GTX TX復位對配置完成的響應

TX復位必須滿足下列條件:

1. 使用順序復位模式,GTRESETSEL必須為低。.

2. GTTXRESET必須使用。

3. 在復位完成前(TXRESETDONE拉高),TXPMARESET和TXPCSRESET 必須驅動為低不變。

4. 在PLL locked之前,GTTXRESET不能被驅動為低。

如果加載配置時,復位模式默認為順序復位模式,在配置加載后等待最少500ns,C/QPLLRESET 和GTTXRESET 就可以被斷言了。

如果復位模式為single mode,用戶必須:

1. 在配置加載完成后,等待最少500ns。

2. 將復位模式改為順序復位模式 Sequential mode。

3. 再等待300-500ns。

4. 斷言 C/QPLLRESET和 GTTXRESET。

推薦的設計是使用來自相關的CPLL或者QPLL的PLLLOCK 來釋放GTTXRESET由高到低。

TX復位狀態機等GTTXRESET拉高,開始TX復位,直到GTTXRESET被釋放低為止。

如下圖所示:

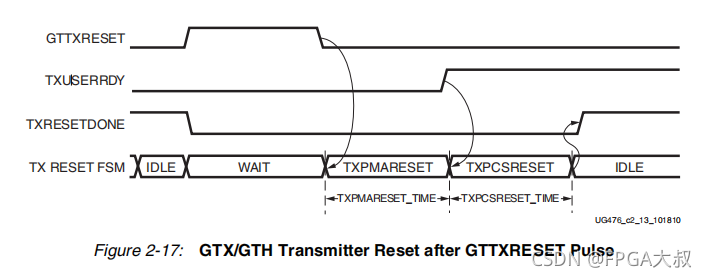

5.3 GTX TX復位對GTTXRESET脈沖的響應

GTX允許用戶在任意時刻對TX進行復位,只需要給GTTXRESET一個有效的高脈沖信號。 TXPMARESET_TIME和 TXPCSRESET_TIME 可以被設置為靜態的也可以通過DRP端口來動態設置以適配在申請 GTTXRESET之前要求的復位時間。

當使用GTTXRESET時必須滿足以下條件:

1. 使用sequential mode必須將GTRESETSEL置低。

2. 在復位完成之前,TXPMARESET 和 TXPCSRESET 必須一直為低。

3. 相關 PLL必須 locked。

4. GTTXRESET的推薦設計是一個時鐘周期脈沖。

5.4 GTX TX 模塊復位

TX PMA和 TX PCS 可以單獨進行復位。在 TXPMARESET 或者 TXPCSRESE復位過程完成之前,TGTTXRESET必須保持為低。驅動TXPMARESET從高到低來啟動PMA復位程序, 在TXPMARESET復位過程中,TXPCSRESET必須保持為低。

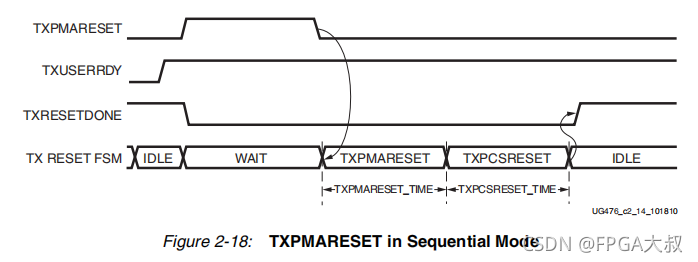

在順序復位模式,復位狀態機在PMA復位完成后,(如果TXUSERRDY為高)自動開始PCS復位。如下圖:

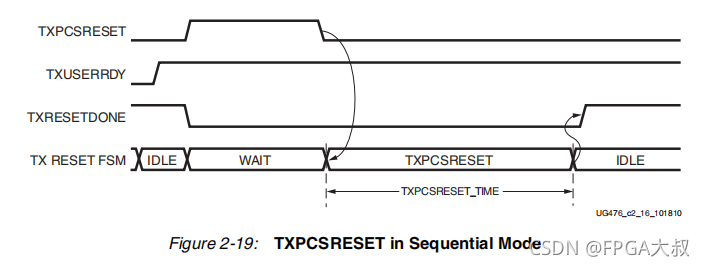

當TXUSERRDY為高時,驅動TXPCSRESET由高到低來啟動PCS復位程序。在PCS復位過程中,TXPMARESET 必須保持為低。

在順序復位模式,復位狀態機僅復位PCS,如下圖:

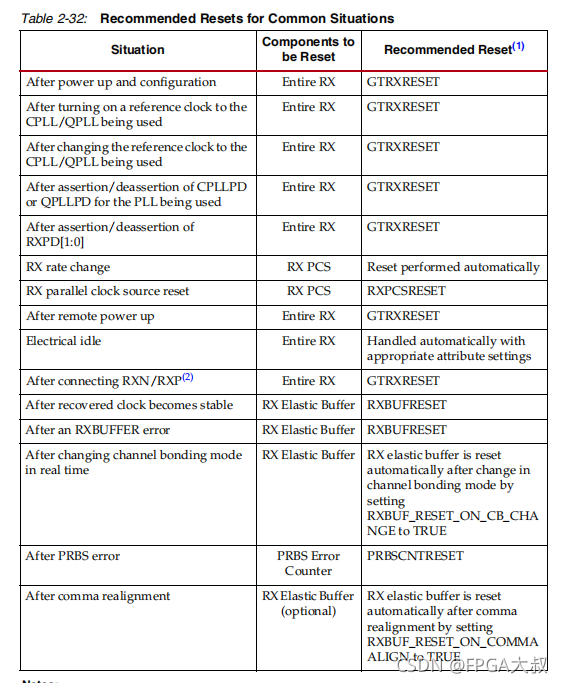

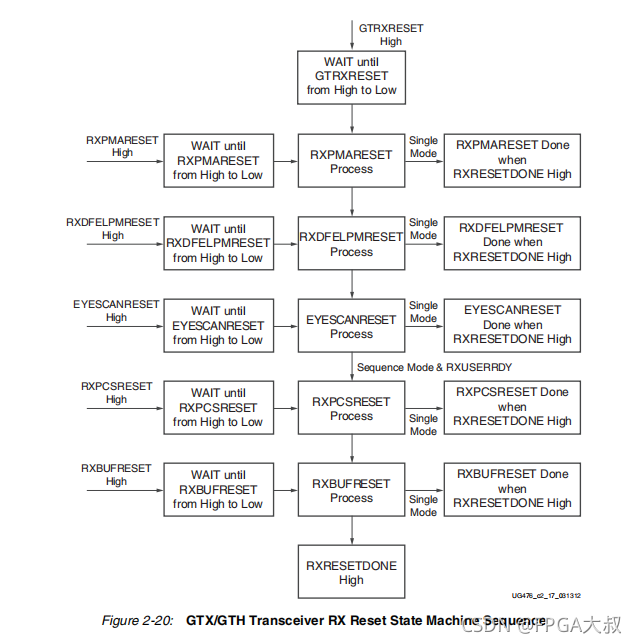

六、RX復位與初始化

已經快11點了,累了,溜了溜了,,,放張圖:

結論

由GTX核分別輸出了發送端TX和接收端RX的初始化完成信號:

TX: gt0_tx_fsm_reset_done_out(output)

RX: gt0_rx_fsm_reset_done_out(output)

直接使用這兩個信號就好,TX復位完成就可以開始發送數據,RX復位就可以接收數據。

也可以加個信號 GT_RESET_DONE;

assign GT_RESET_DONE = gt0_tx_fsm_reset_done_out && gt0_rx_fsm_reset_done_out;

先用起來,后面再深入研究,不過了解了復位過程發現還是有點意思~

OK,前面說了一大堆結論卻還是很簡單的~

拿去搬磚吧~

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21781瀏覽量

604936 -

數據

+關注

關注

8文章

7118瀏覽量

89342 -

Xilinx

+關注

關注

71文章

2169瀏覽量

121846

發布評論請先 登錄

相關推薦

【米爾-Xilinx XC7A100T FPGA開發板試用】Key-test

Verilog 測試平臺設計方法 Verilog FPGA開發指南

基于Xilinx ZYNQ7000 FPGA嵌入式開發實戰指南

采用Xilinx FPGA的AFE79xx SPI啟動指南

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

FPGA | Xilinx ISE14.7 LVDS應用

FPGA核心板 Xilinx Artix-7系列XC7A100T開發平臺,米爾FPGA工業開發板

想通過CYUSB3014配置xilinx FPGA,如何下載CYUSB3014的FPGA配置實用程序工具?

Xilinx 7系列FPGA功能特性介紹

適用于 Xilinx? MPSoC 和 FPGA的可配置多軌PMU TPS650864數據表

Xilinx fpga芯片系列有哪些

適用于 Xilinx? MPSoC 和 FPGA 的可配置多軌PMU TPS650864數據表

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx FPGA平臺GTX簡易使用教程(三)

Xilinx FPGA平臺GTX簡易使用教程(三)

評論