多看一些example design之后,你就會發現都是熟悉的配方。

一、Example Design

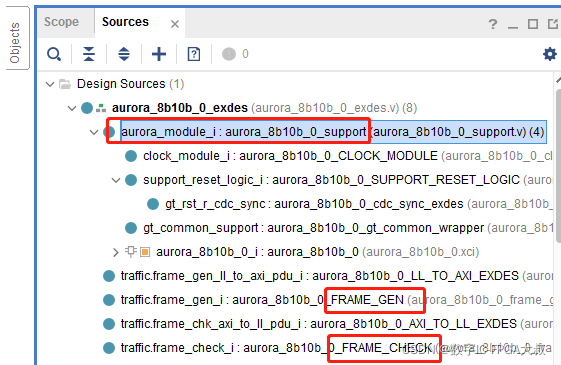

首先打開example design,看看示例工程架構:

多看一些xilinx的example design之后,你就會發現都是熟悉的配方:

support是核心模塊,包含了IP的例化、時鐘及復位邏輯;重點理解。

frame_gen 是數據產生模塊;

frame_check是數據接收檢查模塊;

support.v

support是核心模塊,包含了IP的例化、時鐘及復位邏輯;時鐘和復位在前面文章已經介紹過了,就不再啰嗦;先看下support對外的端口信號:

module aurora_8b10b_0_support

(

// AXI TX Interface

input [15:0] s_axi_tx_tdata,

input [1:0] s_axi_tx_tkeep,

input s_axi_tx_tvalid,

input s_axi_tx_tlast,

output s_axi_tx_tready,

// AXI RX Interface

output [15:0] m_axi_rx_tdata,

output [1:0] m_axi_rx_tkeep,

output m_axi_rx_tvalid,

output m_axi_rx_tlast,

// GT Serial I/O

input rxp,

input rxn,

output txp,

output txn,

// GT Reference Clock Interface

input gt_refclk1_p,

input gt_refclk1_n,

// Error Detection Interface

output frame_err,

output hard_err,

output soft_err,

// Status

output lane_up,

output channel_up,

// System Interface

output user_clk_out,

input gt_reset,

input reset,

input power_down,

input [2:0] loopback,

output tx_lock,

input init_clk_p,

input init_clk_n,

output init_clk_out,

output tx_resetdone_out,

output rx_resetdone_out,

output link_reset_out,

output sys_reset_out,

//DRP Ports

input drpclk_in,

input [8:0] drpaddr_in,

input drpen_in,

input [15:0] drpdi_in,

output drprdy_out,

output [15:0] drpdo_out,

input drpwe_in,

output pll_not_locked_out

);

首先是framing接口的發送及接收的端口信號,與上一篇我們介紹的一致;我們使用Aurora IP,無非就是將需要發送的數據放到s_axi_tx_tdata數據總線上,從m_axi_rx_tdata數據總線上接收數據。有了這點認知后,理解就簡單多了。接著是GT串行I/O,對應物理管腳。接著就是狀態信號channel_up,channel_up信號拉高,表明鏈路建立成功可以進行正常數據收發。然后是一些時鐘和復位信號,最后是DRP動態重配置的相關信號。

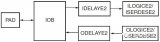

繼續看support對Aurora 8b/10b的例化:

aurora_8b10b_0 aurora_8b10b_0_i

(

// AXI TX Interface

.s_axi_tx_tdata (s_axi_tx_tdata),

.s_axi_tx_tkeep (s_axi_tx_tkeep),

.s_axi_tx_tvalid (s_axi_tx_tvalid),

.s_axi_tx_tlast (s_axi_tx_tlast),

.s_axi_tx_tready (s_axi_tx_tready),

// AXI RX Interface

.m_axi_rx_tdata (m_axi_rx_tdata),

.m_axi_rx_tkeep (m_axi_rx_tkeep),

.m_axi_rx_tvalid (m_axi_rx_tvalid),

.m_axi_rx_tlast (m_axi_rx_tlast),

// GT Serial I/O

.rxp (rxp),

.rxn (rxn),

.txp (txp),

.txn (txn),

// GT Reference Clock Interface

.gt_refclk1 (gt_refclk1),

// Error Detection Interface

.frame_err (frame_err),

// Error Detection Interface

.hard_err (hard_err),

.soft_err (soft_err),

// Status

.channel_up (channel_up),

.lane_up (lane_up),

// System Interface

.user_clk (user_clk_i),

.sync_clk (sync_clk_i),

.reset (system_reset_i),

.power_down (power_down),

.loopback (loopback),

.gt_reset (gt_reset_i),

.tx_lock (tx_lock_i),

.init_clk_in (init_clk_i),

.pll_not_locked (pll_not_locked_i),

.tx_resetdone_out (tx_resetdone_i),

.rx_resetdone_out (rx_resetdone_i),

.link_reset_out (link_reset_i),

.drpclk_in (drpclk_i),

.drpaddr_in (drpaddr_in),

.drpen_in (drpen_in),

.drpdi_in (drpdi_in),

.drprdy_out (drprdy_out),

.drpdo_out (drpdo_out),

.drpwe_in (drpwe_in),

//_________________COMMON PORTS _______________________________

// ------------------------- Common Block - QPLL Ports ------------------

.gt0_qplllock_in (gt0_qplllock_i),

.gt0_qpllrefclklost_in (gt0_qpllrefclklost_i),

.gt0_qpllreset_out (gt0_qpllreset_i),

.gt_qpllclk_quad1_in (gt_qpllclk_quad1_i ),

.gt_qpllrefclk_quad1_in (gt_qpllrefclk_quad1_i ),

.sys_reset_out (sys_reset_out),

.tx_out_clk (tx_out_clk_i)

);

啊這,突然覺得官方例程的注釋已經很清楚了,再羅里吧嗦的介紹有點煩。

真不是筆者偷懶~ = =||

個人建議,把時鐘復位理清楚,再按照framing接口時序,來設計數據的收發。基本上就能使用Aurora搬磚了。

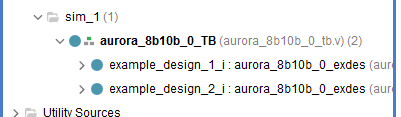

二、仿真

直接看仿真,清晰明了。

可以看到,還是熟悉的配方,仿真頂層還是例化了兩個example實體,然后在TB頂層對其進行環回連接:

assign rxn_1_i = txn_2_i;

assign rxp_1_i = txp_2_i;

assign rxn_2_i = txn_1_i;

assign rxp_2_i = txp_1_i;

也就是說,Aurora-2的發送管腳接到了Aurora-1的接收管腳,那么Aurora-2發送的數據必然與Aurora-1接收到的數據是相等的;我們打開仿真,驗證一下。

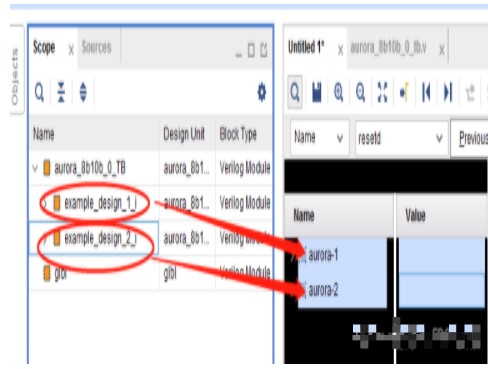

首先把相關信號拖到仿真,并設置group,便于歸類查看:

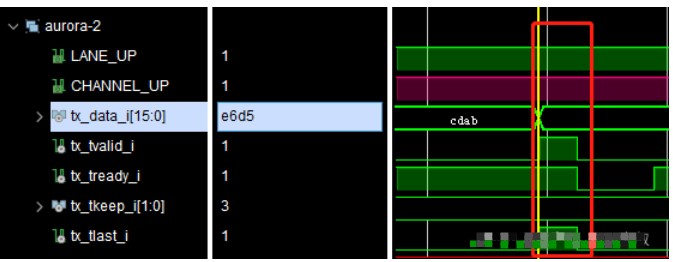

根據推論,先看Aurora-2發送的第一個數據:

如圖所示:

tx_data = 16’he6d5; 只有一個數據,占了一個時鐘周期(user_clk時鐘域),所以tlast與tvalid都只是同時拉高了一個時鐘周期。同時,tkeep = 2’h3;表明這個數據所有字節都是有效的。另外注意,數據是在valid和ready握手(同時有效)時發送的。

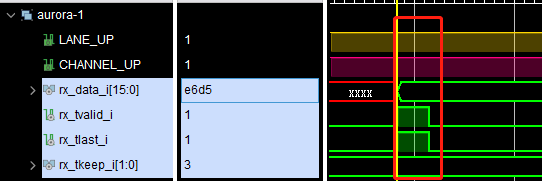

再看Aurora-1接收的第一個數據:

如圖所示:

當rx_tvalid有效時,rx_data = 16’he6d5;同時,tlast信號為1,表明這一次數據傳輸的接收完畢。rx_tkeep = 2’h3,表明數據全部字節有效。

通過對比可知,接收數據等于發送數據。驗證成功。

接下來可以繼續驗證Aurora-2發送的第二個數據與Aurora-1接收的第一個數據;也可以驗證Aurora-1發送的數據與Aurora-2接收的數據。這里就不再啰嗦了。

下一篇,我們基于Aurora IP完成自己的數據收發。

審核編輯:湯梓紅

-

AURORA

+關注

關注

0文章

25瀏覽量

5397

發布評論請先 登錄

相關推薦

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

如何在ModelSim中添加Xilinx仿真庫

介紹MCUboot支持的四種升級模式(2)

Xilinx SelectIO資源內部的IDELAYE2應用介紹

Xilinx 7系列FPGA功能特性介紹

SC171開發套件V1 硬件平臺介紹及使用

Xilinx FPGA NVMe主機控制器IP,高性能版本介紹應用

國產計算機平臺介紹(四)——飛騰

Xilinx平臺Aurora IP介紹(四)Example Design介紹

Xilinx平臺Aurora IP介紹(四)Example Design介紹

評論