一、Aurora配置

開門見山的說,跟DDR/PCIE/GTX這種復雜的IP相比,Aurora配置那是相當的簡單。走著。

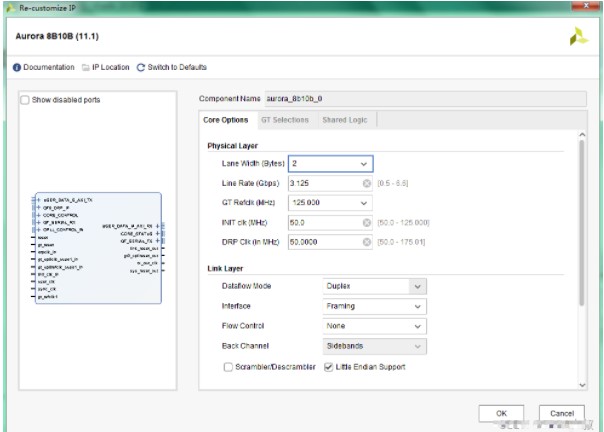

1.1第一頁配置

物理層Physical Layer:

Lane Width : 鏈路位寬,對應用戶數據位寬;實際用戶數據位寬= Lane Width*Lane的個數(也就是第二頁的Lanes)

Lane Rate : 鏈路數據傳輸速率,Gbps。我們測試默認3.125G就好。

下面三個時鐘在上一篇《時鐘和復位》說過,就不再啰嗦了。

鏈路層Link Layer:

dataflow mode: 數據流模式,可選全雙工/ 只接收/ 只發送;根據實際情況選擇,為了測試,我們這里選擇全雙工。

interface:Framing/streaming可選。streaming較簡單,大家可以自行去驗證。一般使用framing接口,可能是axi4-s接口更方便連接吧。后續介紹都基于Framing接口。

flow control:流控,暫時不選擇。

back channel:sidebands/timer 可選,(只有在單工模式才能選擇);秋大佬告知這個什么意思,我沒用過,先略過。

Scrambler/Descrambler :繞碼/解繞,這里不選擇

little endian support :小端模式,勾選上就對了。小端模式在不同場合一般有兩層意思:①[31:0]這種書寫習慣,對應的是[0:31];②假設你的數據是64位,鏈路寬度是32位,那么一次只能傳輸32bit,先傳輸高32bit為大端模式,先傳輸低32bit為小端模式。

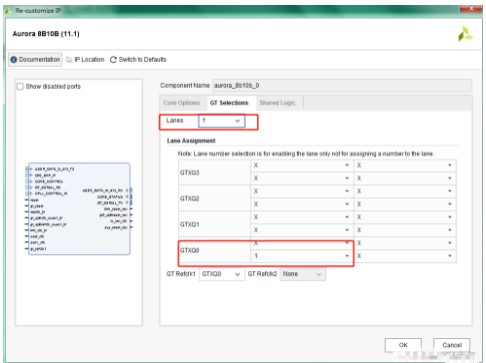

1.2第二頁配置

第二頁配置主要是對GT的選擇。

包括:使用幾個GTX,GTX的位置等。根據實際選擇,這里做測試默認就好。

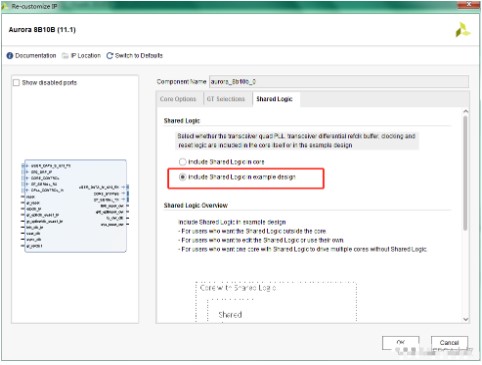

1.3第三頁配置

為了學習以及使用的靈活性,我們一般選擇將共享邏輯放在example design而不是放入core。

配置部分就介紹完了,使用還是很簡單的。再次感謝xilinx!

前面說過,Aurora core支持兩種接口模式:framing 和 streaming。

streaming較簡單,framing 較通用。

下面我們一起來看下這兩種接口。

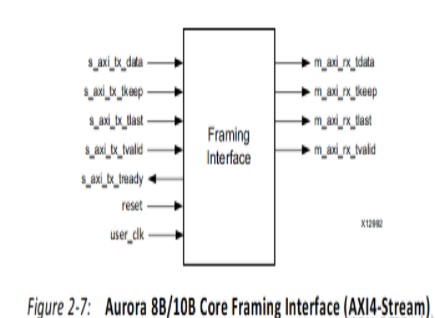

二、Framing接口

2.1 接口信號

發送端:

接收端:

Tips: 其實,在理解了AXI4總線(AXI4-FULL/LITE/STREAM)后,再來看這些信號名,都不需要看文檔你就能知道它的意思了。所以,強烈建議把AXI4總線接口先去熟悉一遍。空了,我也將AXI4總線簡單整理一下。

2.2理論介紹

傳輸數據時,用戶邏輯需要操縱控制信號讓core做以下操作:

1. 當s_axi_tx_tvalid和s_axi_tx_tready都斷言時,將需要發送的數據放到數據總線s_axi_tx_tdata。簡單來說就是_tvalid和_tready每握手一次,完成一個數據傳輸。

2. 把數據劃分到Aurora 8B/10B channel的各條lane。

3. 使用 s_axi_tx_tvalid 信號來傳輸數據,用戶應用程序可以將_valid信號置為無效來插入空閑字符idles。(用來暫停或停頓。)

4. 暫停數據(即插入空閑)(s_axi_tx_tvalid置為無效)

接收數據:

1. 檢測并丟棄控制字節(空閑,時鐘補償,通道PDU(SCP)的開始,通道協議數據單元(ECPDU)的結束和PAD。

2. 置位成幀信號(m_axi_rx_tlast),并指定最后一個數據(m_axi_rx_tkeep)中的有效字節數。

3. 從通道中恢復數據。

4. 通過斷言m_axi_rx_tvalid信號來組裝數據,以呈現給m_axi_rx_tdata總線上的用戶接口。

注意:

僅當同時聲明s_axi_tx_tready和s_axi_tx_tvalid(高)時,Aurora 8B / 10B內核才對數據采樣。

AXI4-Stream數據僅在幀內時才有效。 幀外的數據將被忽略。 要開始幀,在數據的第一個字位于s_axi_tx_tdata總線上時拉高s_axi_tx_tvalid。 要結束幀,在數據的最后一個字(或部分字)位于s_axi_tx_tdata端口上時拉高s_axi_tx_tlast,并使用s_axi_tx_tkeep指定最后一個數據拍中的有效字節數。

如果幀的長度不超過一個字,則同時使s_axi_tx_tvalid和s_axi_tx_tlast有效。

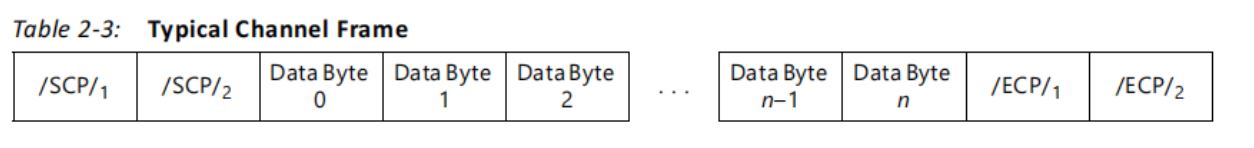

Aurora 8B/10B Frames 幀結構

TX子模塊通過TX接口將每個接收到的用戶幀轉換為Aurora 8B / 10B幀。 通過在幀的開頭添加一個2字節的SCP代碼組來指示幀的開始(SOF)。 幀的結尾(EOF)通過在幀的末尾添加2字節的通道結束協議(ECP)代碼組來表示。 只要沒有數據,就會插入空閑代碼組。代碼組是8B / 10B編碼的字節對,所有數據都作為代碼組發送,因此具有奇數字節的用戶幀在幀末尾附加了一個稱為PAD的控制字符,以填充最終的代碼組。

Length

用戶應用程序通過操縱s_axi_tx_tvalid和s_axi_tx_tlast信號來控制通道幀長度。 Aurora 8B / 10B核分別響應幀開始和幀結束有序集/ SCP /和/ ECP /。

以上基本是對文檔的翻譯,結合實際使用來看,幀頭幀尾部分由核幫你做了。我們只需要將有效數據負載放在s_axi_tx_tdata總線上,通過s_axi_tx_tvalid和s_axi_tx_tlast握手來進行數據傳輸就好。接收,根據m_axi_rx_tvalid標志來接收有效數據就好。

2.3 接口時序圖

接下來,我們再看3個數據發送的例子:

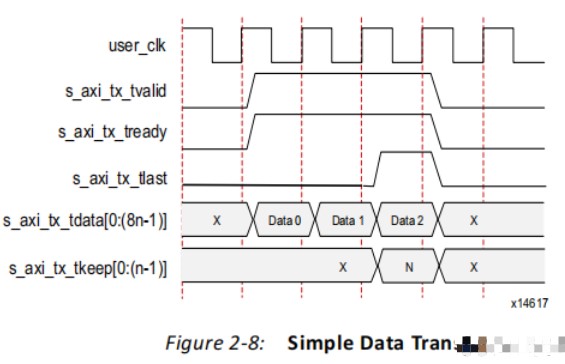

CASE1 : 簡單數據傳輸

如圖所示:在s_axi_tx_tvalid和s_axi_tx_tlast同時有效(握手)時,s_axi_tx_tdata總線上的數據傳給了Aurora core,再由core發送出去;s_axi_tx_tlast標志著最后一個數據傳輸;s_axi_tx_tkeep標志著最后一個數據哪些字節是有效的。

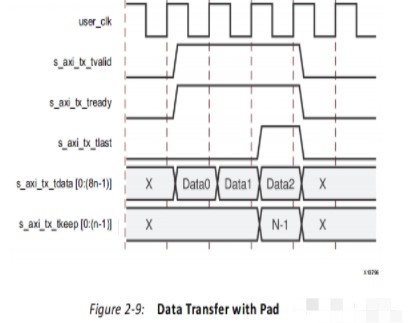

CASE2 : 數據傳輸with pad(具有奇數字節)

跟case1唯一不同的是,在最后一個數據傳輸時,由于數據是奇數字節,所以存在無效字節,由tkeep信號來標志有效字節。

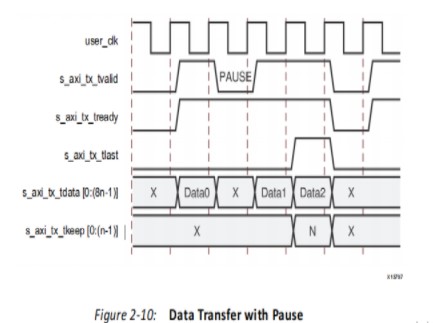

CASE3 : 有中斷的數據傳輸

看圖就是了,反正記住一點,在ready/valid握手時,才發生有效數據傳輸。

如果我們想要暫停數據傳輸,那么只需要將tvalid信號置為無效,就可以插入空閑字符,其實也就達到了流控的效果。

三、Streaming接口

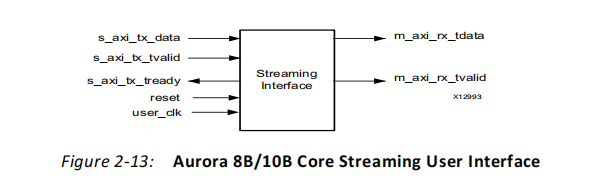

3.1 接口信號

對比framing接口是不是簡單很多。

發送:

數據總線s_axi_tx_tdata , 數據有效信號s_axi_tx_tvalid;用戶邏輯只需要設計這兩個信號就好。同樣的,數據傳輸發生在s_axi_tx_tvalid和s_axi_tx_tready同時有效(握手)時。

接收:

在m_axi_rx_tvalid信號有效時,接收m_axi_rx_tdata數據總線上的數據。

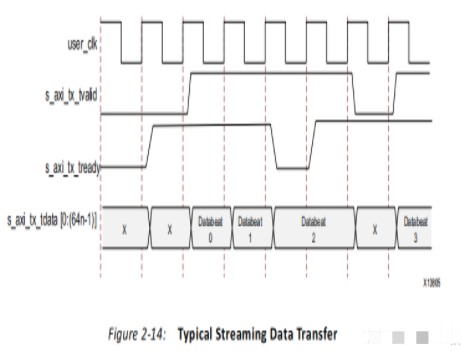

3.3接口時序圖

發送:

如下圖所示:數據有效傳輸發生在s_axi_tx_tvalid和s_axi_tx_tready同時有效(握手)時。

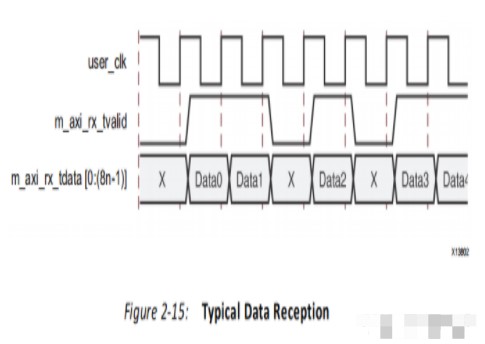

接收:

在m_axi_rx_tvalid信號有效時,接收m_axi_rx_tdata數據總線上的數據。如果來不及使用,必須使用buffer先緩存下來,否則數據丟失。

streaming接口較為簡單,就不再啰嗦了。后文介紹基于framing接口。

OK,IP配置完了,下一篇我們介紹example design!

審核編輯:湯梓紅

-

接口

+關注

關注

33文章

8682瀏覽量

151606 -

Xilinx

+關注

關注

71文章

2169瀏覽量

121846

發布評論請先 登錄

相關推薦

豐田、Aurora及大陸集團攜手NVIDIA,共推高度自動駕駛車型

豐田、Aurora和大陸集團加入NVIDIA合作伙伴行列

思嵐科技SLAMTEC Aurora在智能割草機器人中的應用

Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx DDS IP核的使用和參數配置

Xilinx平臺Aurora IP介紹(三)Aurora配置及接口

Xilinx平臺Aurora IP介紹(三)Aurora配置及接口

評論